GaN-Leistungselektronik von Innoscience

Bewährte Zuverlässigkeit zum wettbewerbsfähigen Preis

Zu teuer, zu unzuverlässig – mit diesen beiden Vorurteilen zum Einsatz von GaN-Leistungshalbleitern räumt Dr. Denis Marcon, General Manager bei Innoscience Europe, auf. Preislich ist GaN wettbewerbsfähig mit Silizium-Produkten, und bei richtiger Implementierung ist es auch sehr zuverlässig.

Boom des GaN-Marktes! Wie die Analysten von Yole in ihren neuesten Untersuchungen prognostizieren, erwarten sie für GaN zwischen 2022 und 2028 ein durchschnittliches jährliches Wachstum (CAGR) von 49 Prozent. Über die Zahlen kann man zwar streiten, aber es ist offensichtlich, dass viele Unternehmen das Potenzial von GaN, kleinere Systeme mit höherer Leistungsdichte und höherer Effizienz bereitzustellen, erkannt haben.

GaN wird auch als »grüne« Lösung angesehen, die vermarktet werden kann. Amazon bietet zum Beispiel GaN-betriebene Ladegeräte unter dem Slogan »go greener« an. Bis heute hat Innoscience mehr als 300 Mio. GaN-Chips für verschiedene Anwendungen wie Ladegeräte, Rechenzentren und Lidar-Systeme ausgeliefert. Innoscience ist das einzige Unternehmen, dessen GaN-ICs in Smartphones eingesetzt werden. Doch trotz dieses Erfolgs zögern einige Entwickler noch damit, auf GaN umzusteigen. Ihre Begründung, zwei weit verbreitete Irrtümer – der Preis und die Zuverlässigkeit –, sollen in diesem Beitrag entkräftet werden.

GaN-ICs sollen zwei- oder dreimal teurer sein wie Silizium-Bauelemente. Bild 1 zeigt jedoch einen Preisvergleich von 650-V-InnoGaN-HEMTs von Innoscience mit Si-Superjunction-Bauelementen bei ähnlichen Spannungen und Strömen, deren Preise auf den Websites der Distributoren veröffentlicht wurde. In der Grafik ist zu sehen, dass InnoGaN für jeden gegebenen Durchlasswiderstand (RDS(on)) preislich mit Si-Bauelementen vergleichbar ist. Da GaN noch eine junge Technologie ist, besteht noch viel Raum für weitere Verbesserungen – sowohl bei der Leistungsfähigkeit als auch bei der Kostenreduzierung. Letztere ist für unsere Argumentation entscheidend.

Jobangebote+ passend zum Thema

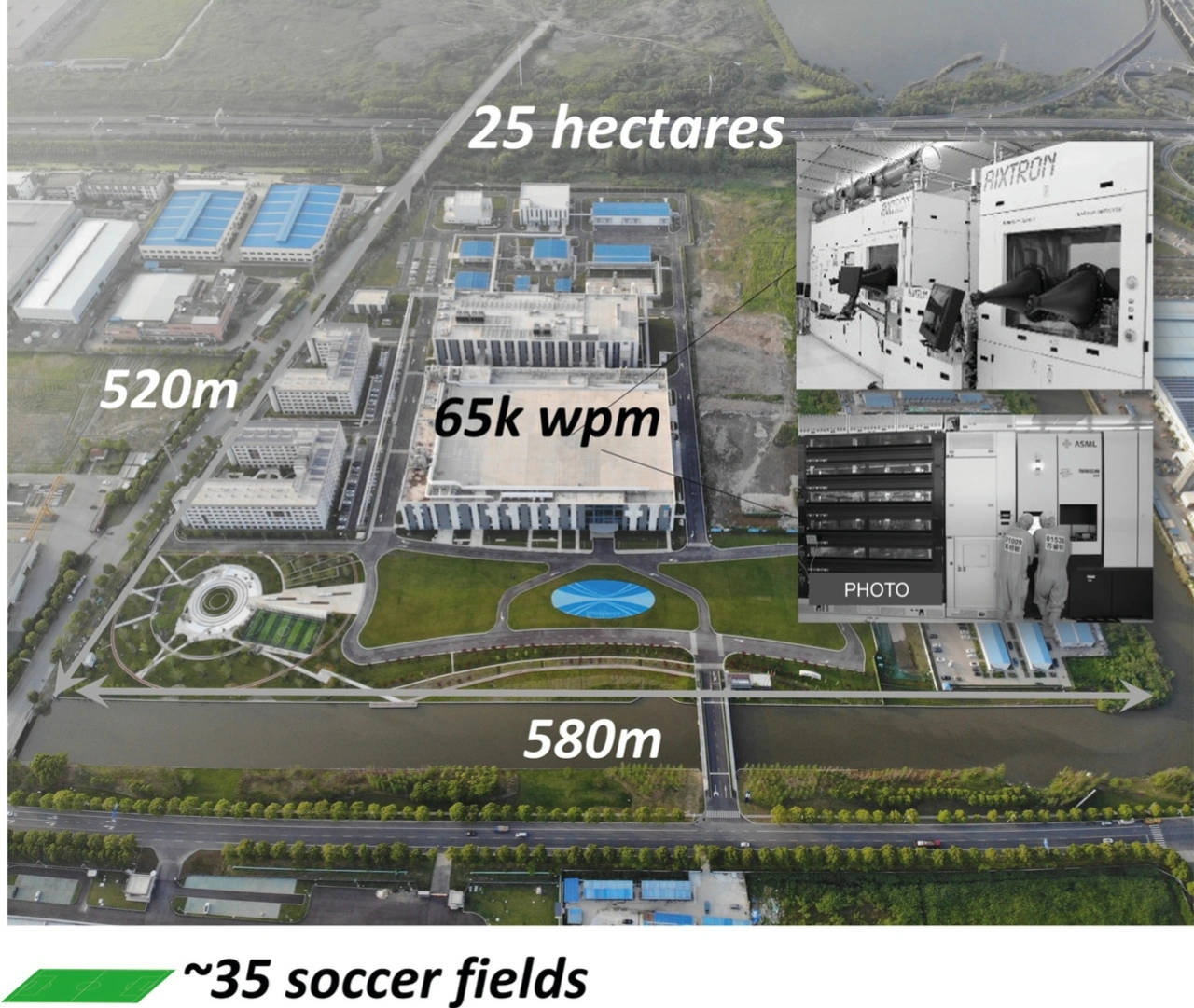

Dieser Preisvergleich wurde mit ICs durchgeführt, die von Innoscience gefertigt und verkauft werden. Wie wurde dies erreicht? Erstens verfolgt Innoscience ein IDM-Modell (Integrated Device-Manufacturer) mit zwei großen und speziellen 8-Zoll-Fabriken. Damit lassen sich Skaleneffekte nutzen. Bild 2 zeigt eine Anlage des Unternehmens in Suzhou, die sich über eine Fläche von 25 Hektar (35 Fußballfelder) erstreckt und in der 70.000 Wafer pro Monat gefertigt werden können. Dort setzt das Unternehmen die gleichen Fertigungsverfahren mit hohem Durchsatz ein, die über viele Jahre hinweg für die Si-Verarbeitung verfeinert und optimiert wurden.

Daher hat Innoscience laut einem Yole-Bericht im vergangenen Jahr bereits 10.000 8-Zoll-Wafer pro Monat hergestellt – viel mehr als andere Anbieter. Kern des IDM-Modell ist es, dass Innoscience alle kritischen Fertigungsprozesse im Haus behält, was die Entwicklungszeit verkürzt und die eigentliche Bauteiltechnologie verbessert. Im Vergleich dazu sind Fabless-GaN-Anbieter, die nicht alle Prozesse kontrollieren, sondern sich auf externe Fertigungspartner verlassen, möglicherweise nicht in der Lage, Technologie- und Prozessverbesserungen so schnell umzusetzen.

Innoscience hat auch die Lehren gezogen, die auch für Silizium als Pionier bereits in der Vergangenheit gezogen wurden, indem es die Wafer-Durchmesser vergrößert und dadurch die Kosten pro Chip gesenkt hat. Seit seinen Anfängen hat sich Innoscience auf 8-Zoll-Wafer konzentriert. Betrachtet man einen 2 mm × 2 mm großen Chip, so können auf einem 6-Zoll-Wafer 3886 Bauteile hergestellt werden. Mit 8-Zoll-Wafern steigt diese Zahl auf 7265. Durch die nahezu doppelte Anzahl von Chips, die pro Wafer hergestellt werden können, sinken die Kosten für das einzelne Bauteil um 30 bis 40 Prozent, selbst wenn man den höheren Preis des Epi-Wafers berücksichtigt.

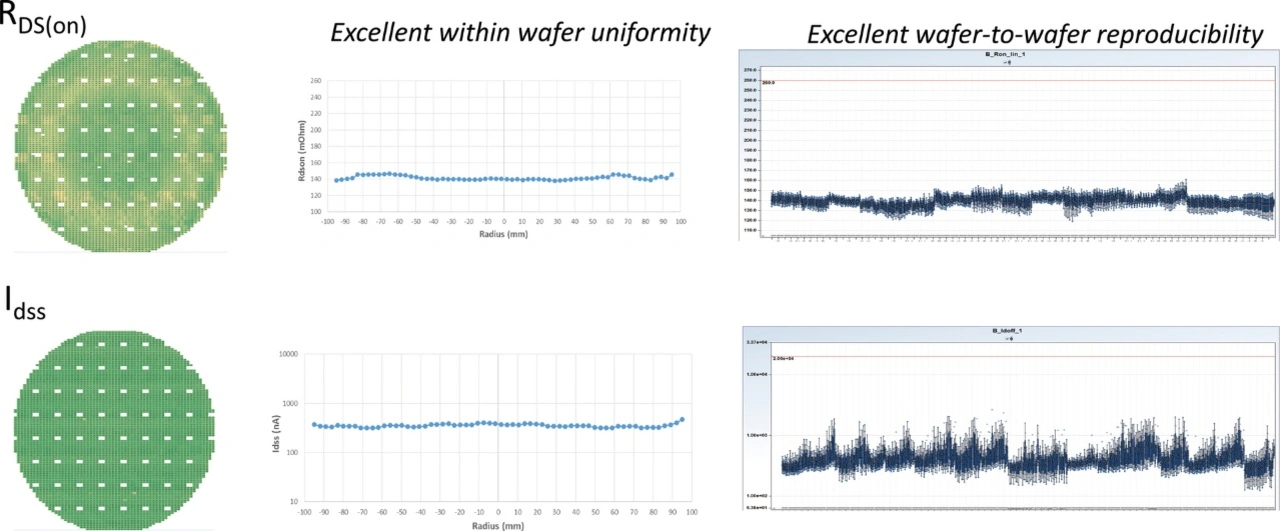

Schließlich hat Innoscience die Epitaxie und die Verarbeitung der Bauelemente optimiert, um die Ausbeute zu maximieren. Bild 3 zeigt eine sehr hohe Gleichmäßigkeit des Einschaltwiderstands (RDS(on)) und des Leckstroms (IDSS) über den gesamten Wafer, mit nur einem geringen Ausschuss an den Kanten. Dies gilt nicht nur innerhalb eines Wafers, sondern ist auch von Wafer zu Wafer reproduzierbar. In den Diagrammen zeigen sich die Eigenschaften von mehr als 100 Wafern, und sie belegen, dass der Prozess sehr stabil ist und eine hohe Ausbeute aufweist.

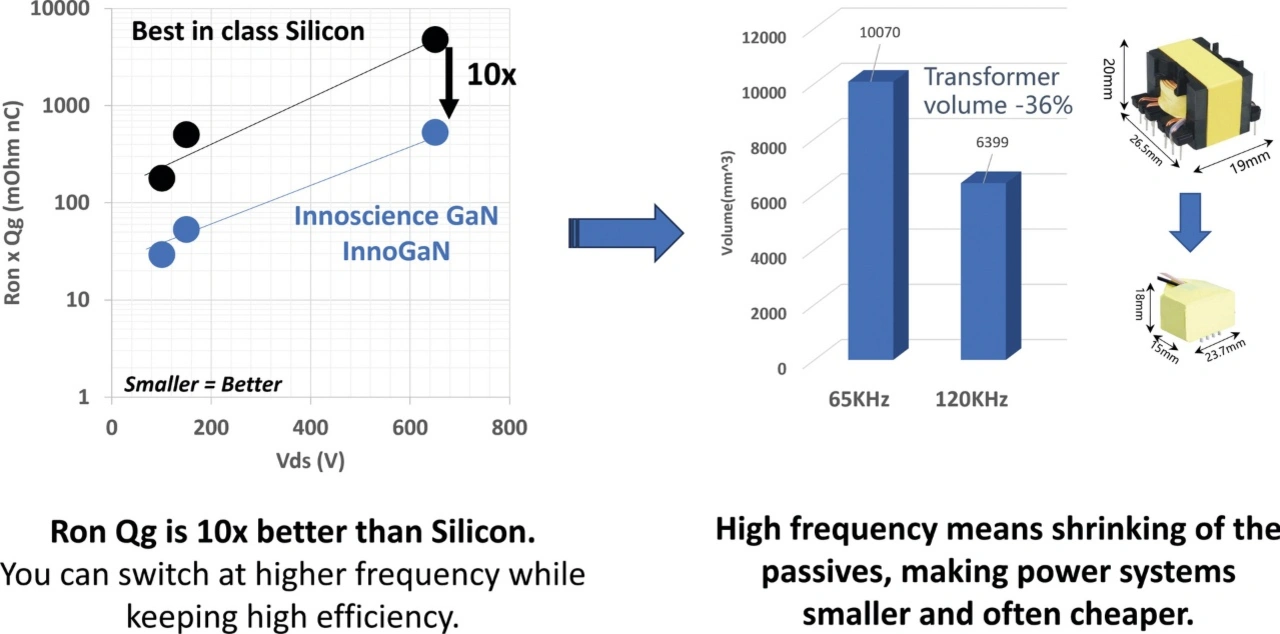

So ist es Innoscience gelungen, die Kosten für den GaN-Chip wettbewerbsfähig zu halten. Aber es gibt noch einen weiteren Aspekt. GaN hat eine Güte (FoM, Figure of Merit: Ron× Qg), die zehnmal besser ist als die von Silizium. GaN kann damit bei viel höheren Frequenzen schalten und dabei einen hohen Wirkungsgrad beibehalten (Bild 4). Somit lassen sich kleinere passive Bauelemente verwenden, was die Leistungselektronik bzw. Stromversorgung kleiner und oft auch kostengünstiger macht.

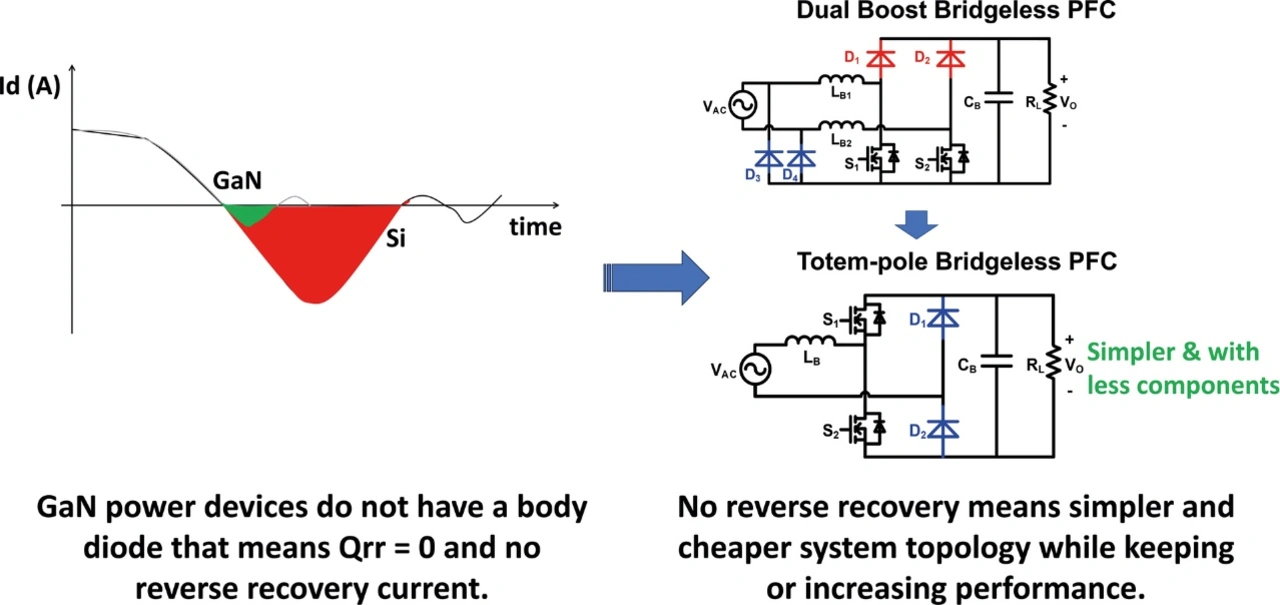

Ein weiterer Vorteil von GaN ist, dass keine Body-Diode vorhanden ist. Somit entfällt der Sperrverzögerungs-/Rückstrom (Bild 5). Daher können anstelle komplexer Aufbauten wie z. B. einer brückenlosen Leistungsfaktorkorrektur (PFC) mit doppelter Verstärkung, die üblicherweise mit Si-Bauteilen zum Einsatz kommt, viel einfachere Systeme wie etwa eine Totem-Pole-Konfiguration eingesetzt werden. Dies reduziert die Anzahl der benötigten Komponenten und spart Kosten.

GaN-Bauelemente sind also preislich mit Si konkurrenzfähig und ermöglichen kleinere und einfachere Systeme, die oft kostengünstiger sind als jene mit entsprechenden Si-Bauelementen. GaN ist also nicht teurer als Si und preislich durchaus wettbewerbsfähig.

Kommen wir nun zum zweiten Mythos über GaN – potenziell mangelnde Zuverlässigkeit.

Erstens ist GaN keine neue Technologie, auch wenn sie erst jetzt in Serienanwendungen der Leistungselektronik eingesetzt wird. Sie wird bereits seit mindestens 20 Jahren erforscht, entwickelt und beschrieben. So sind die Degradations-, also Verschlechterungsmechanismen – zeitabhängiger Durchbruch, Einfangen (Trapping) von Ladungsträgern und die Abnutzung durch heiße Ladungsträger – gut bekannt und können berücksichtigt werden. Damit können die Bauelemente so entsprechend ausgelegt werden.

Kürzlich und auch aufgrund eines von Dr. Bahl von Texas Instruments veröffentlichten Whitepapers wurde eine JEDEC-Richtlinie speziell für GaN-Leistungsschaltbausteine (JEP 180) ausgegeben. JEP 180 definiert Tests, die an Bauelementen durchgeführt werden sollten, um die realen Einsatzbedingungen in einer Anwendung zu simulieren (etwa Soft Switching, Hard Switching oder Ähnliches). Bei Si-MOSFETs gilt ein Bauelement, das die JEDEC-Standardtests bestanden hat, als qualifiziert, und das hat sich als ausreichend erwiesen.

Im Falle von GaN ist die Durchführung von JEDEC-Standardtests zwar obligatorisch, aber Zuverlässigkeitsexperten haben erkannt, dass erweiterte Tests erforderlich sind, um Ausfälle unter realen Schaltbedingungen, wie sie in JEP 180 beschrieben sind, zu vermeiden. Derzeit ist JEP 180 ein Leitfaden, aber es wird erwartet, dass er zu einem Standard wird. Innoscience und andere Unternehmen testen in Übereinstimmung mit diesem Standard.

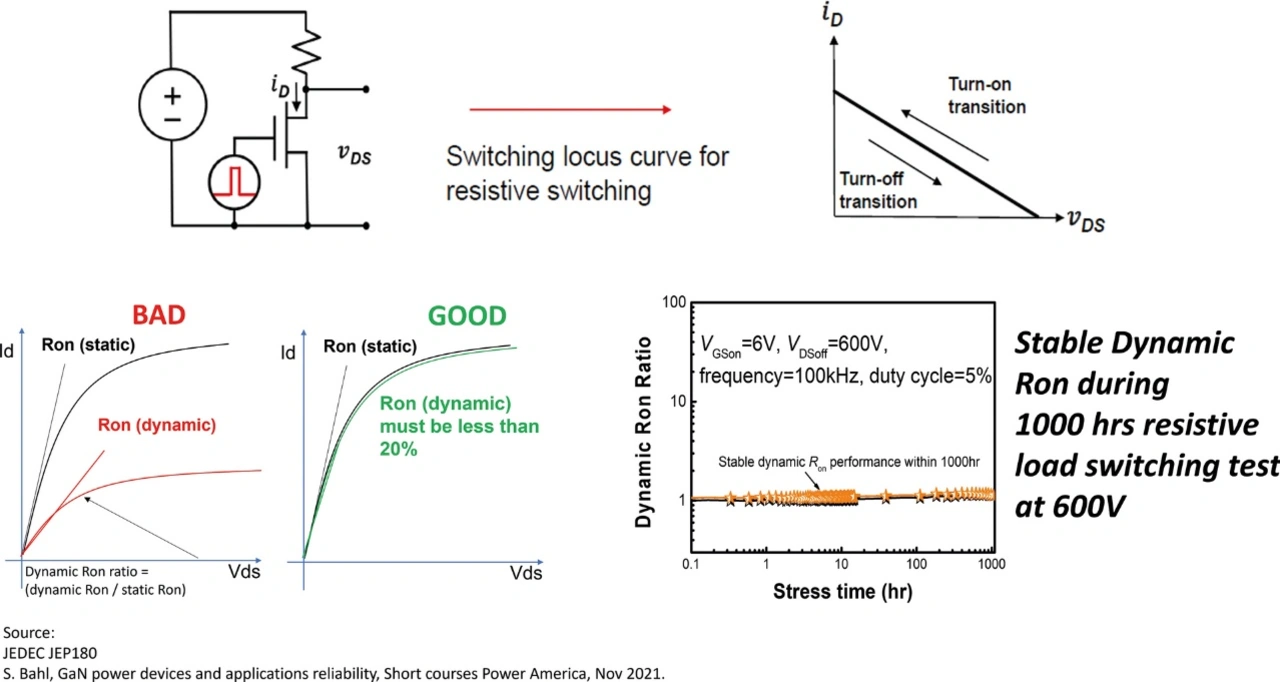

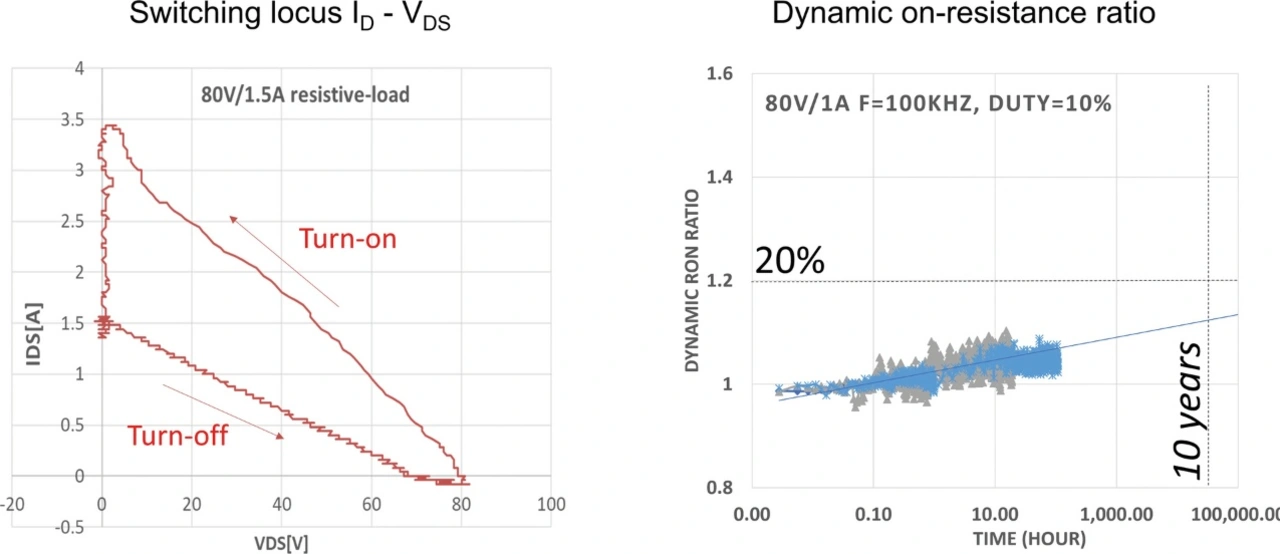

Bild 6a beschreibt weitere Einzelheiten. JEDEC 180 empfiehlt, dass ein Bauelement unter Widerstands-Schaltbedingungen belastet werden sollte. Ein »schlechtes« Bauelement weist einen Anstieg des Durchlasswiderstands aufgrund des Charge-Trapping-Effekts auf und zeigt eine Verschlechterung, sobald das Schalten hoher Spannungen beginnt. Ein »gutes« Bauelement weist nur geringe Unterschiede auf, und das dynamische Durchlasswiderstandsverhältnis, also das Verhältnis zwischen statischem und dynamischem Durchlasswiderstand, sollte unter 20 Prozent bleiben. Innoscience führt diesen Test 1000 Stunden lang durch. Dabei zeigt sich ein sehr stabiler Einschaltwiderstand, der bei InnoGaN-Bauelementen für hohe Spannungen (Bild 6a) sowie für niedrige Spannungen (Bild 6b) deutlich unter 20 Prozent bleibt.

Innoscience führt auch auf Chip- und Gehäuseebene routinemäßige JEDEC-Tests durch. Dazu zählen High-Temperature-Gate-Bias (HTGB), High-Temperature-Reverse-Bias-Stress (HTRB) und sogar H3TRB (High-Temperature-, High-Humidity-, High-Reverse-Bias-Test), ein sehr strenger Test, der typisch für die Automotive-Branche ist.

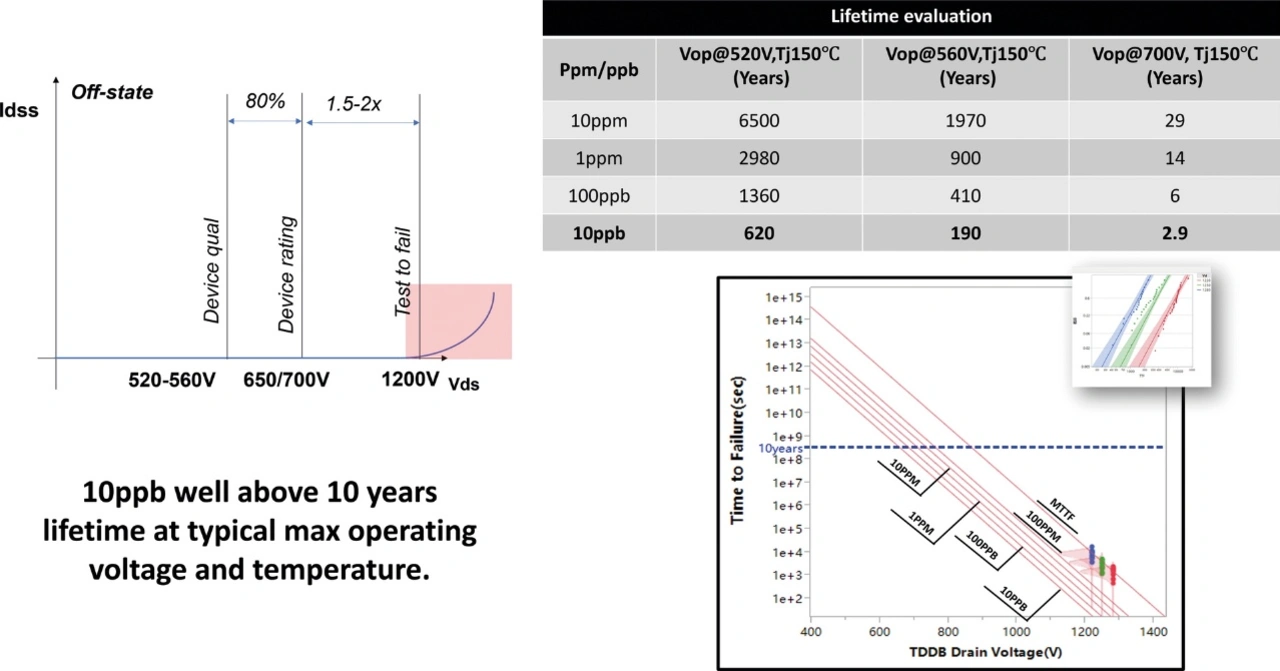

Darüber hinaus führt Innoscience auch Tests bis zum Ausfall durch, um die Lebenserwartung zu extrapolieren. Sie werden jenseits der maximalen Bauteilspezifikationen durchgeführt. So wird etwa für ein 650-V-Bauteil der beschleunigte Sperrspannungstest zwischen 1200 und 1300 V und bei 150 °C durchgeführt (Bild 7). Beschleunigte Tests zeigen, dass die Zeit, die erforderlich ist, um die InnoGaN-Bauteile bei maximaler Drain-Nennspannung oder maximaler Gate-Durchlassspannung zum Ausfall zu bringen, zehn Jahre Lebensdauer bei 10 ppb überschreitet.

Eine hervorragende Zuverlässigkeit ist das Ergebnis des IDM-Modells und Know-hows von Innoscience, bei dem alle wichtigen Bestandteile (von der Epitaxie bis zum Bauelementdesign) berücksichtigt wurden.

Fazit: GaN-Technologie ist bei richtiger Implementierung äußerst zuverlässig. Mit der erwiesenen Zuverlässigkeit und der preislichen Wettbewerbsfähigkeit sind die letzten verbleibenden Hindernisse beseitigt, die Anwender vom Einsatz von GaN-Leistungsbauelementen abhalten.