Wide-Bandgap-Materialien im Fokus

Impulsstrompotenzial von SiC-FETs

WBG-Halbleiterschalter wie etwa SiC-FETs zeichnen sich durch geringe statische und dynamische Verluste aus und halten hohen Impulsströmen stand. Doch wie lassen sich die Eigenschaften quantifizieren? Und was zeigt der Vergleich mit Silizium-/Si-Komponenten?

Wenn es darum geht, die Leistungsverluste in Halbleiterschaltern zu verringern, stehen Bauelemente mit breiter Bandlücke (Wide Bandgap, WBG) hoch im Kurs – insbesondere SiC-FETs, Kaskoden aus einem Siliziumkarbid-/SiC-JFET und Silizium-/Si-MOSFET in einem gemeinsamen Gehäuse. Diese Anordnung ergibt einen selbstsperrenden (Normally-off) Schalter mit einer einfachen Gate-Ansteuerung und Leistungszahlen (Figure of Merit, FoM), die alle konkurrierenden Technologien übertreffen. Eine besondere FoM ist der Durchlasswiderstand pro Flächeneinheit für eine bestimmte Spannungsklasse des Bauelements RDS(A), der die Kombination aus geringer statischer und dynamischer Verlustleistung und Wirtschaftlichkeit erfasst. Ein kleinerer Chip (Die) bedeutet mehr Stück pro Wafer und geringere Bauelementekapazitäten, was wiederum zu geringeren Schaltverlusten führt. So weit, so gut, aber besteht bei einem kleineren Die nicht das Risiko eines übermäßigen Temperaturanstiegs und einer geringeren Spitzenstromfähigkeit? Ganz im Gegenteil, wie wir hier beweisen können.

Jobangebote+ passend zum Thema

Durchlasswiderstand von SiC-FETs

Der 750-V-Baustein UJ4SC075005L8S von Qorvo im TOLL-Gehäuse erreicht eine RDS(A)-FoM, die 2,2-mal besser ist als die von SiC-MOSFETs der 4. Generation – und zwar über den gesamten Temperaturbereich hinweg. In der Praxis weist der Baustein einen Durchlasswiderstand von 5,4 mΩ bei 25 °C und 9,2 mΩ bei 125 °C auf, das ist vier- bis zehnmal weniger als bei Si- oder SiC-MOSFETs und GaN-HEMT-Zellen, die nur für 600/650 V ausgelegt sind.

Um diesen niedrigen Widerstand zu nutzen, sodass er sich in einem hohen Nennstrom niederschlägt, basieren SiC-FETs von Qorvo in TOLL-Gehäusen auf einer Silber-Sinter-Chip-Befestigung und auf einer Wafer-Dünnungstechnik, was zu einem Wärmewiderstand von nur 0,1 °C/W zwischen Sperrschicht und Gehäuse führt. Ein weiterer Vorteil ist, dass die maximale Sperrschichttemperatur für SiC-Bauelemente bei 175 °C liegt – verglichen mit Silizium, das 150 °C erreicht. Daher kann ein einzelnes Bauelement bei einer Sperrschichttemperatur von 175 °C und einer Umgebungstemperatur von 85 °C kontinuierlich 80 A leiten, wenn es an einem einfachen Kühlkörper mit 0,58 °C/W befestigt ist. Dies ermöglicht ein TOLL-Gehäuse mit einer Grundfläche von nur 9,8 mm x 11,65 mm und einer Höhe von 2,3 mm.

Der Spitzenstrom des SiC-FET ist weit höher als der Dauerstrom

Der TJ(Max)-Wert für einen SiC-Baustein und sein Nennstrom werden effektiv durch das verwendete Gehäuse bestimmt – SiC als Material ist tatsächlich in der Lage, bei über 500 °C sicher zu arbeiten. Selbst wenn wir den transienten Höchstwert im JFET eines SiC-Kaskaden-FET auf 175 °C begrenzen, besteht die Möglichkeit, Spitzenströme zu bewältigen, die ein Vielfaches des Dauerstroms betragen, wenn von niedrigeren Temperaturen aus gestartet wird.

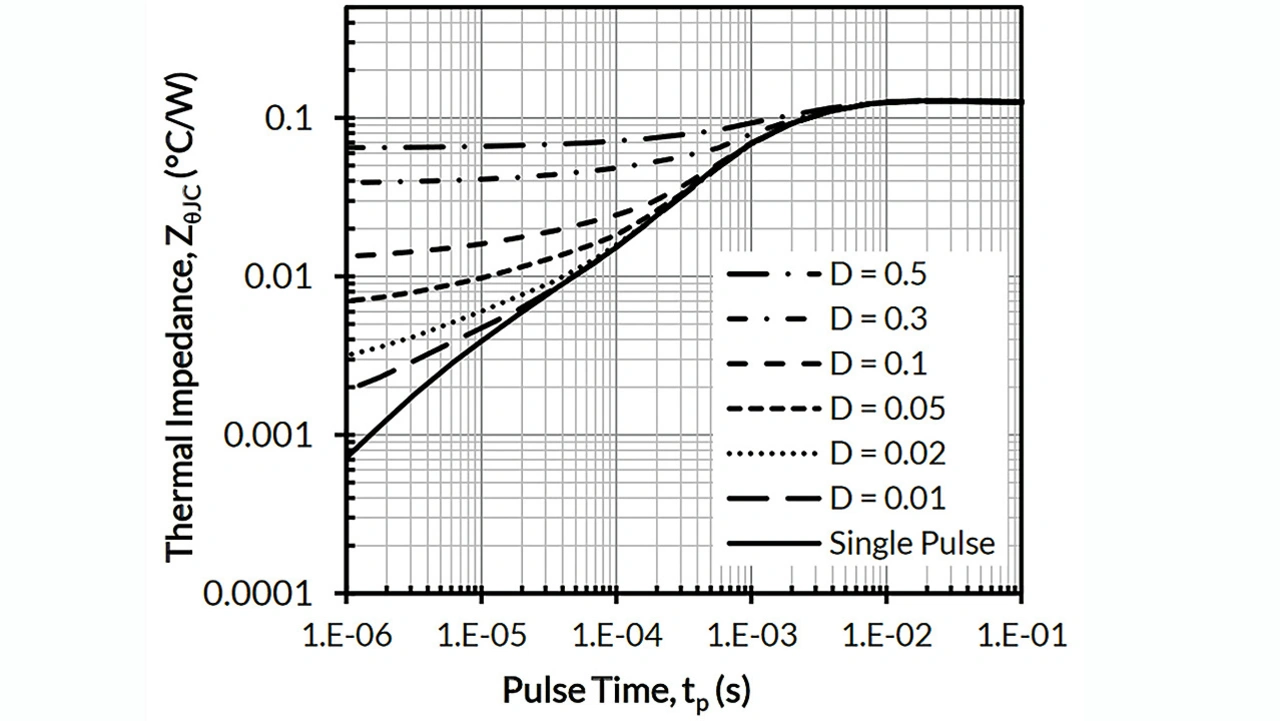

Das Zeitlimit für einen bestimmten Spitzenstrom wird durch die Wärmekapazität des Chips und seine unmittelbare Verbindung mit dem internen Kupfer-Leadframe bestimmt und kann durch ein Diagramm der transienten Wärmeimpedanz für einen bestimmten Chip und ein bestimmtes Gehäuse charakterisiert werden. Bild 1 zeigt die Werte für den UJ4SC075005L8S von Qorvo.

Aus dem Diagramm geht hervor, dass ein einzelner 100-µs-Impuls einen vorübergehenden Anstieg der Sperrschichttemperatur von etwa 0,015 °C pro Watt Verlustleistung verursacht, während bei Wiederholung desselben Impulses mit einem Arbeitszyklus von 50 % der Anstieg kontinuierlich etwa 0,07 °C/W beträgt. Bei einer Impulsdauer von etwa 10 ms tendiert die thermische Impedanz zum stationären Wert, und bei einer Dauer von mehr als einer Sekunde können Impulse mit einem Tastgrad von weniger als 50 % als Einzelereignisse behandelt werden, da sich die Sperrschicht zwischen den Impulsen vollständig abkühlt.

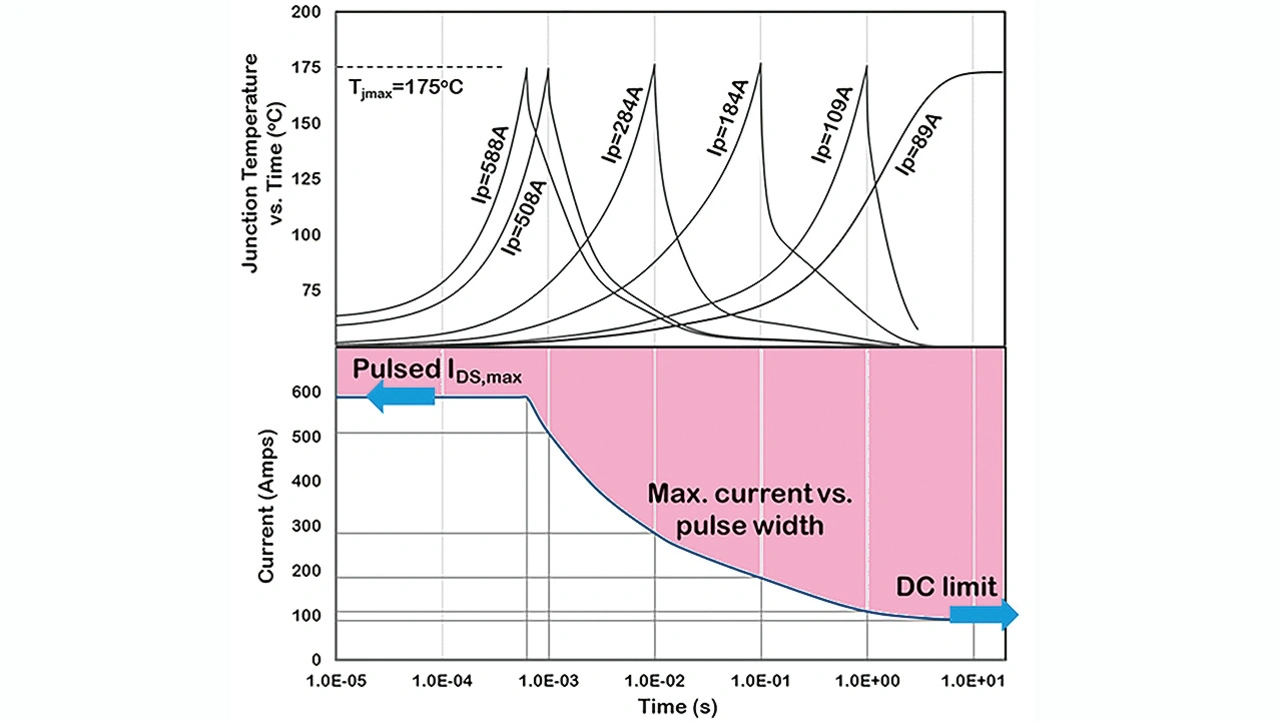

Was das in der Praxis für den UJ4SC075005L8S bedeutet, ist in Bild 2 dargestellt. In diesem Beispiel ist das Gehäuse des Bauelements an eine Kupferebene auf einer Leiterplatte gelötet, die mit Wärmeleitbahnen aus Kupfer zu einem Aluminiumkühlkörper auf der Rückseite verbunden ist. Der Kühlkörper wird auf 50 °C gehalten und ist durch ein isolierendes Wärmeleitmaterial (TIM) getrennt, was einen gewissen Wärmewiderstand erzeugt. In dieser Anordnung beträgt der Dauerstrom 89 A, aber es können bis zu 588 A Spitzenstrom für einen einzelnen 500-µs-Impuls verarbeitet werden, bevor die Sperrschicht 175 °C erreicht. Bild 2 zeigt die Zwischenwerte des Impulsstroms und die zulässigen Zeitdauern. Man erkennt die Abkühlung der Sperrschicht mit mehreren thermischen Zeitkonstanten nach dem Stromimpuls sowie die Gesamterwärmungs- und Abkühlungszeit im ungünstigsten Fall von etwa einer Sekunde, nach der die Impulse als Einzelereignisse betrachtet werden können.

Unter anderen Bedingungen mit geringerem Wärmewiderstand der Schnittstelle zu einem großen Kühlkörper kann der maximale Dauerstrom des Bauelements bis zu 120 A betragen, begrenzt durch die internen Bonddrähte.

Vergleich des SiC-FET mit Si-MOSFET

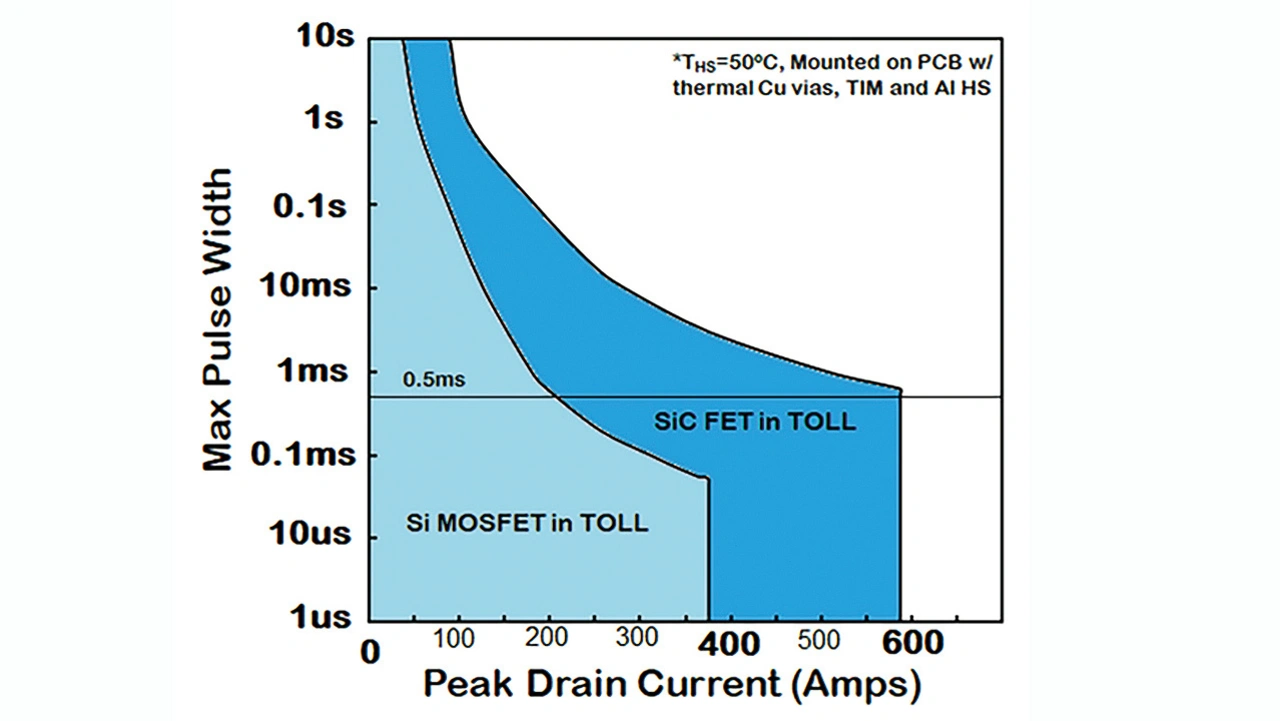

Die Ergebnisse können sich sehen lassen, aber wie sehen sie im Vergleich zu Si-MOSFETs aus, die derzeit z. B. in Halbleiter-Leistungsschaltern für geringere Leistung verwendet werden? Ein bekanntes Maß für Sicherungen und andere Geräte, die Stoßströme verarbeiten müssen, ist die I2t-Bewertung. Im TOLL-Gehäuse ist der SiC-FET hier etwa achtmal besser als ein Si-MOSFET. Bild 3 zeigt den Vergleich in der gleichen physikalischen Anordnung wie in Bild 2 mit dem Beispiel-SiC-FET, der 588 A für 500 µs standhält, während der Si-MOSFET nur etwa 200 A aushält, was einem I2t-Unterschied vom Faktor 8,6 entspricht.

Hohe Spitzenstrombelastbarkeit

Die höhere Impulsstrombelastbarkeit von SiC-FETs sorgt für eine bessere Sicherheitsmarge bei Überlastbedingungen in jeder Anwendung, aber es gibt noch weitere Vorteile: SiC-FETs eignen sich besonders für Leistungswandler mit induktiven Lasten, bei denen ein Überschwingen der Spannung unvermeidlich ist. Die Bauelemente haben eine robuste Avalanche-Fähigkeit: 316 mJ/Einzelimpuls im Falle des UJ4SC075005L8S. Darüber hinaus wird von leiterplattenmontierten DC/DC-Wandlern in Servern und ähnlichen Anwendungen zunehmend eine hohe Spitzenleistung in einem kleinen Formfaktor verlangt, was durch datenintensive Anwendungen wie KI, maschinelles Lernen (ML) und Streaming vorangetrieben wird.

Beim Design der Wandler wird häufig davon ausgegangen, dass die Sperrschichttemperaturen durch die auftretenden Spitzenströme in Richtung ihrer Maximalwerte getrieben werden und bei bestimmten Arbeitszyklen möglicherweise höher liegen. Informationen über die Sperrschichttemperatur werden von Sensoren und Vorhersage-Algorithmen zurückgemeldet, die eine digitale Steuerung (über PMBus) verwenden, um der Last Anweisungen zu geben, bei Bedarf »zu drosseln«. So wird vermieden, dass die Schaltübergänge ihr absolutes Maximum überschreiten. Auch hier bietet der hohe Spielraum der SiC-FETs Vertrauen in die Zuverlässigkeit und Lebensdauer des Stromversorgungssystems.

In diesen und ähnlichen Anwendungen kann die hohe Spitzenstrombelastbarkeit der SiC-FETs den Bedarf an mehreren parallel geschalteten Bauelementen verringern, was zu entsprechenden Einsparungen bei den Kosten für die Bauelemente und der Leiterplattenfläche führt.

Halbleiter-Schutzschalter profitieren

Halbleiter-Schutzschalter werden speziell für hohe Fehlerströme eingesetzt. Dabei kommen SiC-FETs und JFETs wegen ihres geringen Spannungsabfalls immer häufiger zum Einsatz und verdrängen IGBTs, insbesondere bei niedrigeren Stromstärken. Fehlerströme können jedoch immer noch sehr hoch sein, und die Spitzenstrombelastbarkeit von SiC-FETs ist hier von Vorteil. Sie sorgt für mehr Robustheit und ermöglicht der Überstromerkennung, eine längere Verzögerung vor der Reaktion vorzuhalten. Ein unerwünschtes Auslösen wird somit vermieden.

Fazit

SiC-FETs mit kleinem Formfaktor und Spitzenströmen von mehreren hundert Ampere sind ideale Bauelemente für moderne Leistungswandler, die eine hohe Leistungsdichte und Spitzenbelastbarkeit erfordern. Die Kennzahlen zeigen, dass die Bauteile deutlich besser sind als konkurrierende GaN- und Si- oder SiC-MOSFETs derselben Spannungsklasse. Das hier beschriebene Bauelement ist auf der Website von Qorvo zu finden, zusammen mit einer Reihe alternativer Bauteile, die sich für eine Vielzahl von Anwendungen eignen.

Der Autor

Pete Losee ist Senior Engineering Manager Power Devices bei Qorvo.