Wirkungsgrad und Ökologie

Effizientere Leistungswandler dank SiC-Transistoren

Fortsetzung des Artikels von Teil 1

Der SiC-Transistor in seinem Umfeld

Trotz all der soeben aufgeführten Vorteile beschränkte sich die Einsatz von SiC-Transistoren in der Vergangenheit aus Kostengründen auf ganz spezielle Anwendungen für anspruchsvolle industrielle Märkten (Stromversorgungen für Ölbohranlagen, militärische Systeme und Ähnliches). Wichtige Einflussfaktoren auf die Kosten waren die höheren Kosten und die geringere Verfügbarkeit von SiC-Substraten, die teureren Fertigungsprozesse für SiC und die geringeren Produktionsausbeuten (hauptsächlich infolge der höheren Defektdichten der Substrate).

In letzter Zeit haben Verbesserungen der Substratqualität dazu geführt, dass die Produktionsausbeute und die Zuverlässigkeit von SiC-Bauelementen signifikant gesteigert werden konnten. Zusammen mit der gestiegenen Verfügbarkeit von Substraten hat dies Verbesserungen des Wirkungsgrads und der Fertigungskosten dieser Transistoren bewirkt, was wiederum Anreize für die Verwendung dieser Bauelemente in Elektrofahrzeug-Systemen wie etwa Bordladegeräten und Traktionswechselrichtern geschaffen hat.

Da SiC-Transistoren ein effizienteres und höherfrequentes Schalten ermöglichen und deshalb die Verwendung kleinerer induktiver Bauelemente zulassen, treibt das WBG-Material die Verwendung von SiC in vielen Leistungswandlungs-Applikationen für den industriellen Markt voran, ganz abgesehen von den Vorstößen im Bereich der Automobil-Anwendungen.

SiC ist jedoch keineswegs für alle Anwendungen geeignet. Die Erfolge, die IGBTs in Systemen für erneuerbare Energie, USVs und Motorreglern verzeichnen, sind großenteils auf die niedrigen Leitungsverluste sowie darauf zurückzuführen, dass diese Anwendungen relativ geringe Schaltfrequenzen erfordern. IGBTs können zudem durch Ändern des Verhältnisses von VCE(SAT) und tfall in verschiedenen Familien angeboten werden, um wahlweise die Leitungsverluste oder die Schaltverluste zu optimieren.

Schaltet man mehrere IGBTs allerdings parallel, so ändert sich die Steigung der Ausgangskennlinie. Auf der einen Seite wird die Einschaltspannung niemals geringer sein als der Spannungs-Offset, der aus dem Knie in der IGBT-Kennlinie resultiert (etwa 0,8 V). Andererseits führt das Parallelschalten von n MOSFETs dazu, dass der RDS(on) eines einzelnen MOSFET durch n dividiert wird, was die geringstmöglichen Leitungsverluste ergibt.

In realen Anwendungen lässt sich diese Eigenschaft nutzen, ohne dass man unbedingt unter allen Bedingungen die geringstmöglichen Leitungsverluste erhält. Einige Motorregelungs-Anwendungen wie etwa Wechselrichter für Elektrofahrzeuge oder Kühlkompressoren arbeiten aber während des Großteils ihrer Lebensdauer nur mit einem Bruchteil (nämlich 20 bis 50 Prozent) ihrer Nennleistung, weshalb der Einsatz von SiC-Transistoren auch hier zu niedrigeren Verlusten und einem höheren Wirkungsgrad führt.

Jobangebote+ passend zum Thema

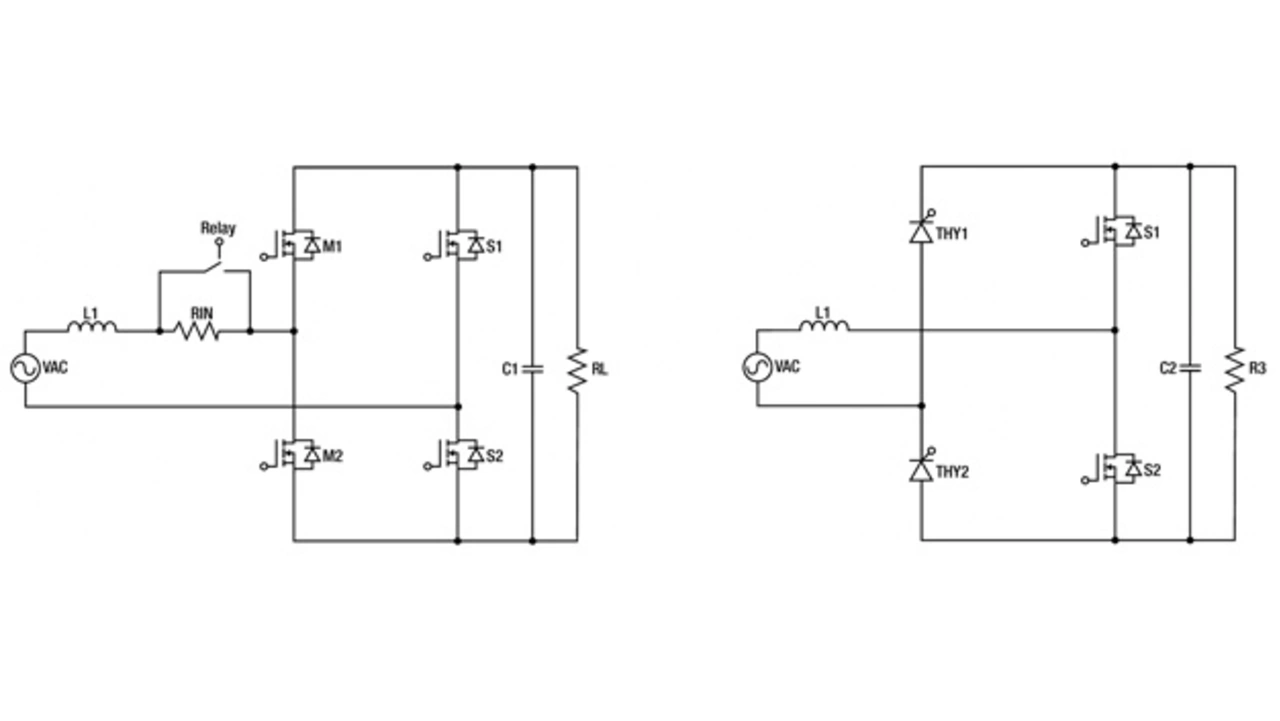

Totem-Pole- PFC-Schaltungen

Wie bereits erwähnt, können die Energieverluste vieler Leistungswandlungs-Anwendungen gravierende ökonomische und ökologische Konsequenzen haben. Eine effiziente Leistungsfaktor-Korrekturstufe (PFC) zwischen der eingangsseitigen Gleichrichterstufe (implementiert mit einer niederfrequent schaltenden Eingangsbrücke) und dem anschließenden Gleichspannungswandler kann zur Eindämmung dieser Verluste beitragen. Häufig aber müssen zum Erreichen des geforderten Wirkungsgrads die Verluste in allen drei Stufen der Stromversorgung minimiert werden. Brückenlose Topologien können hier helfen, indem sie die Verluste in der Eingangsstufe eliminieren und so daran mitwirken, den angestrebten Wirkungsgrad zu erreichen. So ist die brückenlose Totem-Pole-PFC-Topologie nur im lückenden Betrieb und damit hauptsächlich in Anwendungen mit geringer Leistung eingesetzt werden, weil die hohen Sperrerholströme der Body-Dioden in den MOSFETs zu großen Verlusten führen. SiC-Transistoren, die durch einen vernachlässigbar geringen Sperrerholstrom der internen Body-Diode gekennzeichnet sind, eröffnen jedoch ganz neue Perspektiven für diese Topologie. In Bild 4 sind die brückenlose Totem-Pole-PFC-Topologie (links) und die semi-brückenlose Totem-Pole-PFC-Topologie (rechts) zu sehen. Letztere nutzt zwei Thyristoren zur Begrenzung des Einschaltstroms. Damit wird die sonst übliche Schaltung ersetzt, in der dieselbe Funktion mit einem wenig effizienten Strombegrenzungs-Widerstand und einem Relais implementiert war.

In einer konventionellen PFC-Topologie kommen zwei Dioden-Spannungsabfälle in der Brückenschaltung und einer in der Hochsetzsteller-Stufe vor, während in der brückenlosen Totem-Pole-Topologie zwei widerstandsarme MOSFETs im niederfrequenten Zweig der Brücke ohne jegliche Spannungsabfälle arbeiten und damit den Wirkungsgrad verbessern. So minimiert die brückenlose Totem-Pole-PFC-Topologie nicht zuletzt auch die Verluste im leitenden Pfad. Wie in Bild 4 zu erkennen ist, besteht die Topologie aus zwei SiC-MOSFETs (S1 und S2), die mit einer hohen Schaltfrequenz von typisch 65 kHz bis 150 kHz schalten, sowie einem Paar niederohmiger MOSFETs (M1 und M2), die mit Netzfrequenz (47 bis 63 Hz) schalten. Damit besteht der leitende Pfad nur aus einem schnellen und einem langsamen Schalter.

Es ist möglich, die beiden Niederfrequenz-MOSFETs durch zwei Thyristoren zu ersetzen, was den Vorteil hat, dass der Einschaltstrom beim Anlaufen der Schaltung begrenzt wird. So kann auf das Relais und den strombegrenzenden Widerstand früherer Designs verzichtet werden. Dieser Ansatz zeichnet sich durch interessante Zuverlässigkeitsvorteile aus und senkt die Standby-Verluste gegenüber der traditionellen NTC/PTC-Schaltung zur Begrenzung des Einschaltstroms.

Im hochfrequenten Zweig sorgt die gegenüber Si-MOSFETs sehr geringe Sperrverzögerungs-Ladung der SiC-MOSFETs dafür, dass sich die brückenlose Totem-Pole-Topologie auch für Anwendungen hoher Leistung eignet. Mit

ihrem sehr hohen Wirkungsgrad und ihrer großen Leistungsdichte erfüllt sie die Anforderungen von unterbrechungsfreien Stromversor-gungen und Motorregelungs-Applikationen.

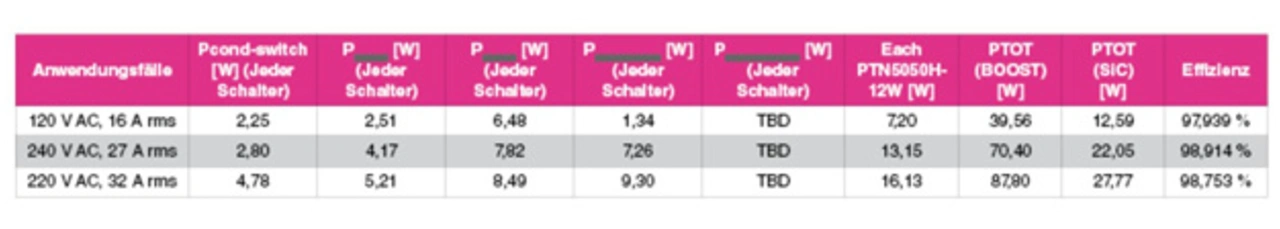

In Tabelle 2 ist der berechnete Wirkungsgrad einer semi-brückenlosen Totem-Pole-PFC-Schaltung wiedergegeben, die zwei Thyristoren und zwei SiC-MOSFETs enthält. In diesem Beispiel kommen Thyristoren des Typs TN5050H-12WY und SiC-MOSFETs vom Typ STCW90N65G2V zum Einsatz. Die SiC-FETs besitzen einen maximalen RDS(on) von 24 mΩ bei 25 °C und werden mit positiven und negativen Gate-Spannungen (+20 V, –4 V) angesteuert. Hierfür kommt ein galvanisch isolierter, zweikanaliger Habbrücken-Gate-Treiber des Typs STGAP2D zum Einsatz, der sowohl als Stromquelle als auch als Stromsenke bis zu 4 A verkraftet. Erstellt wurde die Tabelle für unterschiedliche Eingangsspannungen und Leistungen, basierend auf einer Gleichspannung von 400 V und einer Schaltfrequenz von 100 kHz.

Die Analyse beruht auf den folgenden Annahmen:

- Die Verluste in den Induktivitäten und Kondensatoren bleiben unberücksichtigt.

- Es wird eine Sperrschichttemperatur von 125 °C angenommen.

- Jeder Schalter leitet während der einen Netzhalbwelle einen Vorwärts- und während der anderen Halbwelle einen Rückwärtsstrom (Synchrongleichrichter und Body-Diode).

Wie man sieht, lässt sich dank der SiC-Technologie auch bei niedrigen Eingangsspannungen ein hoher Wirkungsgrad erzielen. Bei höheren Eingangsspannungen und Leistungen ist der Wirkungsgrad sogar höher als erwartet.

- Effizientere Leistungswandler dank SiC-Transistoren

- Der SiC-Transistor in seinem Umfeld

- Wechselrichter als zweites Beispiel