Machine Learning

Neuronale Netze effektiv beschleunigt

Fortsetzung des Artikels von Teil 1

Spiking Neural Networks (SNNs)

Neben den bis hierher ausschließlich betrachteten digitalen DL-Beschleunigern beherbergt der KI-Chip-Zoo aber noch weitere Gattungen. Diese unterscheiden sich in der Durchführung der Berechnungen: Bei DNNs laufen alle Berechnungen Layer-weise wie eine Welle durch das neuronale Netz – das heißt, zuerst wird Layer 1 komplett berechnet, dann Layer 2 und so weiter. Insofern ist ein Neuron im Layer 1 erst einmal passiv, nachdem es in der aktuellen Inferenz berechnet wurde, und es wird erst wieder in der nächsten Inferenz aktiv. Eine Alternative dazu stellen Spiking Neural Networks (SNNs) dar. Die Netzwerk-Topologie von SNNs ähnelt prinzipiell der von DNNs. Allerdings können hier die Neuronen wie beim biologischen Gehirn prinzipiell zu jedem Zeitpunkt aktiv werden. Sie senden dann kurze Impulse, sogenannte Spikes, zu ihren Nachfolge-Neuronen. Je mehr ein Neuron von seinen Vorgängern angeregt wird, umso häufiger pulst es selbst. Die Pulsfrequenz ist also das Äquivalent zum Ausgangswert (Output Feature) eines DNN.

Da SNNs ans Hirn angelehnt sind, werden sie – wie die analogen Äquivalente, die weiter unten vorgestellt werden – auch als neuromorphe Schaltungen bezeichnet. Dieser Begriff ist aber schwammig, teilweise werden auch DL-Beschleuniger dazugezählt. An einfachen neuromorphen Schaltungen wird faktisch schon seit Jahrzehnten geforscht. Enormen Auftrieb hat das Thema aber erst in den letzten Jahren erhalten, zum einen durch die Erfolge von DL in der Praxis, zum anderen durch die akademische Forschung im HBP. In dem Projekt von der University of Manchester und der TU Dresden wurde die »SpiNNaker«-Chip-Architektur entwickelt. Darüber hinaus haben IBM mit seinem »TrueNorth« und Intel mit dem »Loihi« bereits digitale SNN-Chips produziert, die allerdings nicht kommerziell verfügbar sind. Man erwartet von diesen SNN-Chips bei der gleichen Aufgabe eine nochmals geringere Leistungsaufnahme und kürzere Latenzen gegenüber DLI-Beschleunigern. Weiterhin gibt es Ansätze, wie SNN-Chips während der Inferenz weiter trainiert werden können. Dadurch können die Chips für »Reinforcement Learning« eingesetzt werden. Auf der anderen Seite gibt es aber beim Thema Training und Hyper-Parameter-Auswahl für SNNs immer noch zahlreiche offene Fragen, während bei DNNs das Wissen deutlich fortgeschrittener ist. Mit dem »Akida« von BrainChip ist für 2019 bereits ein kommerzieller SNN-Chip angekündigt, eine größere Anzahl von Produkten und Anwendungen ist jedoch erst in einigen Jahren zu erwarten.

Jobangebote+ passend zum Thema

Analoge DLI-Beschleuniger

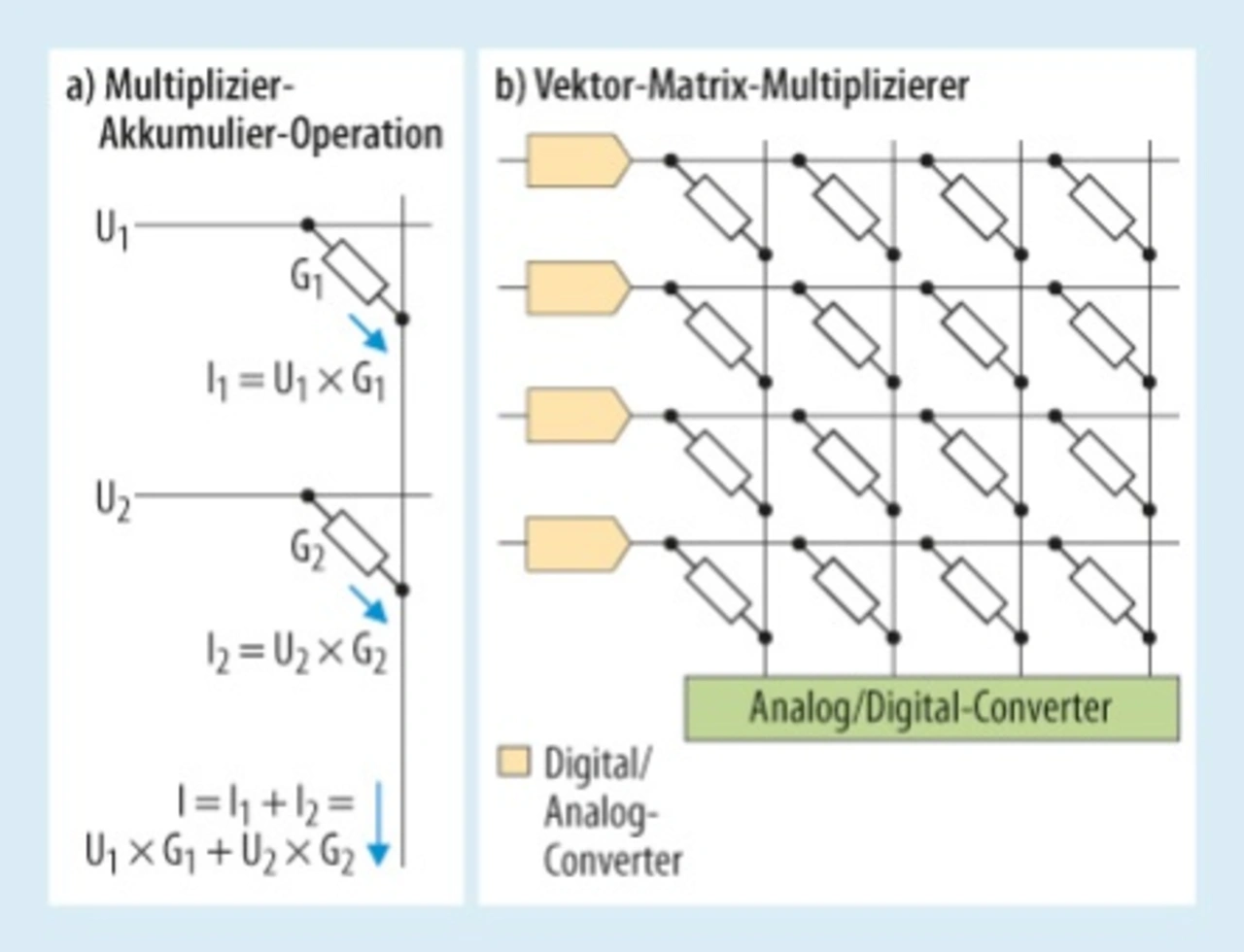

Bis hierher war die Rede rein von digitalen Schaltkreisen. Wie bereits erwähnt, gibt es die beiden Kategorien DLI-Beschleuniger und SNN-Chips auch als teilweise analoge Variante. Neben den bereits beschriebenen bedeutenden Fortschritten bei den digitalen Varianten wurde in letzter Zeit auch viel Aufwand für die Entwicklung von analogen DLI-Beschleunigern betrieben. Dieser Begriff bezeichnet analoge speicherbasierte Schaltungen, welche die MAC-Berechnungen mit Hilfe einer Speichermatrix mit Crossbar-Architektur vornehmen. Im Crossbar sind alle Gewichtsfaktoren der Synapsen als Leitwerte von memristiven Komponenten gespeichert. Memristoren sind elementare Komponenten, deren Widerstandswert durch Anlegen eines Stroms einprogrammiert werden kann und dann auch ohne diesen Strom gehalten wird.

Wie in Bild 6 gezeigt, nutzt der Crossbar-Ansatz das Ohmsche und Kirchhoffsche Gesetz für eine analoge MAC-Berechnung. Jeder Input-Wert einer Synapse wird als Spannungswert U an den jeweiligen Memristor angelegt, dessen Leitwert G gleich dem Gewicht ist. Der dann fließende Strom I ist das Produkt aus I = G × U. Die Ströme aller Synapsen eines Neurons treiben eine gemeinsame Leitung und addieren sich damit. Der Summenstrom des Neurons muss anschließend noch eine nicht-lineare Aktivierungsfunktion passieren und stellt dann den Ausgangswert des Neurons dar. Weil die MAC-Berechnung dort stattfindet, wo die Speicher sind (In-Memory-Computation), müssen die Gewichte nicht von anderen On- oder gar Off-Chip-Speichern zur CPU gestreamt werden. Außerdem läuft die Berechnung aller MAC-Operationen voll parallel. Deswegen verbessert die analoge Cross-Bar-Architektur sowohl die Inferenz-Geschwindigkeit als auch die Energieeffizienz [6]. Aus diesem Grund sind analoge Beschleuniger sehr gut für Fully Connected Layer geeignet, während Convolutional Layer auch von digitalen Beschleunigern berechnet werden können [6].

Crossbar-Architektur

Diese Architektur benötigt resistive Speicherzellen (Memristoren) wie RRAM (Resistive RAM), PCM (Phase-Change Memory), MRAM (Magnetic RAM), STT-MRAM (Spin Transfer Torque Magnetic RAM), CBRAM (Conductive Bridge RAM), OxRAM (Oxide Based RRAM) oder FeRAM (Ferroelectric RAM), die alle nichtflüchtig sind (Embedded Non-Volatile RAM). Sie unterscheiden sich voneinander durch die Anzahl der möglichen Schreibzyklen, die Speicherungszeit – um einen Leitwert zu programmieren – und die physikalische Dichte [3, 6]. Die Memristoren weisen einen Zustand mit hohem Widerstand und einen mit niedrigem Widerstand auf. Der Wechsel zwischen beiden Zuständen erfordert das Anlegen einer bestimmten Spannung über eine Mindestzeit.

Die Crossbar-Architektur benötigt sowohl Analog-Digital-Converter (ADCs) als auch Digital-Analog-Converter (DACs) an ihrer Peripherie. DACs sind für die Umwandlung der Input-Werte der Synapsen in Spannungen U1, U2 bis Un nötig. Diese Werte liegen in der Regel digital gespeichert vor. Ein ADC ist für die Umsetzung des summierten Ausgangsstroms erforderlich. Der ADC hilft dabei, den Ausgangswert wieder digital abzuspeichern. Die Anforderungen dieser Umsetzer könnten die gesamte Fläche und Leistungsaufnahme der Schaltung extrem erhöhen. Deswegen muss die Wortbreite der ADCs und DACs begrenzt und dabei die Rechengenauigkeit des DNNs durch geeignete Techniken erhalten werden [5]. Der »errechnete« Ausgangsstrom des Crossbars kann statt als Digitalwert auch als Spike ausgegeben werden. Dafür wird eine Art Schmitt-Trigger-Schaltung benötigt, bei der die Frequenz der Ausgangsspikes dann proportional zu dem Ausgangstrom des Crossbars ist.

Die noch am weitesten in der Zukunft liegende Art von neuromorpher Hardware sind schließlich analoge SNN-Schaltungen, bei denen in analogen Neuronen Spikes erzeugt werden – fast so wie im menschlichen Gehirn. In Deutschland hat die Universität Heidelberg mit der »BrainScaleS«-Architektur im HBP eine sehr anspruchsvolle analog-digitale SNN-Schaltung entwickelt. Um zwischen den hier vorgestellten verschiedenen Ansätzen für neuromorphe Hardware vergleichen zu können, sollten als Metriken unter anderem Leistungsaufnahme, Latenz, Durchsatz und Kosten berücksichtigt werden [3]. Weitere Metriken können die Recheneffizienz (Anzahl von 16-bit-äquivalenten Operationen pro Sekunde und pro Quadratmillimeter), die Leistungseffizienz (Anzahl von 16-bit-äquivalenten Operationen pro Watt) und die Speichereffizienz (On-chip Kapazität für die Gewichtsfaktoren pro Quadratmillimeter) sein [5].

Aufholjagd

Die Entwicklung von KI-Chips, das heißt DL-Beschleunigern und neuromorpher Hardware, hat seit 2015 eine ungeahnte Dynamik entwickelt. Diese Dynamik wird auch in den nächsten Jahren anhalten, einige vorhandene Anwendungen stark umkrempeln und viele gänzlich neue Anwendungen hervorbringen. Eine weitere Reduktion der Leistungsaufnahme um mehr als zwei Größenordnungen ist dabei durchaus realistisch. Insofern stellt diese neue Halbleiter-Kategorie eine große Chance für neue Anwendungen in unterschiedlichsten Wirtschaftsbranchen dar. China hat das schon vor längerem begriffen, Europa und Deutschland sollten schnell nachziehen.

Literatur

[1] https://www.iis.fraunhofer.de/de/ff/kom/iot/neuromorphic.html

[2] https://www.tractica.com/newsroom/press-releases/deep-learning-chipset-market-to-reach-66-3-billion-by-2025/

[3] Sze V., Chen Y., Yang T. and Emer J.S.: Efficient Processing of Deep Neural Networks: A Tutorial and Survey. in Proceedings of the IEEE. vol. 105. no. 12. pp. 2295-2329. Dec. 2017.

[4] Han S., Mao H., Dally W.J.: Deep Compression: Compressing Deep Neural Networks with Pruning, Trained Quantization and Huffman Coding.

Die Autoren

Dr. Marco Breiling

studierte Elektrotechnik in Karlsruhe, Trondheim, Paris und Southampton und promovierte in Erlangen. Er ist seit 2001 am Fraunhofer Institut für Integrierte Schaltungen IIS in Erlangen tätig. Dort koordiniert er als Chief Scientist die neuromorphen Hardware-Aktivitäten.

Prof. Dr. Rastislav Struharik

ist CTO von Kortiq und außerordentlicher Professor am Institut für Energie, Elektronik und Telekommunikation an der Universität Novi Sad. Er erhielt den B.Sc., M.Sc. und Ph.D. in Elektronik und Telekommunikation an der Universität von Novi Sad in den Jahren 1999, 2005 und 2009. Dort ist er auch Leiter der Abteilung für Embedded Systems and Algorithms. Seine Forschungen und Interessen umfassen rekonfigurierbares Computing, Hardwarebeschleunigung von Algorithmen, Machine Learning, DSP-Algorithmen und Design und Verifikation von komplexen digitalen Systemen.

Dr. Loreto Mateu

erwarb ihren Bachelor in Industrial Engineering an der Universitat Autònoma de Barcelona und schloss das Studium 1997 ab. Von 1999 bis 2002 absolvierte sie ihren Master in Elektrotechnik an der Universitat Politècnica de Catalunya, Spanien. 2009 beendete sie ihre Dissertation zum Thema »Energy Harvesting from Human Passive Power«. Seit 2007 arbeitet sie am Fraunhofer IIS, und seit 2018 ist sie Gruppenleiterin der Gruppe »Advanced Analog Circuits«.

- Neuronale Netze effektiv beschleunigt

- Spiking Neural Networks (SNNs)