Siemens EDA

Multiphysikalische Effekte bei 3D-IC-Designs beherrschen

3D-ICs bieten mehr Leistung und Effizienz durch vertikal gestapelte Chiplets, erhöhen aber die Komplexität durch thermische, mechanische und elektrische Wechselwirkungen. Daher sind multiphysikalische Analysen und eine enge Zusammenarbeit über alle Designbereiche hinweg entscheidend.

Die Halbleiterindustrie steht an einem Wendepunkt: Die Grenzen des Mooreschen Gesetzes machen einen Übergang zur dreidimensional integrierten Schaltkreistechnologie (3D-IC) erforderlich. Durch die vertikale Integration mehrerer Chiplets ermöglichen 3D-ICs Fortschritte in Bezug auf Leistung, Funktionalität und Energieeffizienz. Das Stapeln von Dies erhöht jedoch aufgrund multiphysikalischer, d.h. thermischer, mechanischer und elektrischer Wechselwirkungen die Komplexität. Dies gilt es bereits beim Entwicklungsbeginn zu berücksichtigen.

Der Übergang von zweidimensionalen (2D) SoCs zu gestapelten 3D-ICs verändert die Designumgebung von Grund auf. 2D-SoCs profitieren von etablierten Prozess-Designkits (PDKs) und vorhersehbaren Workflows. Die 3D-Integration führt hingegen oft zu einer Kombination heterogener Dies, die verschiedene Prozessknoten und neue Verbindungstechnologien verwenden. Das bringt zusätzliche Variablen für den gesamten Design- und Verifizierungsprozess mit sich. Multiphysikalische Phänomene sind keine isolierten Probleme mehr, sondern integrale Bestandteile des Gesamterfolgs für ein Design.

Multiphysik: ein neues Design-Erfordernis

Die vertikale Struktur von 3D-ICs, die durch Silizium-Vias und Mikrobumps verbunden und in hochmoderne Packaging-Materialien eingebettet sind, erzeugt eine eng gekoppelte Umgebung. In dieser kommt es zu einer komplexen Wechselwirkung zwischen Wärmeableitung, mechanischer Integrität und elektrischem Verhalten.

Bei 2D-Chips wurden die thermischen und mechanischen Prüfungen unter überschaubaren Auswirkungen oft bis zum Ende des Zyklus hinausgeschoben. Doch bei 3D-ICs birgt eine Verschiebung dieser Analysen das Risiko kostspieliger Neu-Designs oder Ausfälle bei Leistung und Zuverlässigkeit. Das herkömmliche SoC-Design beruht häufig auf High-Level RTL-Beschreibungen, bei denen viele physikalische Optimierungen frühzeitig festgelegt werden und sich später nur schwer ändern lassen. Die Komplexität und physikalische Wechselwirkung bei 3D-ICs erfordert hingegen ein frühzeitiges Feedback aus den physikalischen Analysen bei der RTL- und Layoutplanung, damit die Entwickler fundierte Entscheidungen treffen können, bevor diese durch kostspielige Einschränkungen behindert werden.

Ein Chiplet kann für sich genommen für eine bestimmte Spezifikation gut funktionieren, aber trotzdem unter reduzierter Zuverlässigkeit und Leistung leiden, wenn es den realen Bedingungen eines 3D-Stacks ausgesetzt wird. Nur eine frühzeitige, prädiktive multiphysikalische Analyse kann diese Risiken aufdecken und eine kosteneffiziente Risikominimierung ermöglichen. Eine kontinuierliche multiphysikalische Bewertung muss bei der Layoutplanung beginnen und sich durch jede Design-Iteration fortsetzen. Jede Layout-, Schnittstellen- oder Materialänderung kann neue thermische oder mechanische Belastungen mit sich bringen, die neu bewertet werden müssen, um die Systemzuverlässigkeit und Ausbeute zu gewährleisten.

Verlagerung des IC-Designs in die Systemebene

3D-ICs erfordern eine enge Zusammenarbeit zwischen spezialisierten Teams: Den-Entwicklern, Interposer-Experten, Packaging-Ingenieuren und in zunehmendem Maße auch Elektroniksystemarchitekten und RTL-Entwicklern. Jede Gruppe verfügt über ihre eigenen Toolchains und Datenstandards, oft mit unterschiedlichen Netzbezeichnungskonventionen, Komponentenorientierungen und Funktionsdefinitionen, was zu Kommunikations- und Integrationsschwierigkeiten führt.

Zusätzlich zu den internen Herausforderungen umfasst das 3D-IC-Design oft Chiplets von mehreren Anbietern - Foundries, Halbleiterherstellern und OSAT-Unternehmen –, jeder mit unterschiedlichen Methoden und Datenformaten. Während die Verwendung handelsüblicher Chiplets Flexibilität bietet und die Entwicklung beschleunigt, kann die Integration bisher verborgene multiphysikalische Probleme aufdecken. Ein für sich betrachtet voll funktionstüchtiges Chiplet kann nach dem Stapeln bereits die Spezifikation verfehlen, was die Notwendigkeit einer engeren Zusammenarbeit in der Branche unterstreicht.

Die Beseitigung dieser Unterschiede erfordert einen Verantwortlichen auf Systemebene, unterstützt durch umfassende EDA-Plattformen, die Methoden vereinheitlichen und Daten domänenübergreifend zusammenführen. Dies gewährleistet Konsistenz und reduziert die Fehler, die mit isolierten Arbeitsabläufen einhergehen. Für EDA-Anbieter ist es unerlässlich, integrationsfreundliche Umgebungen und Tools zu entwickeln, die eine solche Zusammenarbeit ermöglichen.

Die Zusammenarbeit zwischen den Unternehmen hängt nun ebenfalls von robusteren Tools und Methoden für den Datenaustausch ab. EDA-Anbieter spielen dabei eine zentrale Rolle, indem sie Plattformen und Standards für eine nahtlose Kommunikation und Datenaggregation zwischen Fabless-Unternehmen, Halbleiterherstellern und OSATs bereitstellen.

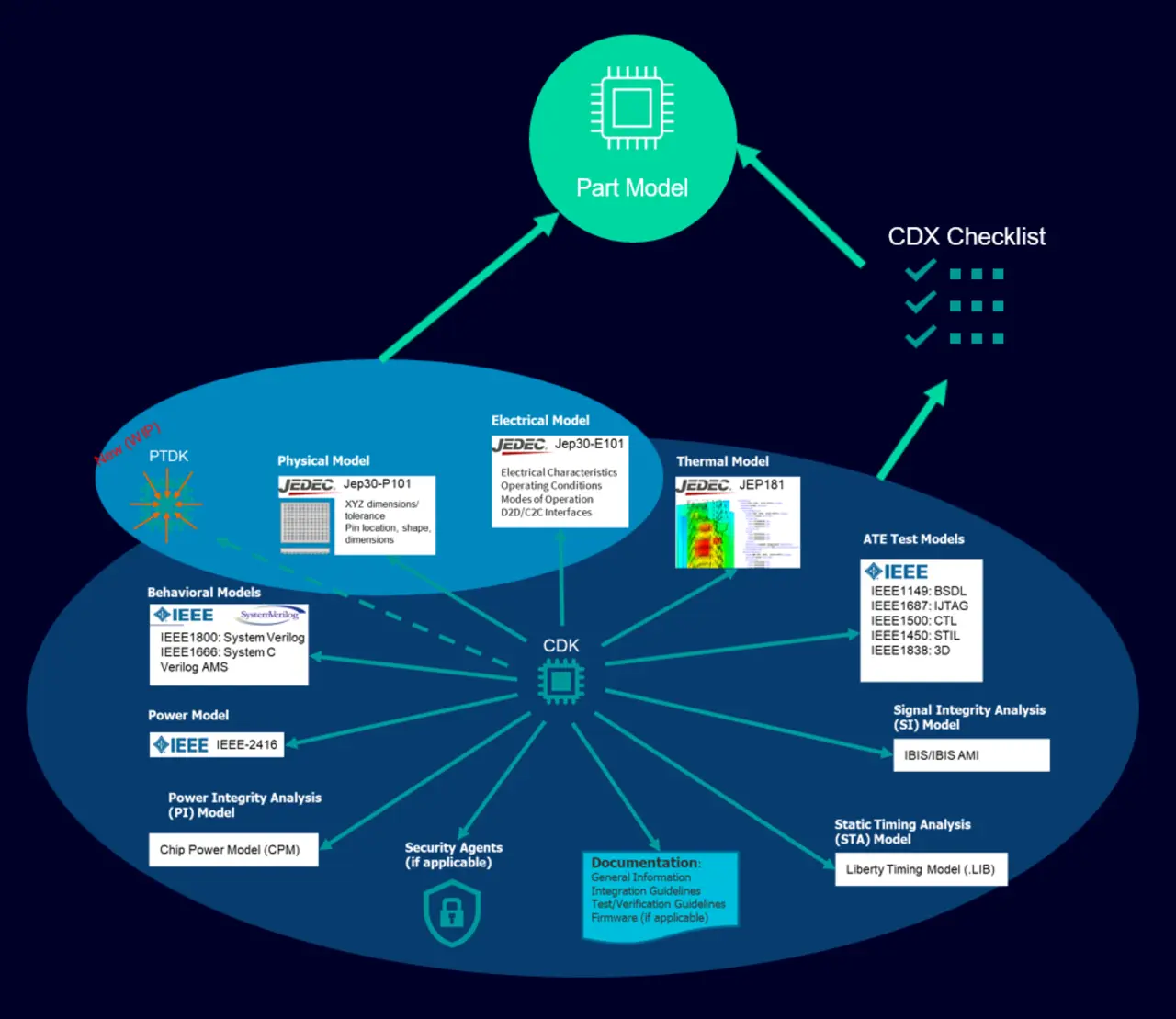

Auf Branchenebene entstehen neue Standards und 3D-IC-Designkits. Diese wurden von der CDX-Arbeitsgruppe und Industriepartnern entwickelt, um die bestehenden Herausforderungen zu bewältigen und eine gemeinsame Sprache zur Beschreibung von 3D-IC-Komponenten, Schnittstellen und Package-Architekturen zu schaffen. Diese Standards sind unerlässlich, um einen zuverlässigen Datenaustausch und eine Integration zwischen verschiedenen Teams und Lieferkettenpartnern zu ermöglichen.

Jobangebote+ passend zum Thema

Programme wie die 3Dblox-Initiative von TSMC bieten vorab festgelegte Platzierungs- und Verbindungsdefinitionen, wodurch sie Unklarheiten reduzieren und die Interoperabilität der Tools fördern.

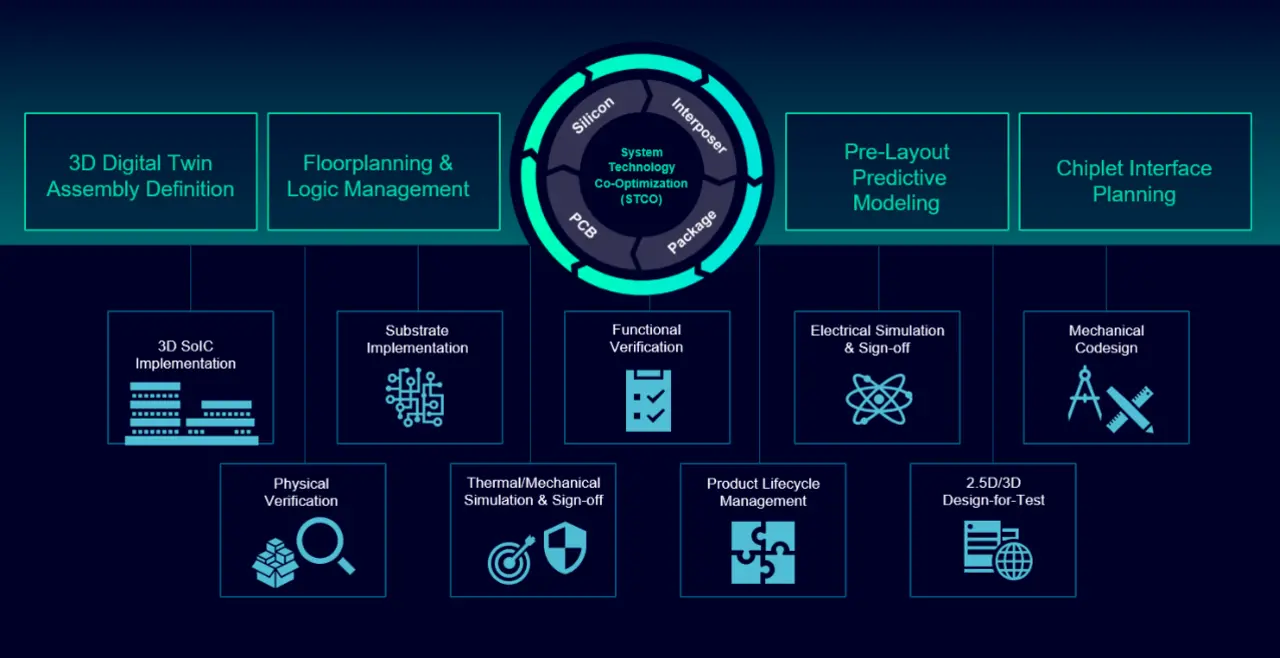

Digitaler Zwilling und prädiktive Multiphysik

Das Konzept des digitalen Zwillings erweitert die multiphysikalische Analyse auf den gesamten Produktlebenszyklus. Die durchgängige Verwendung einer genauen digitalen Darstellung – von Details auf Transistorebene bis hin zur vollständigen Systemintegration – ermöglicht eine vorausschauende Simulation und Optimierung, bei denen Wechselwirkungen bis hin zur Packaging-, Leiterplatten- oder Systemebene berücksichtigt werden. Durch den Transfer der multiphysikalischen Ergebnisse auf die verschiedenen Abstraktionsebenen können Teams prüfen, ob das Verhalten eines Chiplets unter thermischen und mechanischen Belastungen die Zuverlässigkeit des Endprodukts realistisch vorhersagt.

Bei 3D-ICs müssen elektrische Modelle für das Chiplet durch multiphysikalische Daten ergänzt werden, die aus Simulationen auf Stackebene erfasst worden sind. Eine Back-Annotation der Temperatur- und Belastungsergebnisse aus der Package-Ebenen-Analyse in die Chiplet-Netzlisten bildet die Grundlage für genauere elektrische Simulationen auf Systemebene. Diese Rückkopplungsschleife wird zu einem kritischen Teil der Abnahme und stellt sicher, dass jedes Chiplet innerhalb seines Betriebsfensters im voll bestückten System ordnungsgemäß funktioniert.

»Immer cool bleiben«

Das Wärmemanagement ist der entscheidende Faktor für die Schnittstellen zwischen den einzelnen Dies in 3D-ICs. Die vertikale Nähe aktiver Dies kann zu einer schnellen Wärmeakkumulation und zu Risiken, zum Beispiel zum thermischen Durchgehen, führen. Dabei verschlechtert die kontinuierliche Wärmeentwicklung die elektrische Leistung weiter und führt zu mechanischen Belastungen durch die unterschiedlichen Wärmeausdehnungskoeffizienten verschiedener Materialien. Die Ausdehnungsdifferenz der Materialien untereinander kann sogar Dies verformen und die Zuverlässigkeit von Verbindungen gefährden.

Um prädiktive Designs zu ermöglichen, benötigt die Branche standardisierte »Multiphysik-Liberty-Dateien«, die Temperatur- und Belastungsabhängigkeiten von Chiplet-Blöcken festlegen, ähnlich wie bei den Liberty-Dateien, die im Place-and-Route-Prozess von 2D-Designs eingesetzt werden. Mit diesen Dateien können die Entwickler beurteilen, ob ein Chiplet im Stack unter den erwarteten Wärmebedingungen innerhalb seines sicheren Betriebsbereichs bleibt.

Um sicherzustellen, dass die elektrischen Modelle reale Betriebsumgebungen widerspiegeln, muss eine multiphysikalische Analyse auch die Back-Annotation von Temperatur- und Belastungsinformationen auf die einzelnen Chiplets unterstützen. Während sich die Toolchains für diesen Prozess weiterentwickeln, liegt das Ziel klar auf der Hand: umfassende, physikalisch orientierte Simulations- und Datenaustauschprozesse werden zu integralen Bestandteilen der Abnahme von 3D-IC-Designs, die einen zuverlässigen Betrieb und eine optimale Systemleistung gewährleisten.

Die Zukunft des 3D-IC-Designs gestaltet

Der Übergang zur 3D-IC-Technologie ist eine Transformationsphase der Halbleiterindustrie und verändert grundlegend die Art und Weise, wie komplexe Systeme entwickelt, verifiziert und gefertigt werden. Die 3D-IC-Technologie markiert im Bereich der Innovation von Halbleitern einen großen Schritt nach vorn. Ihr Erfolg hängt von prädiktiven, frühzeitigen multiphysikalischen Analysen und einer engen Zusammenarbeit innerhalb der gesamten Lieferkette ab. Die Festlegung gemeinsamer Standards, die Optimierung auf Systemebene und die Konzepteinführung des digitalen Zwillings werden zu höherer Leistung, Zuverlässigkeit und einer verkürzten Markteinführungszeit führen.

Pioniere des 3D-IC-Designs – darunter EDA-Unternehmen, Halbleiterhersteller und Systementwickler – nutzen einheitliche Plattformen auf Systemebene. Entwickler können damit Iterationen und multiphysikalische Analysen innerhalb einer »Single Cockpit«-Umgebung durchführen, um diese effizient für verschiedene Arten von multiphysikalischen Analysen auszuführen. Als führender Anbieter in den Bereichen 3D-IC-Methoden, Standardisierung und Tools hat Siemens kürzlich die erste echte 3D-IC-EDA-Lösung vorgestellt: Innovator3D IC. Dieses Produkt bietet Entwicklern das einheitliche integrierte Cockpit, das sie benötigen.

Im Zuge des kontinuierlichen Fortschritts bei EDA-Tools und Methoden sowie bei der Kollaboration kann die Halbleiterindustrie nun das volle Potenzial der 3D-Integration ausschöpfen – und die nächste Generation elektronischer Systeme bereitstellen, mit denen die Grenzen von Leistungsfähigkeit, Effizienz und Innovation weiter verschoben werden.

Siemens EDA Autoren

Die drei Autoren des Artikels »Multiphysikalische Effekte bei 3D-IC-Designs beherrschen«