SiC – eine Bestandsaufnahme (Teil 1)

Wie SiC-MOSFETs langfristig günstiger werden

Auch wenn die Nachfrage nach SiC-MOSFETs rasant wächst, bleiben Fragen zu den Bauteilkosten im Vergleich zu herkömmlichen Siliziumlösungen. Was steckt eigentlich hinter dem hohen Preis? Wie lässt sich dieser senken? Und wie hoch könnten die Kosten in zehn Jahren sein?

Diskrete SiC-MOSFETs für 100 A – sowohl 650-V- als auch 1200-V-Typen – kosteten mit Stand September 2021 fast genau das Dreifache wie ein äquivalenter Silizium-IGBT, obwohl der SiC-Chip drei- bis viermal kleiner ist. Der größten Kostenblock ist das Substrat, und dies wird ziemlich sicher auch noch einige Zeit so bleiben. SiC-Boules (siehe Bild oben), also der Block, aus dem die Wafer gesägt werden, müssen bei +2200 °C per Sublimationsprozess aus der Gasphase abgeschieden werden.

Hochwertige Siliziumwafer hingegen lassen sich aus meterlangen Siliziumblöcken sägen, die nach dem Czochralski-Verfahren aus einem Tiegel mit geschmolzenem Silizium bei +1500 °C gezogen werden. Somit ist das Herstellungsverfahren für Siliziumkarbid wesentlich energieaufwendiger als für Silizium, und die fertigen SiC-Boules sind gerade einmal 25 mm lang. Damit sind die Kosten für einen SiC-Wafer im Vergleich zu einem Siliziumwafer 30- bis 50-mal höher.

Weitere Faktoren, die zum höheren Preis von Siliziumkarbid beitragen, sind die Epitaxie (Aufwachsen einer hochwertigen SiC-Bauelementeschicht auf der Substratoberfläche) und die Prozessierung der Wafer. In beiden Fällen sind höhere Temperaturen und kostspieligere Verbrauchsmaterialien erforderlich als bei Silizium. Aber diese Kostenbeiträge sind im Vergleich zu den Substratkosten gering.

Der letzte Kostentreiber ist die Ausbeute (Yield) bei jedem der vorgenannten Prozessschritte. Diese Kosten ergeben sich aus der Anzahl der unbrauchbaren Wafer aus den Boules und der Anzahl der Wafer, die nach der Epitaxie und der Prozessierung aussortiert werden müssen. Der größte Einflussfaktor auf die Ausbeute ist die Materialqualität des SiC-Wafers, einschließlich der Anzahl der Defekte, die das Bauelement unbrauchbar machen und die aus den Prozessen des Boule-Wachstums und der Epitaxie stammen, aber auch die weniger offensichtlichen Defekte, die die langfristige Zuverlässigkeit beeinträchtigen. Ein weiteres Problem bei der Fertigung ist die Zuverlässigkeit des Gate-Oxids des MOSFET.

Jobangebote+ passend zum Thema

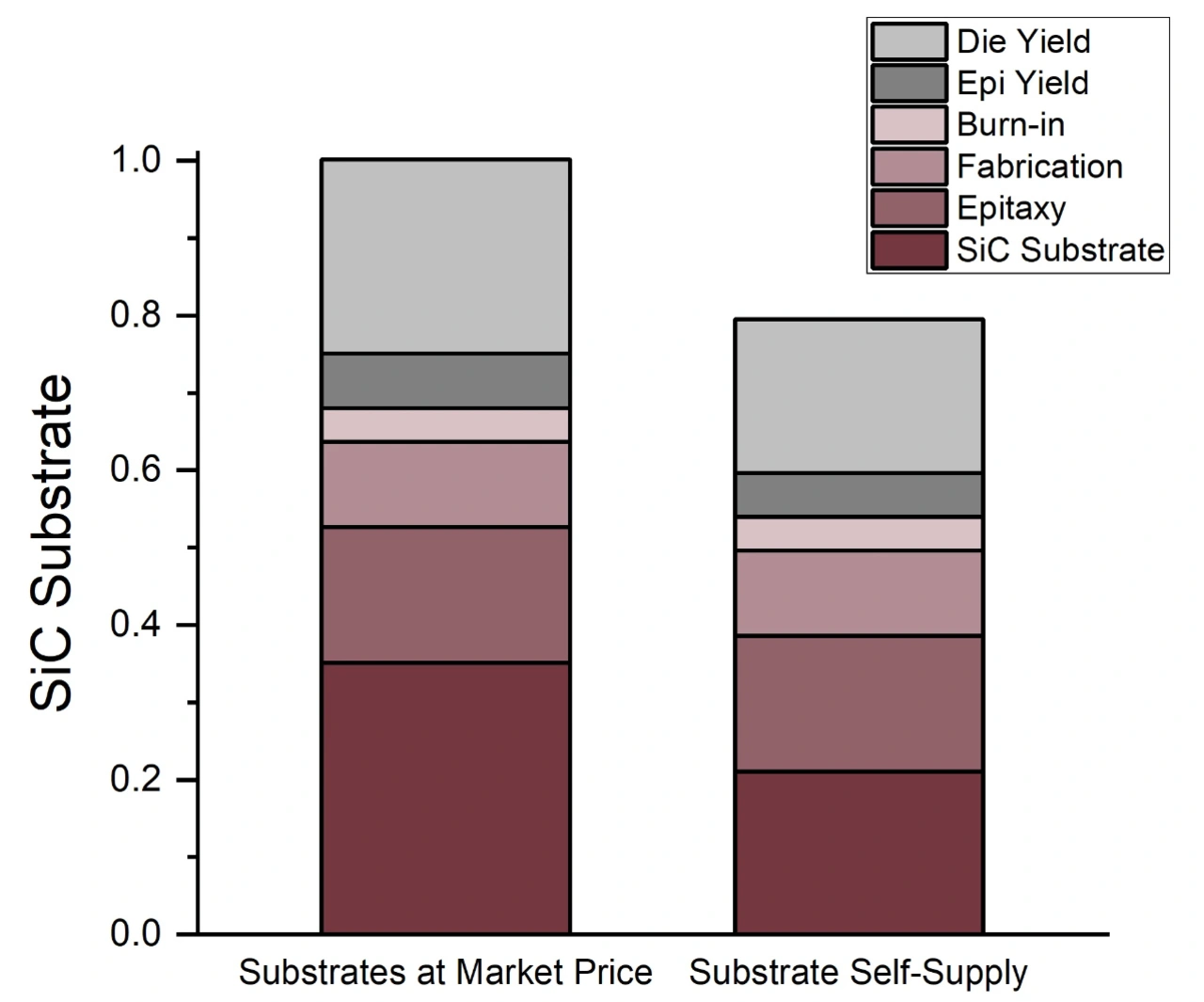

Bild 1 schlüsselt die Gesamtkosten für einen SiC-MOSFET-Die auf, wobei die Ausbeute von einem handelsüblichen MOSFET-Chip mit 1200 V/100 A aus dem Jahr 2021 stammt, hergestellt auf einem 150-mm-Substrat. Die beiden Säulen stehen für zwei unterschiedliche Modelle der Versorgung mit Substraten: zum einen die Unternehmen, die ihre Substrate zu Marktpreisen einkaufen müssen (links), zum anderen denjenigen, die vertikal integriert sind und sich daher selbst mit Substraten zu Selbstkosten eindecken können (rechts).

Umstieg auf 200-mm-Wafer senkt Kosten

Mehrere Faktoren zusammengenommen dürften dazu führen, dass der Preis für Siliziumkarbid sinkt. Aktuell werden SiC-Bauelemente vorwiegend auf Substraten mit einem Durchmesser von 150 mm gefertigt, obwohl Wolfspeed und GT Advanced Technologies (GTAT) in den nächsten sechs bis zwölf Monaten eine Migration auf 200-mm-Substrate erwarten. Dadurch lassen sich etwa 1,8-mal mehr Bauelemente pro Wafer fertigen und somit auch die Herstellungskosten pro Bauelement senken.

Allerdings dürfte der größere Durchmesser den Anteil des Substrats an den Chipkosten nicht erheblich senken, da für die Herstellung der größeren Waferfläche proportional mehr Aufwand erforderlich sein wird, um eine SiC-Boule herzustellen. Wie schon beim Übergang von 100-mm- auf 150-mm-Scheiben ist zu erwarten, dass die Substratkosten zunächst proportional zur Fläche steigen, dann aber mit zunehmender technologischer Reife und wachsendem Wettbewerb stetig sinken werden.

Zumindest in den ersten Jahren ist es daher sehr wahrscheinlich, dass ein 200-mm-Wafer mehr kostet als sein 150-mm-Pendant. Dies liegt daran, dass es eine große Herausforderung ist, auf eine neue Wafergröße zu optimieren, und dass die Ausbeute an Wafern (beeinflusst durch die Homogenität und Durchbiegung eines Wafers), bei der Epitaxie und bei der Prozessierung beeinträchtigt werden könnte.

Wie der Übergang von 100 mm auf 150 mm gezeigt hat, stieg die Dichte beider Arten von Defekten zumindest anfangs sprunghaft an. Auch gibt es immer noch Belege dafür, wenn man weiß, wo man suchen muss: Auf ihrer SiC-Webseite erklärt der Wafer-Hersteller SK Siltron, dass die Anzahl der Defekte aller Art bei diesem Übergang um 100 bis 200 Prozent gestiegen ist. Nach einer kurzen Entwicklungsphase dürfte die Fehlerdichte bei 200-mm-Wafern wieder sinken, ebenso wie die Produktionskosten; bis dahin dürften 150-mm-Wafer die wirtschaftlichere Lösung bleiben, und der Übergang zwischen diesen beiden Wafer-Durchmessern dürfte in den ersten Jahren fließend vonstattengehen.

Der Umstieg auf 200 mm macht neue, moderne Fertigungsstätten erforderlich, wofür die Mohawk Valley Fab von Wolfspeed ein gutes Beispiel ist. Dies wird dazu führen, dass der Automatisierungsgrad wesentlich zunimmt, die Zahl der hochqualifizierten – und damit teuren – Ingenieure, die für den reibungslosen Betrieb der Anlage benötigt werden, erheblich sinkt, und damit auch die Fertigungskosten. Kurzfristig ist jedoch damit zu rechnen, dass die Abschreibungskosten aufgrund der erheblichen Ausgaben steigen werden.

Vertikal integrierte Unternehmen haben Kostenvorteile

Die Selbstversorgung mit Substraten innerhalb »vertikal integrierter« Unternehmen beeinflusst die Kosten erheblich. Dies zeigt die linke Säule in Bild 1, in dem die Kosten für ein Substrat um die Gewinnspanne des Verkäufers bereinigt wurden, die hier mit 40 Prozent veranschlagt worden ist. Dies wirkt sich sowohl auf die Ausbeute- als auch auf die Materialkosten aus, denn das gesamte aussortierte Material ist 40 Prozent weniger wert.

Da sich nur wenige Chiphersteller vollständig selbst mit Substraten versorgen können, verschafft dies denjenigen einen Wettbewerbsvorteil, die dazu in der Lage sind. Die im August 2021 angekündigte Übernahme von GTAT durch onsemi zeigt, dass die Konsolidierung in diesem Bereich noch nicht abgeschlossen ist. Einige kleine Unternehmen, die über ein bedeutendes Maß an geistigem Eigentum verfügen, sind nach wie vor von den großen Unternehmen unabhängig und machen den Löwenanteil des Geschäfts aus.

Wie Ende Juni 2021 bekannt wurde, steigert auch China sein Interesse an Siliziumkarbid. Dabei handelt es sich jedoch nicht um den PV-Markt, und es ist nicht möglich, den Markt mit billigem, minderwertigem Material zu überschwemmen. Stattdessen wird es für jeden neuen Marktteilnehmer einige Zeit dauern, bis er die von der Automobilindustrie und anderen Branchen geforderte Kristallqualität und Konsistenz erzielt.

Ein letzter wichtiger Aspekt ist die Weiterentwicklung der SiC-Bauteiltechnologie. Insbesondere Fortschritte in der Bauteilgestaltung und -fertigung dürften den Widerstand eines SiC-MOSFET mit jeder neuen Generation weiter verringern. Nach Angaben von Wolfspeed sank der flächenbezogene Widerstand, also der spezifische Durchlasswiderstand, mit jeder Bauteilgeneration um etwa 40 Prozent. Damit werden bei gleichem Nennstrom die Chipfläche und das Chipvolumen kleiner. Zusätzlich erhöhen kleinere Chips nicht nur die Anzahl der Bauteile pro Wafer, auch die prozentuale Ausbeute steigt.

Allerdings wird das Wärmemanagement dadurch immer wichtiger, denn die Chipfläche A skaliert nicht linear mit dem elektrischen und thermischen Widerstand, sondern proportional zur Quadratwurzel (A∝√(RDS(on) · Rth) [1]. Demnach verkleinert sich die aktive Chipfläche bei einer Halbierung des Widerstands lediglich um 29 Prozent. Inaktive Bereiche (z. B. Gate-Pads und Anschlüsse) skalieren nicht im gleichen Maß.

Kostenprognose für SiC

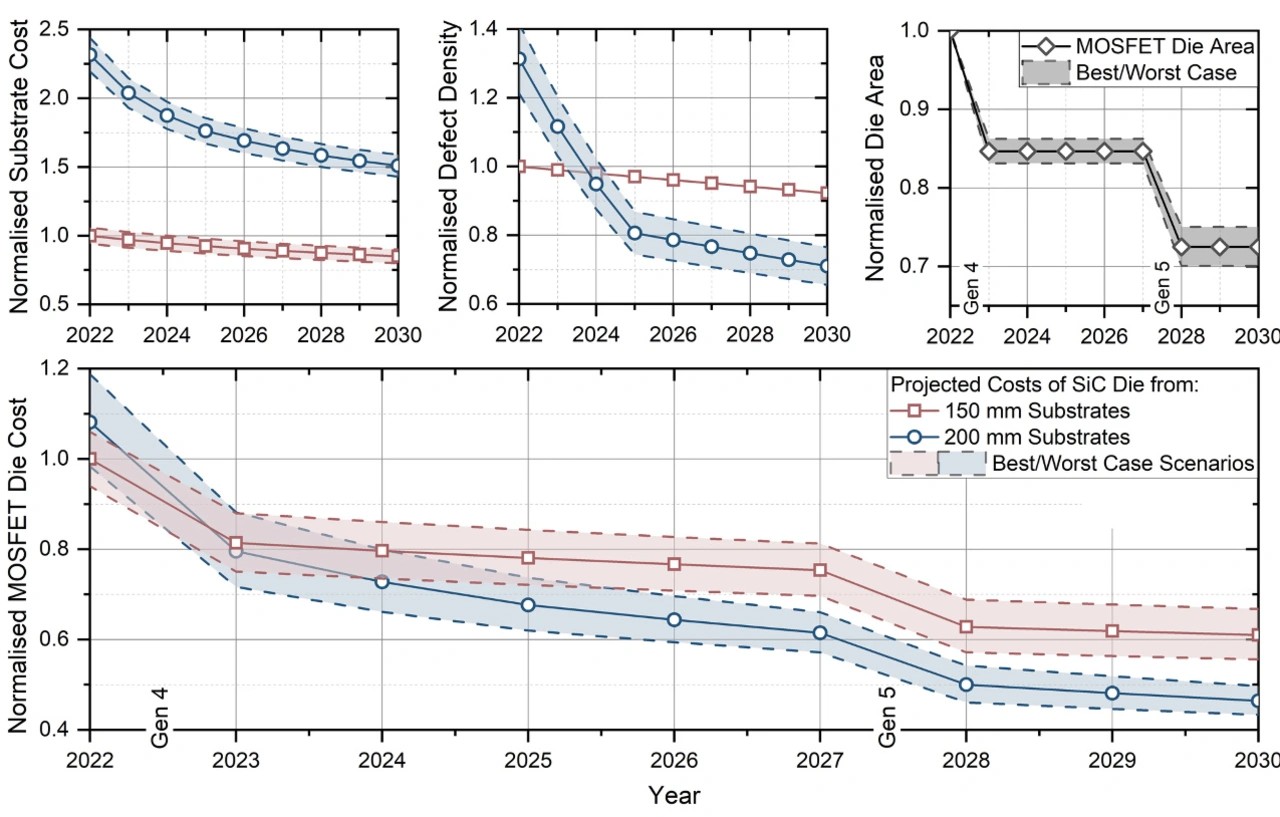

Ausgewählte, normalisierte Ergebnisse aus dem SiC-Kostenprognosemodell von PGC Consultancy sind in Bild 2 dargestellt. Wichtiger, als zu versuchen, die künftigen Bauelementekosten exakt vorherzusagen, ist es, herauszufinden, welche der zuvor identifizierten Kostentreiber am stärksten dazu beitragen können, die Kosten zu senken. Hierbei handelt es sich um eine Untersuchung der Auswirkungen der 200-mm-Technologie im Vergleich dazu, wie sich eine kontinuierliche Verbesserung des Bauteildesigns auswirkt. Dargestellt sind drei der Eingangsgrößen des Kostenmodells (Substratkosten, Defektdichte und Chipfläche) und die prognostizierten Ausgangsgrößen, die alle auf bekannte oder geschätzte Werte für 150 mm im Jahr 2022 normiert sind.

Die Substratkosten zu projizieren ist von zentraler Bedeutung, da sie die Gesamtkosten dominieren. Für 200-mm-Substrate dürften die Kosten pro Flächeneinheit geringfügig höher sein als für 150-mm-Substrate. Allerdings werden sie jährlich schneller sinken als bei 150-mm-Substraten, wie es beim Übergang von den 100- zu den 150-mm-Substraten der Fall war.

Höhere Defektdichte bei Migration auf 200-mm-Wafer

Eine höhere Defektdichte, die sich auf die Ausbeute bei der Epitaxie auswirkt, scheint unausweichlich zu sein. Dies zeigte sich bereits beim Migrieren von 100- zu 150-mm-Wafern. Wie hoch die Defektdichte ansteigt und wie schnell sie wieder abnimmt, ist strittig. Nicht dargestellt ist, dass die Ausbeute an Dies einen ähnlichen Trend aufweisen könnte, da neue Prozesse eingeführt und inkrementell verbessert werden.

Die letzte Eingangsgröße ist die Chipgröße, ein Wert, der sich auf beide Wafergrößen gleichermaßen auswirkt und davon abhängt, wie stark der Durchlasswiderstand in jeder neuen MOSFET-Generation sinkt. Zwei neue Generationen (Gen 4 und 5) werden für die Jahre 2022 und 2027 prognostiziert, wobei jede Generation im Basisszenario jeweils 45 Prozent, im ungünstigsten Fall 40 Prozent und im besten Fall 50 Prozent weniger Widerstand aufweist. Wie bereits erwähnt, nimmt die Fläche proportional zur Quadratwurzel des Widerstands ab, sodass eine Reduzierung des Widerstands um 40 bis 50 Prozent die aktive Fläche des Bauelements um 23 bis 29 Prozent verringert. Die anfängliche Chipgröße basiert auf einem marktführenden MOSFET für 1200 V/100 A (Stand: September 2021).

Das Ergebnis sind die prognostizierten Kosten für einen MOSFET-Chip mit 1200 V/100 A auf einem 200-mm- und einem 150-mm-Substrat, wobei jeweils das Basisszenario sowie das optimale und das schlechteste Szenario dargestellt sind.

Projektion der Kosten

Unter den getroffenen Annahmen deutet die Modellrechnung darauf hin, dass die Kosten für einen MOSFET-Chip mit 1200 V/100 A, der auf einem 200-mm-Substrat hergestellt wird, im Jahr 2030 um 54 Prozent niedriger sein könnten im Jahr 2022 bei einem 150-mm-Substrat. Im günstigsten Fall sinkt der Preis um 57 Prozent, im ungünstigsten Fall nur um 50 Prozent. Der Marktpreis eines IGBTs für 1200 V/100 A ist heute dreimal niedriger als der eines gleichwertigen SiC-MOSFETs, und obwohl der Preis für einen Silizium-IGBT in diesem Zeitrahmen nicht unverändert bleiben wird, werden die SiC-Kosten im Rahmen unserer Berechnungen so stark sinken, dass der Abstand zu Silizium deutlich geringer wird.

Außerdem dürfte eine Umstellung auf 200-mm-Substrate nicht dazu führen, dass die SiC-Kosten unmittelbar drastisch sinken. Tatsächlich ist in jedem von PGC durchgespielten Szenario davon auszugehen, dass anfangs ein Aufpreis bei der Verwendung von 200-mm-Substraten zu zahlen ist, bis die Ausbeute bei Wafern und Chips wieder das Niveau der 150-mm-Wafer erreicht haben wird. Dies dauert jedoch möglicherweise nur wenige Jahre, bis sich die Vorteile der größeren Substrate bezahlt machen.

Vielleicht ist das Basisszenario aber auch zu negativ. Eventuell werden die umfangreichen unternehmensinternen Studien, die seit der ersten Demonstration von 200-mm-Substraten im Jahr 2015 laufen, verhindern, dass die Fehlerdichte genauso sprunghaft ansteigt wie beim Übergang von 100- zur 150-mm-Wafern. Wolfspeed geht davon aus, dass dies in ihrem Fall zutrifft, wobei sie eine Pilotlinie eingerichtet haben, um einen ersten 200-mm-Fertigungsprozess zu etablieren. Das Best-Case-Szenario für 200-mm-Wafer deckt diese Möglichkeit ab, wobei die Chipkosten bei der Markteinführung in etwa denen von 150-mm-Wafern entsprechen, bevor 200-mm-Wafer in den darauffolgenden Jahren billiger werden.

Unabhängig von der Ausgangslage bei den 200-mm-Substraten können bis 2030, wenn die Rechenmodelle die Unterschiede zwischen den verschiedenen Substratdurchmessern ausgeglichen haben, den Flächenunterschied mit Faktor 1,8 zwischen den Substraten voll nutzen können. Im Basisszenario wird ein Chip aus einem 200-mm-Substrat im Vergleich zu einem Chip aus einem 150-mm-Substrat 31 Prozent preiswerter sein.

In den Szenarien wirken sich größere Substratdurchmesser ähnlich stark auf die Kosten aus wie technologische Fortschritte. Die zwei Bauteilgenerationen der letzten zehn Jahre haben dafür gesorgt, dass die Chipkosten um 27 Prozent gesunken sind, ±2,5 Prozent in den Szenarien für den besten und schlechtesten Fall. Daher sind die fortgesetzten marginalen Leistungssteigerungen, die die Bauelementedesigner durch Innovationen wie die Dünnung der Wafer, Trench-Architekturen oder die Verringerung der Prozessknoten erzielen, für die Kostensenkung äußerst wichtig.

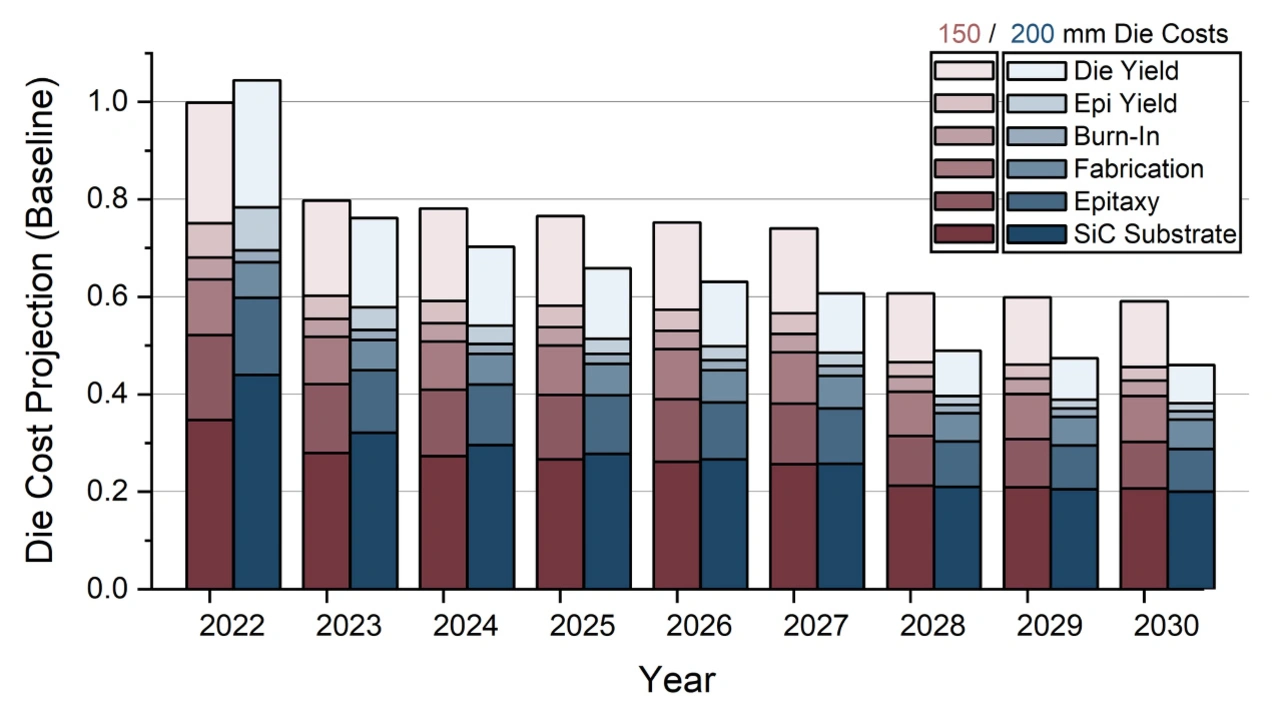

In Bild 3 werden die Basisergebnisse erweitert, um deren Beiträge im Laufe der Jahre zu berücksichtigen. Zu erkennen ist, wie sich die Ausbeute bei den frühen 200-mm-Wafern verschlechtert, was zu Beginn ihrer Einführung einen großen Anteil ausmacht. Bis 2030 werden die niedrigeren Fertigungskosten pro Die der größeren 200-mm-Substrate in den Daten deutlich sichtbar.

Fazit

In der gesamten Branche geht es vorrangig darum, die Konkurrenzfähigkeit von Siliziumkarbid (SiC) auf der Kostenseite zu verbessern, doch eine kurzfristige Lösung dafür gibt es nicht. Die Einführung von 200-mm-Wafern wird langfristig erheblich dazu beitragen, dass sich die Fertigungskosten auf eine bis zu 1,8-mal mehr Bauelemente verteilen. Allerdings wird es einige Zeit dauern, bis die Substrate die heute möglichen Werte für Qualität und Ausbeute der 150-mm-Wafer erreichen. Die Modellierung zeigt, dass es ebenso wichtig ist, die Technologie mit jeder Bauteilgeneration schrittweise zu verbessern. Ein geringerer Durchlasswiderstand führt zu einer kleineren Chipfläche, was die Anzahl der Chips pro Substrat und letztendlich die Ausbeute erhöht.

Selbst bei unseren konservativsten Vorhersagen deuten beide Effekte – die Einführung von 200-mm-Substraten und zwei Generationen von verbesserten Bauelementen – darauf hin, dass sich die Kosten für einen SiC-MOSFET bis 2030 gegenüber heute halbieren werden. Bei einem Kostenunterschied um den Faktor 3 zu gleichwertigen Silizium-IGBTs wäre dies eine positive Entwicklung.

Referenz

[1] W.J. Sung and B.J. Baliga, Design and Economic Considerations to Achieve the Price Parity of SiC MOSFETs with Silicon IGBTs, DOI: 10.4028/www.scientific.net/MSF.858.889