Neue Architektur für Halbleiter-Designs

On-Chip-Sicherheit für die Medizin

Vertrauenswürdige Plattform-Chips für vernetzte Medizingeräte: Das Barkhausen Institut hat ein »Netzwerk on Chip« entwickelt, das einzelne Halbleiterkomponenten über Wächtereinheiten verbindet – für höchste Sicherheit, eine flexible Entwicklung sowie individuelle Medizin-Chips in Massenfertigung.

Die Digitalisierung gilt als einer der größten Treiber für die Medizintechnik und die Gesundheitsversorgung der Zukunft: Verbesserungen bei Diagnose und Behandlung sind zunehmend an Software und entsprechende digitale Hardware geknüpft. Medizingeräte für den Einsatz direkt am oder nahe dem Patienten stellen Medtech-Hersteller, deren Elektronikzulieferer und die Ingenieure und Entwickler vor vielfältige Herausforderungen. Digitale Halbleiterchips für diagnostische und therapeutische Geräte in den Behandlungsräumen müssen den zahlreichen Anforderungen des medizinischen Alltags, allen geltenden Normen und Zertifizierungen wie auch hohen Sicherheitsaspekten genügen.

Spannungsfelder für digitale Hardware

Als »Always-On«-Devices mit Cloud-Anbindung müssen (künftige) Medizingeräte auf der einen Seite sehr sicher, aber auch energieeffizient und thermisch stabil sein – was gerade bei den für KI benötigten rechenstarken Prozessoren eine Herausforderung darstellt. Für digitale Chips in Medizingeräten gelten daher drei entscheidende Spannungsfelder:

- Rechenleistung und Stromverbrauch

- Maßanfertigung und Kosteneffizienz

- Flexibilität und Sicherheit

Power versus Processing

Die von der Hardware bereitgestellte Rechenleistung und auch die Kommunikationsfähigkeiten über drahtgebundene oder drahtlose Schnittstellen entscheiden darüber, welche Anwendungsfälle mit einem Chip umsetzbar sind. Dafür enthalten die Chips Prozessoren und andere Recheneinheiten zum Ausführen von Programmen, aber auch Techniken wie Mobilfunk oder WLAN für die Kommunikation mit der Außenwelt. Ein Mehr an Rechenleistung auf Chip-Ebene ermöglicht fortschrittlichere Programme, allerdings zum Preis eines erhöhten Stromverbrauchs. Batteriebetrieb und Hitzeentwicklung von tragbaren oder gar im Körper einsetzbaren Produkten setzen dem Stromverbrauch enge Grenzen.

Customized Chip-Sets aus Serienproduktion

Die Vielfalt von aktuellen oder in Zukunft denkbaren Medizingeräten erfordert jeweils auf den Anwendungsfall zugeschnittene Chip-Fähigkeiten. Einer separaten Maßanfertigung für jedes Gerät steht jedoch die Kosteneffizienz entgegen. Chip-Fertigung wird erst bei sehr großen Stückzahlen kosteneffektiv, daher sind dedizierte Chips für Medizingeräte mit geringen Seriengrößen wirtschaftlich nicht tragbar. Insbesondere zur einmaligen Verwendung am Patienten konzipierte Wegwerf-Geräte müssen jedoch günstig herzustellen sein, um das Gesundheitssystem nicht unnötig zu belasten.

On-Chip-Security

Ein drittes Spannungsfeld eröffnet sich zwischen der Flexibilität durch Aktualisierung von Software und der Zertifizierbarkeit und Sicherheit der Geräte. Software ist schnelllebig, und in digitalen Produkten können neue Erkenntnisse und Funktionen prinzipiell durch Aufspielen einer neuen Version der Software umgesetzt werden. Auch im Medizinbereich wäre es aus Kosten- und Nachhaltigkeitsgründen wünschenswert, wenn ein kostspielig entwickeltes und beschafftes Gerät durch neue Software-Versionen aktuell gehalten und damit länger genutzt werden kann. Allerdings unterliegen Medizingeräte Regulierungen, welche oftmals eine Zertifizierung voraussetzen. Eine Aktualisierung der Software würde dann eine erneute Zertifizierung erfordern, was wiederum die Kosten in die Höhe treibt. Diese regulatorischen Prozesse sind jedoch eine Grundlage des Vertrauens, welches Patienten in die verwendete Technik setzen.

Chip-Architektur für alle Medizinszenarien

Angewandt auf die drei Spannungsfelder eröffnen sich Ansätze für Lösungen: Das Bereitstellen von hoher Rechenleistung erfordert die Integration von leistungsstarken Prozessoren auf dem Chip. Um den Stromverbrauch zu senken, werden diese Prozessoren von Beschleuniger-Einheiten bei bestimmten Teilaufgaben unterstützt. Solche Beschleuniger sind auf konkrete Teilschritte wie Bildverarbeitung, Signalaufbereitung oder künstliche Intelligenz spezialisiert und bearbeiten diese Schritte mit einer höheren Energieeffizienz als Standardprozessoren. Ein offenes Problem ist dabei die Verknüpfung von Standardprozessoren und Beschleunigern, so dass diese ohne Datentransfer- und Kommunikationsverluste möglichst reibungslos zusammenarbeiten können.

Baukasten-Prinzip für Wunsch-Konfiguration

Medizingeräte für unterschiedliche Anwendungsfälle werden jedoch unterschiedliche Beschleuniger benötigen. Eine individuelle Chip-Fertigung für jedes Gerät, angepasst an dessen spezifisches Anwendungsgebiet, würde zu einer stark fragmentierten Chip-Landschaft führen. Dies hätte zur Folge, dass jede Serie nur in kleinen Stückzahlen produziert werden könnte – ein ineffizienter und kostspieliger Ansatz. Stattdessen bietet sich die Entwicklung universeller Chip-Designs an, die als Baukasten fungieren und verschiedene Beschleuniger sowie Prozessoren integrieren. Für eine spezifische Anwendung wird dann lediglich eine Teilmenge dieser Bausteine aktiviert. Dieser modulare Ansatz ermöglicht nicht nur eine effizientere Großserienfertigung und damit Kostensenkungen, sondern gewährleistet auch Flexibilität für unterschiedliche Einsatzbereiche. Dabei ist es essenziell, dass ungenutzte Chip-Komponenten weder die Funktionalität beeinträchtigen noch Sicherheitsrisiken darstellen.

Bleibt zuletzt das Problem der Flexibilität durch Software-Updates. Im Sinne der Zukunftsfähigkeit und Langlebigkeit von Geräten sind solche Updates wünschenswert. Im Sinne der Zertifizierung muss jedoch sichergestellt werden, dass Kerneigenschaften des Medizingeräts unverändert über alle Updates hinweg erhalten bleiben. So kann zum Beispiel in einem Endoskop die Bildverarbeitung durch ein Update verbessert werden, aber die Betriebssicherheit des Geräts und die Vertraulichkeit der Patientendaten müssen stets gewahrt bleiben. Dafür muss eine Chip- und Betriebssystem-Architektur geschaffen werden, die es erlaubt unveränderliche und veränderliche Bestandteile so zu kombinieren, dass die Unveränderbarkeit der Kerneigenschaften gesichert ist und im Rahmen einer Zertifizierung überprüft werden kann.

Medizinsichere Chip-Architektur M³

Das Dresdner Barkhausen Institut hat unter dem Projektnamen M³ vertrauenswürdige Plattform-Chips und einen neuen Architekturansatz für das medizinische Chip-Design entwickelt, der als Brücke zwischen Sicherheit, Kommunikation und Halbleitertechnik die Anforderungen vernetzter Digital-Health-Systeme widerspiegelt. Die Grundprinzipien entstammen der Welt der Betriebssysteme, speziell der Mikrokernsysteme.

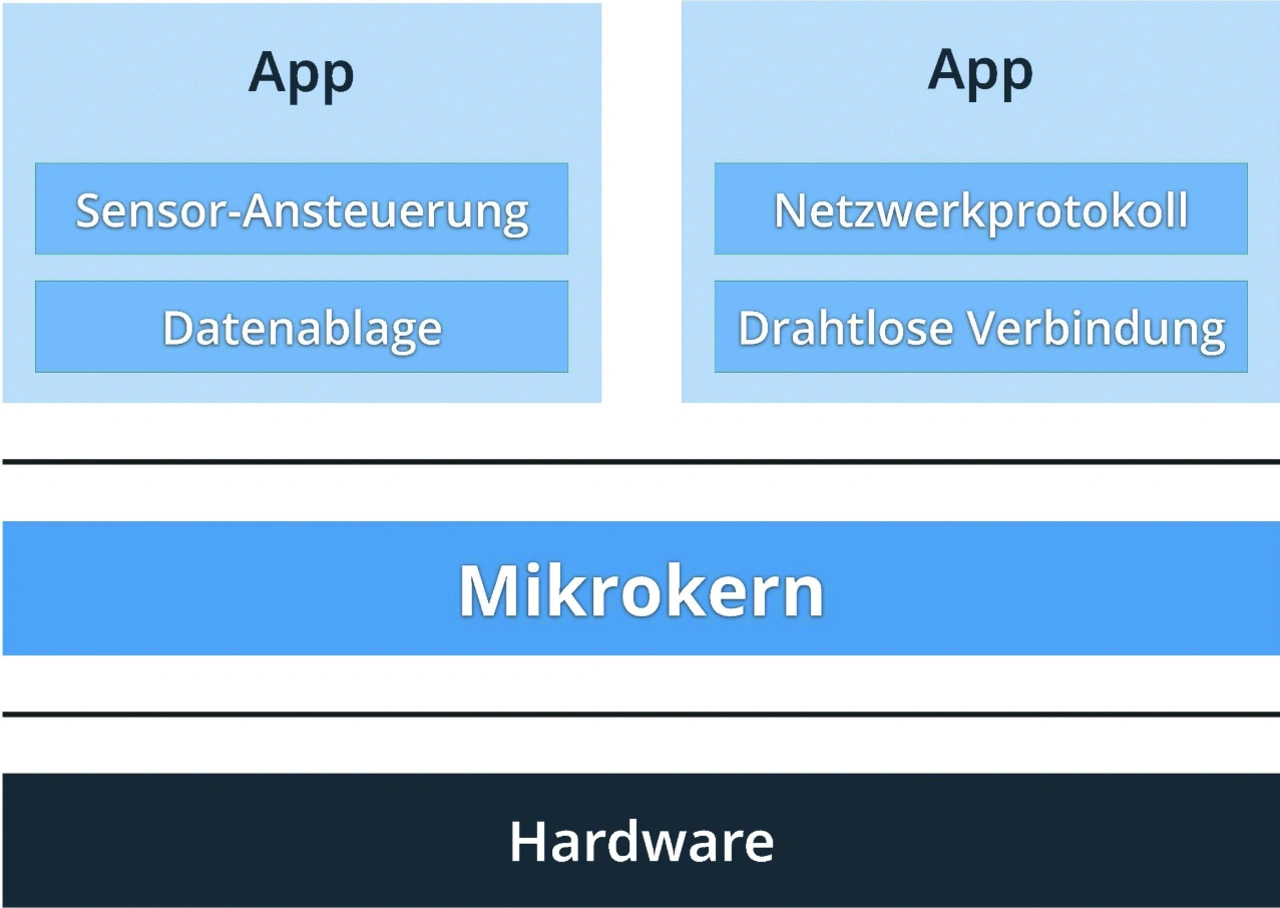

Betriebssysteme dienen allgemein als Verwaltungseinheit, welche die von der Chip-Hardware bereitgestellte Rechenkapazität an darauf laufende Programme zuteilt. Bekannte Betriebssysteme wie Windows und Linux bieten darüber hinaus eine große Palette an weiteren Funktionen, über Datenhaltung und Netzkommunikation bis zur Ansteuerung einer grafischen Oberfläche. Diese umfangreichen Funktionen erweitern die Angriffsfläche des Systems um ein Vielfaches.

Die Idee eines Mikrokernsystems ist es, die Aufgaben des Betriebssystems auf seine Kernaufgabe des Bereitstellens von Rechenkapazität zu reduzieren. Dadurch verringert sich die Angriffsfläche um ein Vielfaches. Zusatzfunktionen wie Kommunikation, Datenhaltung und grafische Ausgabe müssen dann zwar auf Anwendungsebene realisiert werden, die Isolation verschiedener Programme auf einem Mikrokernsystem wird durch die geringere Angriffsfläche aber verbessert. Die Robustheit gegenüber Programmierfehlern und die Sicherheit gegenüber digitalen Angriffen steigen. Es entsteht ein System mit dem Mikrokern als einer widerstandsfähigen und überprüfbaren Isolationsschicht und den Programmen, die so voreinander geschützt sind, dass Fehler in einem Programm ein anderes nicht beeinflussen können.

Mikrokernsystem für Halbleiter-Chips

Das Konzept des Mikrokerns ist seit den 1970er-Jahren bekannt und wird heute in Anwendungsbereichen mit höchsten Sicherheitsanforderungen industriell genutzt. Der Forschungsansatz der M³-Plattform des Barkhausen Instituts ist es, dieses Konzept auf eine Chip-Architektur zu übertragen. In herkömmlichen Hardware-Architekturen werden die verschiedenen, auf einem Chip integrierten Prozessoren und Beschleuniger durch Zugriff auf gemeinsamen Speicher miteinander verbunden. Dabei muss der gesamten Hardware vollständig vertraut werden. Sobald sich in die Implementierung eines Prozessors oder Beschleunigers ein Fehler einschleicht, kann darüber Vollzugriff auf das gesamte System erlangt werden. In den letzten Jahren sind solche Hardware-Fehler wiederholt aufgetreten. Das ist im Sinne der Sicherheit gegenüber Angriffen aber auch bezüglich der Robustheit des Systems keine tragfähige Lösung.

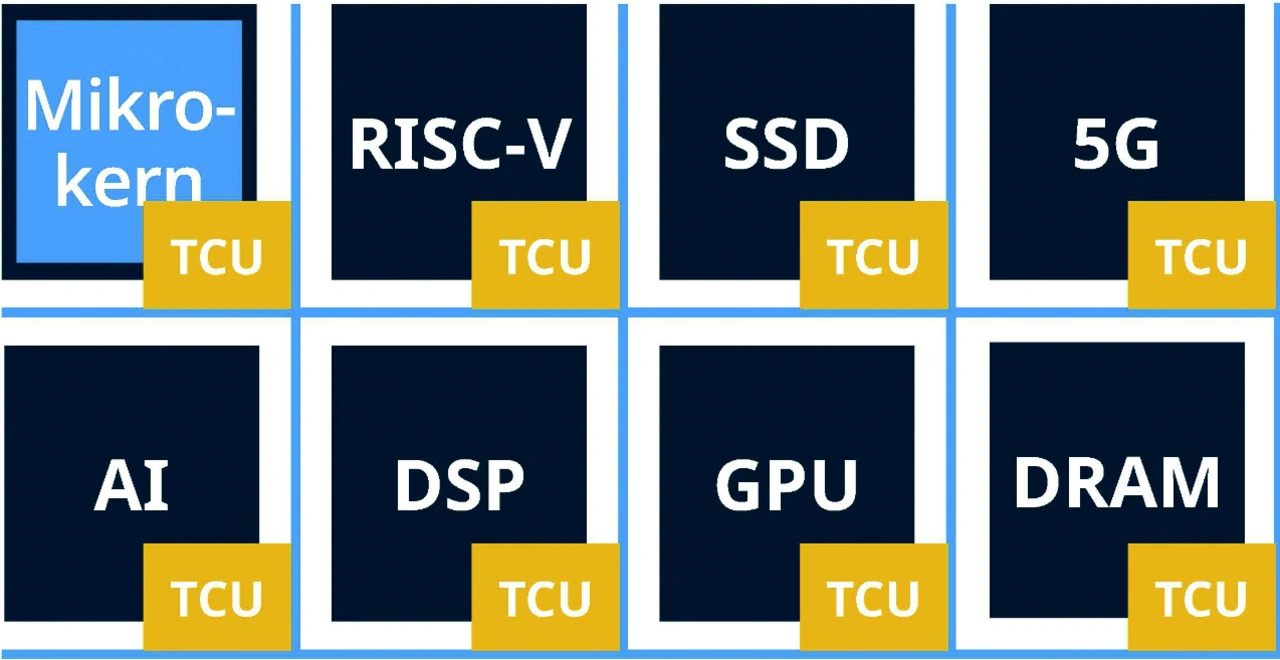

Wächterfunktion: Trusted Communication Unit

Die M³-Plattform begegnet dieser Problematik mit einer neuartigen Chip-Architektur. Dabei werden Prozessoren und Beschleuniger auf dem Chip in separaten Kacheln angeordnet. Über ein Chip-Netzwerk können diese Kacheln miteinander kommunizieren. Dabei ist zwischen diesem Netzwerk und jeder einzelnen Kachel eine Wächterkomponente namens Trusted Communication Unit (TCU) geschaltet. Diese TCU ist als Hardware-Firewall dafür zuständig, nur solche Kommunikationswege zuzulassen, die explizit als erwünscht freigeschaltet wurden. Dadurch können die einzelnen Kacheln zielgerichtet miteinander kommunizieren. Unerlaubte Kommunikation, die durch einen Fehler oder Angriff induziert sein könnte, wird aber abgeblockt. Dadurch ergibt sich, ähnlich zum Mikrokernsystem, eine Chip-Architektur mit der TCU als einer gehärteten und überprüfbaren Isolationsschicht, welche die Kacheln so voreinander schützt, dass Fehler in einem Prozessor oder Beschleuniger den Rest des Systems nicht beeinflussen können. Der geringe Mehraufwand, der durch die Kommunikation über TCUs entsteht, kann in den meisten praktischen Anwendungsfällen vernachlässigt werden.

Sichere Integration und individuelle Verschaltung

In Bezug auf die genannten Spannungsfelder ermöglicht M³ damit die sichere Integration von Prozessoren und Beschleunigern, was zu hoher Energieeffizienz beiträgt. Die einzelnen Kacheln lassen sich flexibel kombinieren, so dass ein Plattform-Chip mit einem Baukasten an Prozessoren und Beschleunigern ausgestattet werden kann. Ein solcher Chip lässt sich kostengünstig in großer Stückzahl fertigen und wird folgend für eine konkrete Anwendung spezialisiert, indem nur die für den Anwendungsfall benötigten Kacheln über die TCUs miteinander verschaltet werden. Die TCUs ermöglichen dabei eine Abgrenzung von Programmbestandteilen, so dass diese auch einzeln aktualisiert werden können. Zentrale Komponenten für die Betriebssicherheit können dabei unverändert belassen werden, so dass kritische Eigenschaften überprüfbar erhalten bleiben.

Plattform-Chips auf Basis der M³-Architektur können nach Ansicht des Barkhausen Instituts damit eine Vielzahl neuer digitaler Halbleitersysteme für Medizingeräte erschließen. Die Dresdner Forschenden arbeiten in zahlreichen wissenschaftlichen Projekten daran, die M³-Architektur weiter zu verbessern. Sowohl die Software als auch die Hardware stehen anderen Forschenden und der Industrie als Open Source zur Verfügung. Der Vorteil der Architektur liegt dabei auch in ihrer hohen Fehlertoleranz. Sollte in einer Kachel ein Problem auftreten, bleibt dieses auf die betroffene Einheit beschränkt. Für die Fehlersuche muss zudem nur die relevante Kachel überprüft werden. Dieser modulare Ansatz verspricht somit, die Sicherheit und Zuverlässigkeit medizinischer Hardware sowie die Vertrauenswürdigkeit zukünftiger vernetzter Medizingeräte signifikant zu verbessern. (uh)