Abkündigung von 6-Zoll-CMOS-Wafern

Produktion auf 8-Zoll-Wafern ist zukunftssicher

Die Abkündigung von 150-mm-CMOS-Wafern stellt ein Risiko dar. Unternehmen, die auf ASICs angewiesen sind, die bisher auf 150-mm-Wafern gefertigt wurden, müssen jetzt handeln, um ihre Versorgung zu sichern, Engpässe beim Redesign zu vermeiden und ihre Differenzierung auf Systemebene zu wahren.

Hersteller elektronischer Produkte und Systeme sind auf eine zuverlässige Versorgung mit ICs angewiesen. Dies gilt insbesondere in Branchen mit langen Produktlebenszyklen wie der Automobilbranche, dem Maschinenbau, der Medizin-, Luft- und Raumfahrttechnik. Käufer von Halbleiterbauelementen vertrauen gerade hier auf eine stabile Versorgung mit Computerchips. Einige Foundries haben jedoch im letzten Jahr angekündigt, die Produktion von 150-mm-/6-Zoll-CMOS-Wafern einzustellen. Dadurch gerieten einige ihrer Kunden in eine schwierige Lage, weil ihre Lieferketten gefährdet wurden. Entwicklungsingenieure mussten sich darauf konzentrieren, Engpässe zu vermeiden, statt an neuen Produkten zu arbeiten.

Um die Gesamtsituation zu verstehen, muss man sich die Entwicklung der Halbleitertechnologie vergegenwärtigen. Parallel zur Verkleinerung der Prozessknoten wurden die Wafer-Durchmesser von 150 mm (6 Zoll) auf 200 mm (8 Zoll) und schließlich auf 300 mm (12 Zoll) erhöht. Neben dem Mooreschen Gesetz hat diese Vergrößerung entscheidend dazu beigetragen, die steigende Nachfrage nach ICs zu befriedigen und die Kosten zu senken. Während 300-mm-Wafer für fortschrittliche Knoten (<90 nm) zum Standard geworden sind, werden viele Analog- und Mixed-Signal-Chips immer noch auf 150-mm-Wafern mithilfe ausgereifter Knoten wie 0,6 µm (Tabelle 1) gefertigt.

Jobangebote+ passend zum Thema

| Wafergröße | 150 mm (6 Zoll) | 200 mm (8 Zoll) | 300 mm (12 Zoll) |

|---|---|---|---|

| Einführungsjahr | 1983 | 1992 | 1999 |

| Prozessknoten | 1,5 µm – 0,6 µm | 0,6 µm – 90 nm | 90 nm – 2 nm |

Die Halbleiterprozessknoten haben sich im Laufe der Zeit verkleinert

Während 300-mm-Wafer für fortschrittliche Technologieknoten seit mehr als zwei Jahrzehnten Standard sind, wird es zunehmend schwieriger, die Produktion von CMOS-Prozessen auf 150-mm-Wafern aufrechtzuerhalten. Mit dem Rückgang der Produktionsmengen von 150-mm-Wafern ist die Beschaffung direkter und indirekter Materialien schwieriger und teurer geworden. Gleichzeitig wurde die Wartung der Anlagen komplexer und damit auch kostspieliger. Weil diese Kosten nicht mehr an die Kunden weitergegeben werden konnten, sahen sich viele Foundries gezwungen, die Produktion von 150-mm-Wafern einzustellen.

Dies führte zur Abkündigung der Prozesse mit Strukturbreiten von 0,6 µm und größer und stellte Hersteller in den Bereichen Automotive, Industrie-, Medizintechnik und anderen Branchen vor Herausforderungen. Diese ausgereiften Knoten werden nach wie vor häufig für Analog- und Mixed-Signal-ICs verwendet, darunter Sensorschnittstellen und Power-Management-ICs (PMICs). Für viele Entwicklungsteams kam die plötzliche Ankündigung des Endes der Lebensdauer (EOL) von CMOS-Chips auf 150-mm-Wafern ohne große Vorwarnung. In einigen Fällen löste die Ankündigung dringenden Handlungsbedarf aus, um Lagerbestände zu evaluieren, Neudesigns einzuleiten und über viele Jahre gefertigte Systeme neu zu validieren.

Gemäß dem JEDEC-Standard J-STD-048 – dem Benachrichtigungsstandard für Produktabkündigungen – haben Kunden ab der Ankündigung sechs Monate Zeit, letzte Bestellungen (Last-Time-Buy-Orders) aufzugeben. Nach Ablauf dieser Frist bleiben den Foundries zwölf Monate, um diese Bestellungen abzuarbeiten und auszuliefern. Dieser enge Zeitrahmen setzt Unternehmen erheblich unter Druck, die Kundennachfrage schnell zu bewerten, letzte Käufe zu sichern und mit der Planung von Ersatzprodukten zu beginnen. In vielen Fällen besteht die einzige praktikable Lösung darin, die betroffenen integrierten Schaltkreise auf einen neuen Prozessknoten zu migrieren – ein Aufwand, der sowohl technische als auch geschäftliche Überlegungen erfordert, insbesondere bei der Entwicklung eines kundenspezifischen ASICs.

Diese Überlegungen beginnen mit einer Bewertung der Wirtschaftlichkeit. Ein ASIC sollte eine einzigartige Lösung bieten, die Systemkosten, Leistungsfähigkeit und Leiterplattenfläche optimiert und durch einen höheren Integrationsgrad einen Mehrwert schafft. Im Rahmen einer technischen Bewertung müssen geeignete Technologien identifiziert, deren verfügbare Eigenschaften bewertet und die Kosten für Prototypen- und Produktionswafer analysiert werden. Schließlich muss ein Foundry-Partner ausgewählt werden, der über einschlägige Erfahrung, Liefertreue, einen geeigneten Produktionsstandort und gegebenenfalls ein Netzwerk qualifizierter Dienstleister für Design, Test und Lieferkettenmanagement verfügt.

350-nm-CMOS auf 200-mm-Wafern

Anstatt direkt auf Sub-130-nm-Prozesse auf 300-mm-Wafern umzusteigen, entscheiden sich viele Hersteller für 350- oder 180-nm-Knoten auf 200-mm-Wafern. Diese Prozesse bieten ein ausgewogenes Verhältnis zwischen Effizienz, Designkomplexität und langfristiger Rentabilität. Die Entwicklungskosten sind aufgrund einfacherer Design-Flows und kostengünstigerer Maskensätze deutlich niedriger als bei kleineren Strukturgrößen. Die Ausgereiftheit des 350-nm-Knotens ermöglicht zudem eine schnellere Markteinführung mit reduziertem Verifizierungsaufwand. Unterstützt wird dies durch erprobte IP-Blöcke und stabile PDKs, die zu konstant hohen First-Time-Right-Erfolgsquoten beitragen. Die Leistungsfähigkeit von Analog- und High-Voltage-Schaltkreisen ist bei 350 nm oft besser als bei kleineren Strukturen und es steht eine größere Auswahl an Bauelementen zur Verfügung als bei fortschrittlicheren Knoten.

Sowohl ICs mit 350-nm- als auch mit 180-nm-Strukturen werden heute auf 8-Zoll-Wafern gefertigt. Kunden, die gerade eine EOL von Prozessen auf 150-mm-Wafern erlebt haben, fragen sich nun besorgt, ob ihnen dasselbe demnächst auch mit 8-Zoll-Wafern passieren könnte. Deshalb tendieren einige gleich zum Umstieg auf 300-mm-Wafer.

Doch dies würde zwar die langfristige Versorgung sichern, müsste aber sehr teuer erkauft werden. Denn 300-mm-Wafer sind für Chips, die in relativ niedrigen Stückzahlen gefertigt werden, keine wirtschaftlich sinnvolle Option. Das liegt daran, dass die Entwicklungszeit und -kosten sowie die Maskenkosten um ein Vielfaches höher liegen als bei etablierten 200-mm-Wafern. Weil sich die Anzahl der Chips pro Wafer bei der Umstellung von einem Waferdurchmesser auf den nächsten fast verdoppelt, unterschreitet ein Kunde bei einem direkten Wechsel von 150 mm auf 300 mm schnell die Mindestbestellmenge einer Foundry.

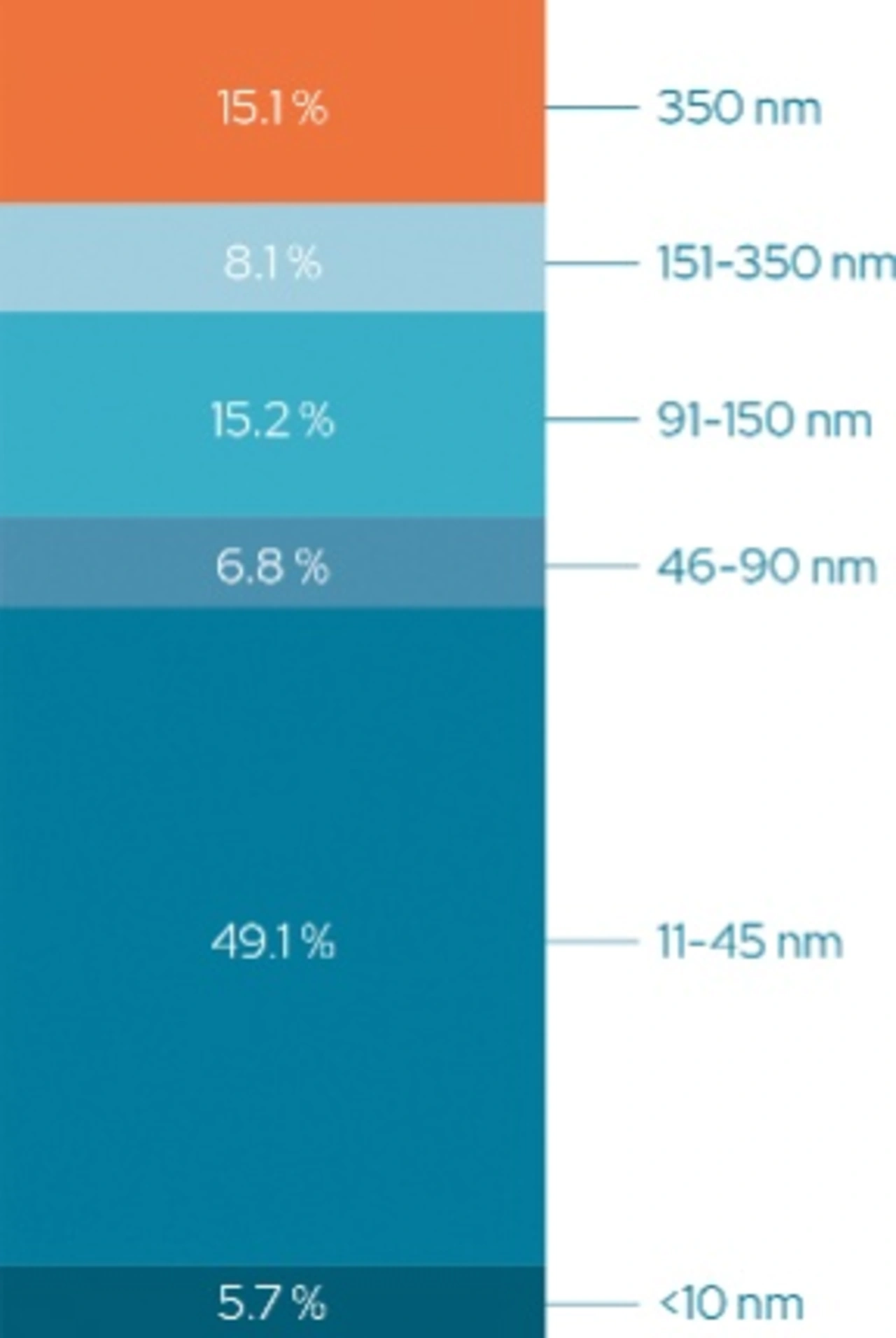

Wird bei der Entscheidung für eine 350- oder 180-nm-CMOS-Technologie die langfristige Verfügbarkeit der Prozesse berücksichtigt, lohnt sich ein Blick auf den aktuellen Stand der Wafer-Lieferungen. Im dritten Quartal 2023 machten Technologieknoten oberhalb von 90 nm mehr als 38 Prozent des monatlich produzierten Wafer-Volumens aus. Dies bedeutet, dass die globale Lieferkette für 200-mm-Wafer weiterhin stark ist und eine kontinuierliche Verfügbarkeit von Materialien und Ausrüstung gewährleistet ist.

Durch seinen langen Lebenszyklus und seine bewährte Stabilität eignet sich der 350-nm-Knoten ideal für Analog-, MEMS- und sensorbasierte Systeme und unterstützt die Integration digitaler Funktionen, die für Mikrocontroller der Einstiegsklasse wie ARM-Cortex-M0-, i8051- oder RISC-V-Cores sowie Embedded-Speicherfunktionen ausreichen.

Bei der Auswahl eines Foundry-Partners sollten Unternehmen sich auf Kriterien konzentrieren, die ihren geschäftlichen Anforderungen entsprechen. Wichtige Fragen sind: Verfügt die Foundry über eine relevante Erfolgsbilanz im Marktsegment des Kunden? Kann sie Lieferverpflichtungen erfüllen, die der erwarteten Lebensdauer und den erwarteten Stückzahlen des ICs entsprechen? Befindet sich der Fertigungsstandort in einer Region mit geringen geopolitischen Risiken? Und bietet er ein Umfeld, das Lieferanten einbindet und Zugang zu Dienstleistern verschafft?

Alle ASIC-Kunden, die von der Obsoleszenz des 150-mm-Waferprozesses betroffen sind und die oben genannten Punkte berücksichtigen, sollten eine Foundry wie X-FAB in Betracht ziehen. Es handelt sich um eine CMOS-Foundry, die sich auf Analog-/Mixed-Signal-Prozesse von 350 bis 110 nm spezialisiert hat. Mit ihren Plug-and-Play-Design-Kits, die präzise Simulationsmodelle für das gesamte Prozessfenster umfassen, ermöglicht X-FAB First-Time-Right-Designs. Der einfache und schnelle Zugriff auf verschiedene Prototyping-Optionen gewährleistet eine nahtlose Produktionsfreigabe. Mit einem Partnernetzwerk aus erfahrenen Dienstleistern für Design, IP, Test und Packaging unterhält X-FAB ein leistungsfähiges Ökosystem – X-Chain von X-FAB. Kunden können sich so auf ihre spezifischen Kernkompetenzen konzentrieren. Die Stabilität der siliziumerprobten Plattformen von X-FAB ermöglicht hohe First-Time-Right-Erfolgsraten, während schnelle und kostengünstige Prototyping-Optionen für einen raschen Produktionsanlauf sorgen.

Gegebenenfalls helfen die Integrationsspezialisten von X-FAB bei der Anpassung der Standardtechnologien an spezielle Anforderungen, einschließlich integrierter MEMS-Prozessoptionen, heterogener Integration und Nachbearbeitung.