ISSCC 2016 in San Francisco

Die Glanzlichter unter den Chips

Fortsetzung des Artikels von Teil 1

Riesige 3D-Speicher und selbstlernende Architekturen

Bei den nichtflüchtigen Speichern zeigte Micron einen NAND-Flash-Speicher mit 3D-Floating-Gate mit einer Kapazität von sagenhaften 768 Gbit, wobei eine Zelle 3 bit speichern kann. Der 179,2 mm2 große Speicher-Chip erreicht eine Dichte von 4,29 Gbit/mm2 und gliedert sich in 32 Kacheln (Tiles). Die CMOS-Schaltungen wurden unter dem Speicherfeld angeordnet. Samsung demonstrierte auf der Konferenz einen 256-Gbit-V-NAND-Flash-Speicher mit 48 vertikal angeordneten Wortleitungsebenen, der auch 3 bit/Zelle speichert. Der Chip misst 97,6 mm2 und gehört zur dritten 3D-NAND-Generation von Samsung. Die E/A-Datenrate beträgt max. 1 Gbit/s. SRAMs sind mittlerweile auch bei 10-nm-FinFET-Prozessen angekommen. Samsung hat ein 128-Mbit-SRAM als 75,6 mm2 großen Test-Chip gebaut, bei dem sich die Parameter auf Leistungsaufnahme, Geschwindigkeit und Chipfläche optimieren lassen. Mit einem Prozessor für smarte Brillen beschäftigte sich das koreanische Forschungszentrum KAIST. Nur 126 mW nimmt der Prozessor für aufsetzbare Displays auf. Der mit 200 MHz getaktete und in 65 nm mit acht Metallisierungslagen gefertigte Prozessor verfügt über einen Embedded Deep Learning Core, der intern zwei Pfade parallel verarbeitet, einen für die Spracherkennung und einen für die Gestenerkennung. Das MIT und Nvidia stellten ebenfalls einen selbstlernenden Prozessor vor, der nach dem Prinzip des Convolutional Neural Networking (CNN) funktioniert. Hauptzweck des in 65 nm produzierten Chips sind Bilderkennungsaufgaben. Mit einer Taktfrequenz von 200 MHz können 34,7 Bilder/s auf fünf Faltungsebenen mit einer Leistungsaufnahme von 278 mW verarbeitet werden.

Jobangebote+ passend zum Thema

Sensoren für Bilder und Medizin

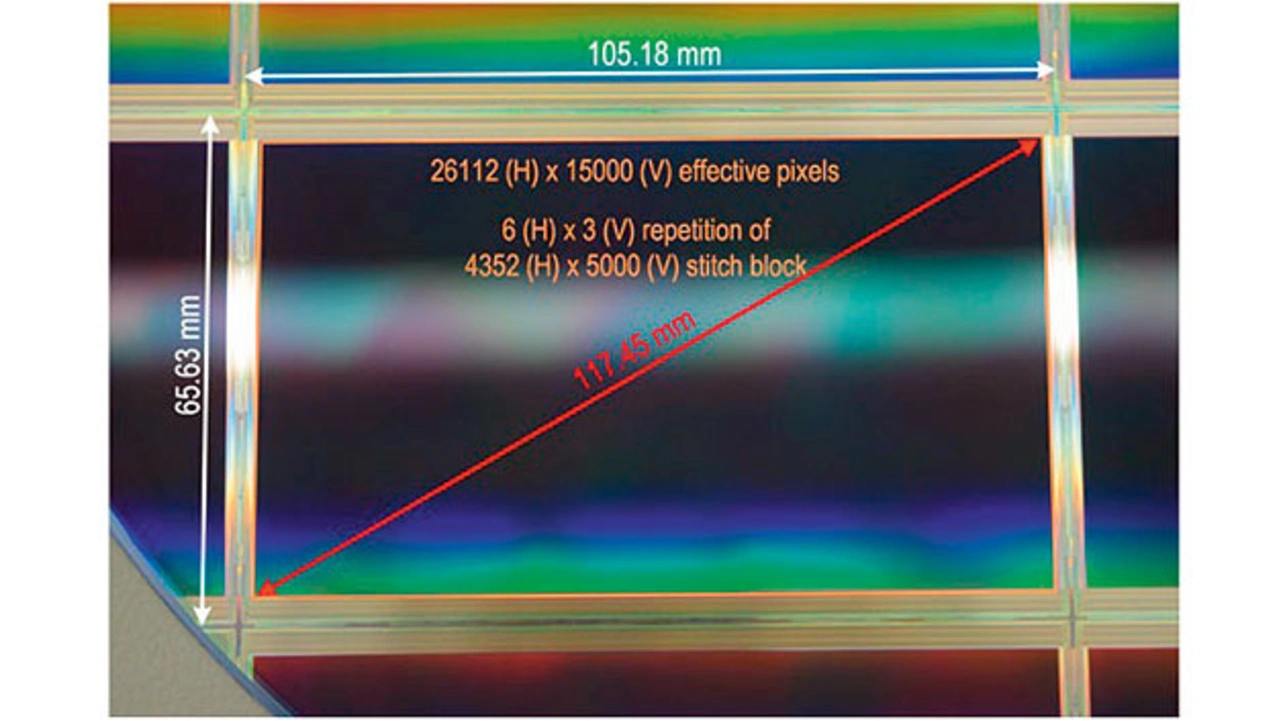

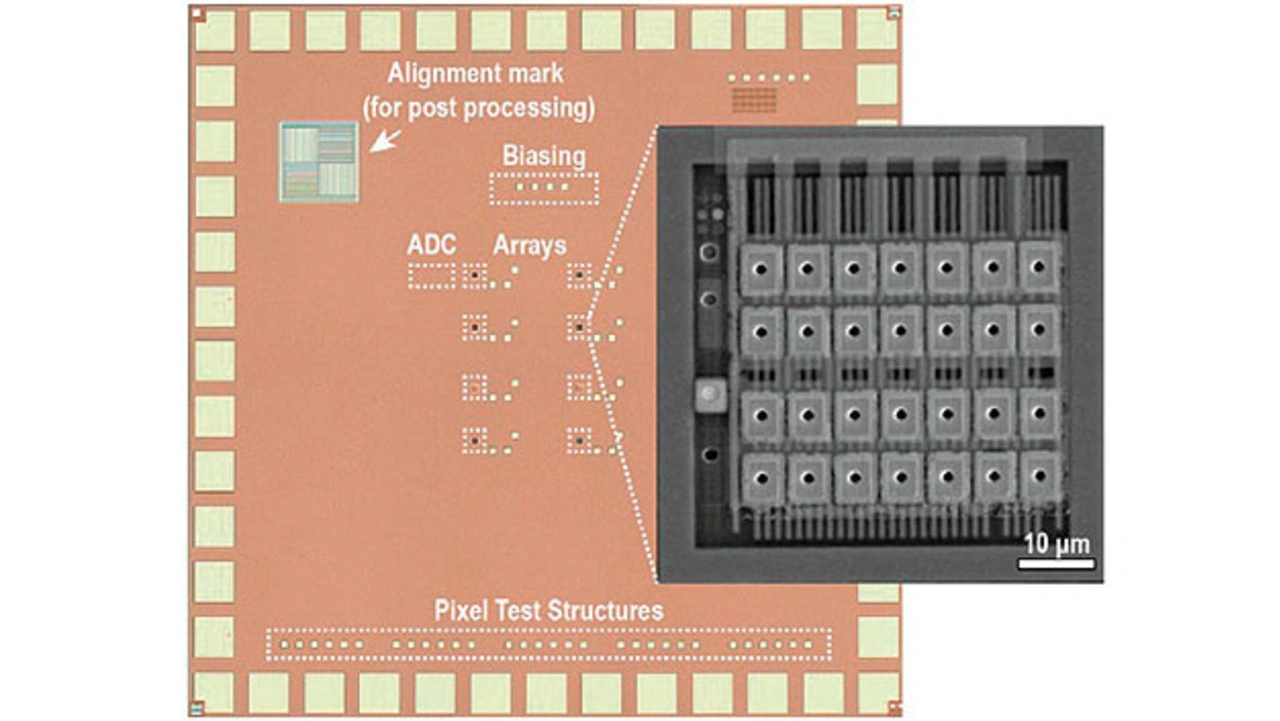

Für Luftbilder hat CMOSIS aus Belgien einen CMOS-Bildsensor mit der gewaltigen Auflösung von 391 Mio. Pixel realisiert, bei dem der Abstand der Bildpunkte 3,9 µm beträgt. Der 105 × 65 mm2 große Bildsensor bietet einen Dynamikbereich von mehr als 78 dB und besteht aus mehreren Blöcken zu je 4352 × 5000 Pixel (Bild 4). Zur Fertigung kamen ein 90-nm-Prozess für die Sensorik und ein 65-nm-Prozess für die Signalverarbeitung von STMicroelectronics zum Einsatz. Die Leistungsaufnahme des Bildsensors beträgt 1750 mW. Zur beschleunigten und kostengünstigen Sequenzierung von DNS haben die Forscher bei Intel einen "Nanogap"-Sensor entwickelt, bei dem zwei planare Elektroden, die durch eine Nanolücke voneinander getrennt sind, elektrochemische Marker detektieren sollen (Bild 5).

Die Elektroden sind aus Platin (50 nm), Chrom (60 nm) und Platin (120 nm) aufgebaut und mit einer 500 nm dicken Oxynitrid-Passivierung überzogen. Der in einem 32-nm-Prozess realisierte Test-Chip umfasst 8192 Pixel, angeordnet in acht Arrays auf einer Fläche von 25 mm2. Ein gleich großer Serien-Chip könnte theoretisch 12 Mio. Pixel umfassen.

Die Leistungsaufnahme des Test-Chips liegt bei einer Spannungsversorgung mit 1,05 V bei 27,9 mW. Wissenschaftler der Princeton University hatten ein EEG-Erfassungs- und Biomarker-Extraktionssystem im Gepäck, das auf Dünnschicht-Elektronik basiert. Die hierfür verwendeten rauscharmen, Chopper-stabilisierten Verstärker aus amorphen Silizium-Dünnschichttransistoren eignen sich für flexible Substrate. Erfasst werden Signale aus mehr als 20 Kanälen. Komprimiert und gemultiplext per TFT-Scanning-Schaltungen, werden die Signale an einer einzigen Schnittstelle zur Weiterverarbeitung zur Verfügung gestellt. Aus den komprimierten Signalen extrahiert ein konventionelles IC über einen implementierten Algorithmus die spektrale Energieverteilung, den generischen EEG-Biomarker.

- Die Glanzlichter unter den Chips

- Riesige 3D-Speicher und selbstlernende Architekturen