IEDM 2018

Moore’s Law ist tot, aber die Skalierung geht munter weiter

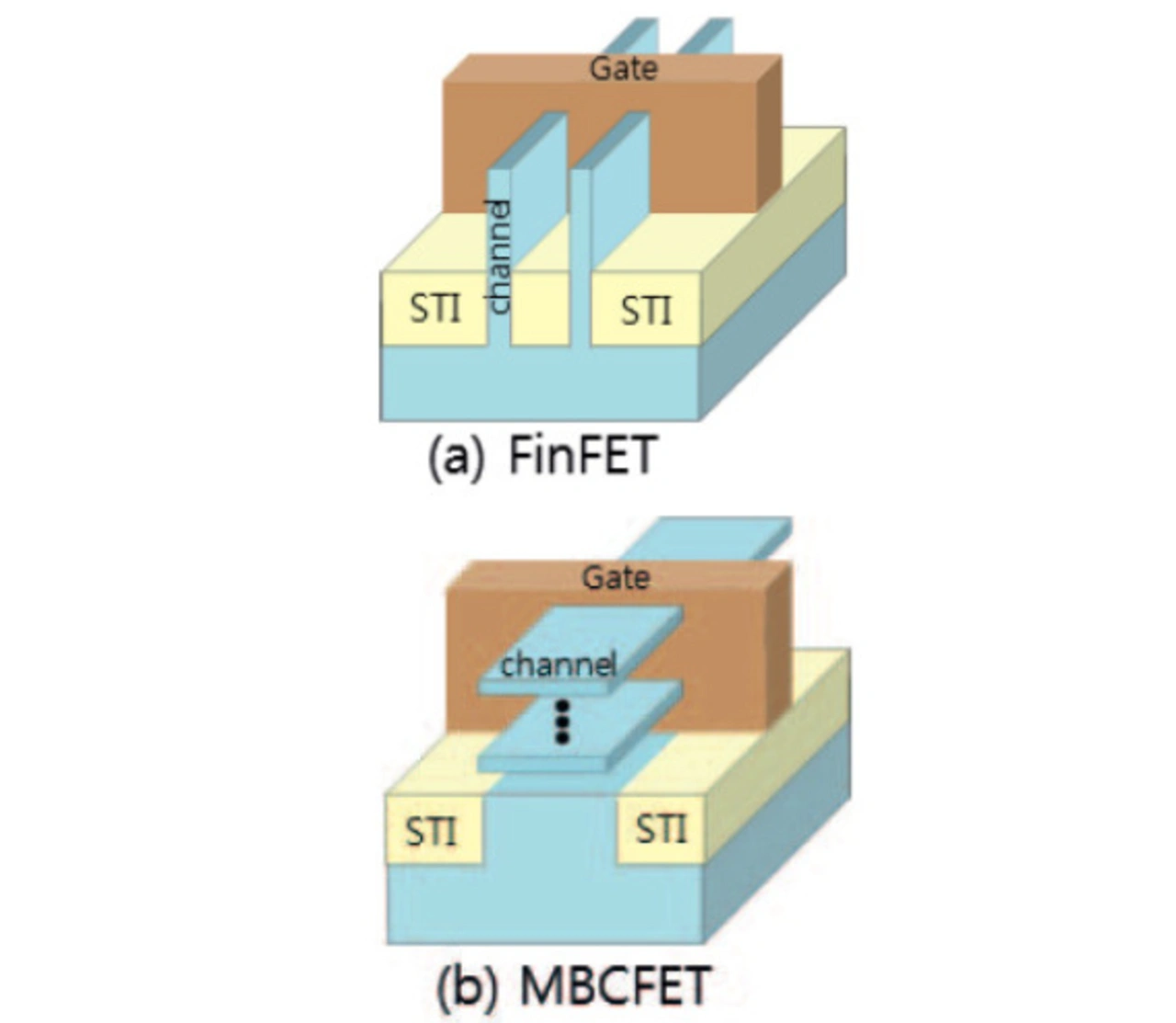

Das diesjährige IEDM ist wieder geprägt von gewaltigen Fortschritten in den unterschiedlichen Dimensionen der Halbleiter-Technik. Von 3-nm-Multi-Bridge-Channel-FETs über 300-GHz-HF-FinFETs bis hin zu Speicher-Architekturen für neuromorphes Computing.

Das International Electron Devices Meeting 2018 (IEDM) glänzte wieder mit zahlreichen Forschungs-Highlights von Unternehmen und Instituten. Bei einem Vortragsprogramm mit 232 Papers in 40 Sessions ist es eine absolute Herausforderung, die interessantesten Entwicklungen und Trends zu identifizieren. Hier sind die Highlights:

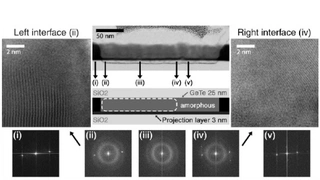

Mark van Dahl von TSMC zeigte einen in Zusammenarbeit mit IMEC entwickelten Ge-CMOS-Gate-Stack mit vertikal gestapelten lateralen Nanowires (NW). Der thermisch stabile High-k-Dielectric-Stack wurde mit Atomic Layer Deposition (ALD) hergestellt und hat das Potential alle Gate-Stack-Anforderungen für n- und p-Kanal Ge-FETs zu erfüllen. Der niedrige Kontaktwiderstand für n-Ge/Metallkontakte liegt auf Rekord-Niveau und wurde ohne Ionenimplantierung in einen Single-NW-Ge-nFET implementiert. Die Single-NW-pFETs weisen bis hinunter zu 24 nm immunität gegenüber Kurz-Kanal-Effekten auf. Die vertikal gestapelten lateralen NW-FETs mit Ge-Kanal wurden auf Basis einer 300-mm-VLSI-Plattform produziert.

Jobangebote+ passend zum Thema

Hohe Packungsdichten durch 3D-Stacking von FinFETs

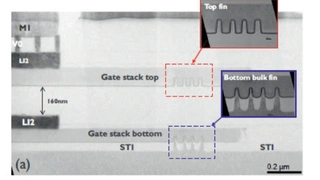

Mit dem Ende von Moore’s Law und der damit verbunden langsameren Skalierung wird das Ausweichen in die dritte Dimension attraktiv. Forschern des Stack, unter Beweis gestellt. Die oberen Transistorstrukturen wurden junction-less bei niedriger Temperatur (<525 °C) hergestellt und werden dann per Wafer-Bonding mit einem bis zu 170 nm hohen Dielectric Stack verbunden." href="http://Mit dem Ende von Moore’s Law und der damit verbunden langsameren Skalierung wird das Ausweichen in die dritte Dimension attraktiv. Forschern des IMEC ist es gelungen, erstmals 3D Stacked FinFETs mit einem Fin-Abstand von 45 nm und 110 nm Gate-Abstand auf 300-mm-Wafern zu fertigen. Damit wird die Kompatibilität dieses sequentiellen 3D-Ansatzes für aggressive Packungsdichten bei fortschrittlichen Prozess-Knoten dank einer hochpräzisen Ausrichtung der ersten prozessierten obersten Schicht bis zur untersten, vom obersten Silizium-Kanal über den Bonding-Stack, unter Beweis gestellt. Die oberen Transistorstrukturen wurden junction-less bei niedriger Temperatur (<525 °C) hergestellt und werden dann per Wafer-Bonding mit einem bis zu 170 nm hohen Dielectric Stack verbunden.">IMEC ist es gelungen, erstmals 3D Stacked FinFETs mit einem Fin-Abstand von 45 nm und 110 nm Gate-Abstand auf 300-mm-Wafern zu fertigen. Damit wird die Kompatibilität dieses sequentiellen 3D-Ansatzes für aggressive Packungsdichten bei fortschrittlichen Prozess-Knoten dank einer hochpräzisen Ausrichtung der ersten prozessierten obersten Schicht bis zur untersten, vom obersten Silizium-Kanal über den Bonding-Stack, unter Beweis gestellt. Die oberen Transistorstrukturen wurden junction-less bei niedriger Temperatur (<525 °C) hergestellt und werden dann per Wafer-Bonding mit einem bis zu 170 nm hohen dielektrischen Stack verbunden.

Die Highlights der IEDM 2018

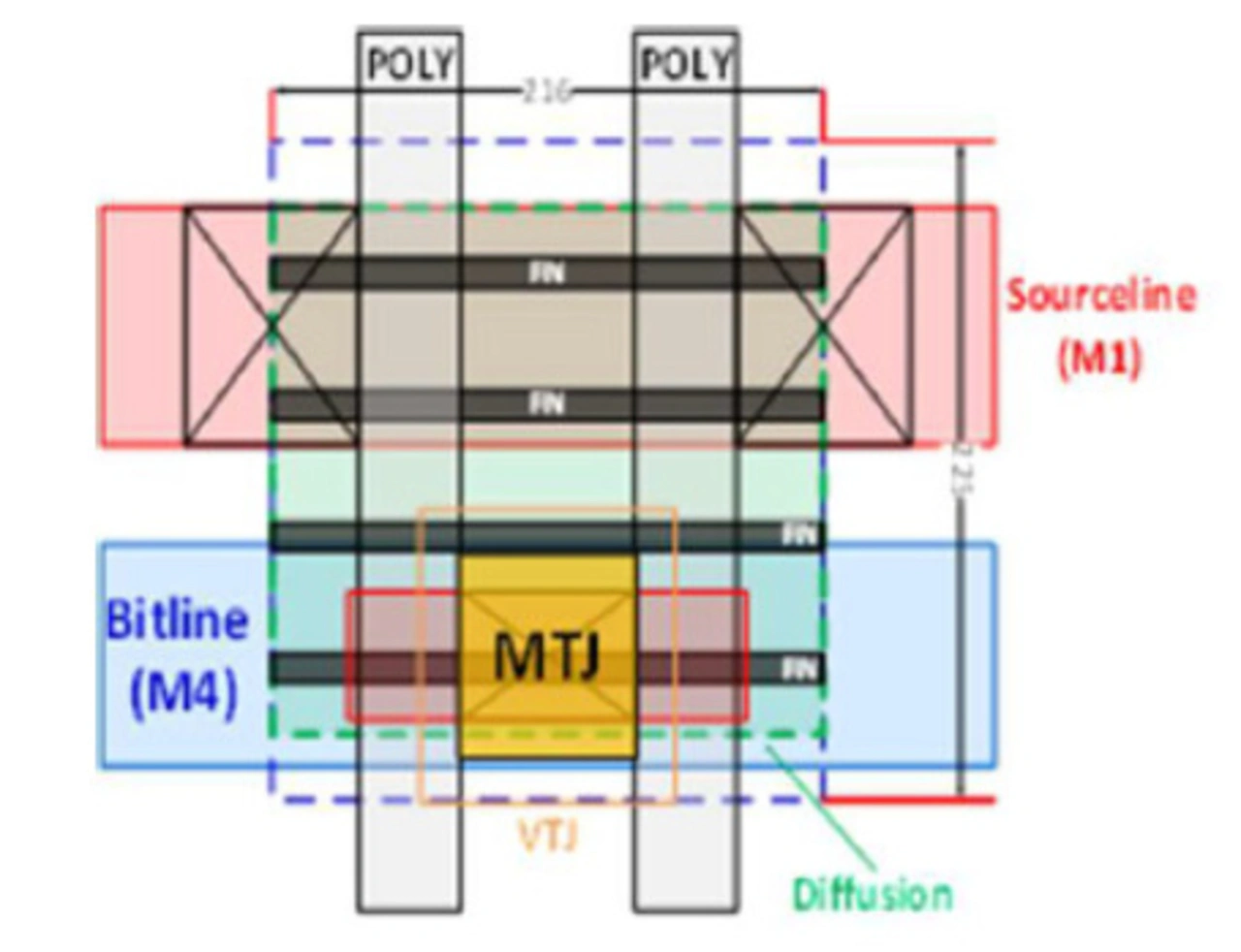

Embedded MRAM für 22 nm FinFETs und FD-SOI

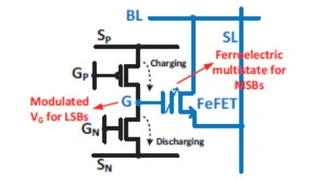

Die Integration nichtflüchtiger Speicher in Prozessoren wird unter anderem bei In-Memory-Computing-Ansätzen bedeutsam. Intel hat nun für seinen 22FFL-Prozess MRAM-Zellen entwickelt. Der Prozess 22FFL bietet High-Performance, Ultra-Low-Power-FinFETs für mobile und HF-Anwendungen mit umfangreicher Unterstützung von höheren Spannungen und Analogfunktionen sowie eine hohe Design-Flexibiliät bei niedrigen Kosten. Diese einbettbaren nichtflüchtigen Speicher erreichen bei 200 °C eine Mindest-Speicherdauer von zehn Jahren und erlauben mehr als 1 Million Schreibzyklen. Diese Daten wurden belegt durch die Realisierung eines 7,2 Mbit großen Speicher-Arrays, das auf einem 300-mm-Wafer gefertigt wurde und eine hohe Ausbeute verspricht.

Auf planare 22-nm-FD-SOI-Technologie in Zusammenhang mit MRAM setzt Globalfoundries. Das Besondere daran ist, dass das realisierte 40 Mbit Embedded MRAM für Automotive-Anwendungen entwickelt wurde und einen Arbeitstemperaturbereich bis 150 °C umfasst. Die Bitfehlerrate liegt im sub-ppm-Bereich, so dass nach einer Million Zyklen keine Fehler auftreten.

- Moore’s Law ist tot, aber die Skalierung geht munter weiter

- Neuromorphes Computing und Si-basiertes Quanten-Computing