IEDM 2019

Unsere Top 10 der Halbleiter-Trends

Auf dem International Electron Devices Meeting stehen traditionell die Transistorstrukturen, also die Basiselemente für die Chip-Integration, im Fokus. Hier haben wir für Sie zehn ausgewählte Meilensteine in der Halbleitertechnik.

Das 65. International Electron Devices Meeting (IEDM), das wie gewohnt im San Francisco Hilton Union Square stattfand, glänzte wieder mit zahlreichen Durchbrüchen in der Halbleitertechnik. Doch zunächst ein wenig Statistik. Insgesamt pilgerten mehr als 1880 Teilnehmer an die Westküste der USA, um ein Programm mit 238 Papers, verteilt auf 39 Sessions sowie sechs Tutorials und zwei Short-Courses zu bewältigen. Insgesamt hatte die Halbleiter-Community 613 Papers eingereicht, von denen allerdings nur 28 Prozent vom Programm-Komitee akzeptiert werden konnten, »invited Papers« bleiben dabei allerdings unberücksichtigt. Interessant ist auch die regionale Verteilung: 53 Prozent kommen mittlerweile aus Asien-Pazifik, 29 Prozent aus Amerika und 20 Prozent aus Europa. Hier verschieben sich also die Gewichte deutlich von Amerika nach Asien. Signifikant ist mittlerweile der hohe Anteil von 65 Prozent, der auf Universitäten und Forschungsinstitute entfällt. Nur 27 Prozent der Papers kommen noch aus der Industrie, acht Prozent von regierungsnahen Organisationen. Sehr gut besucht waren vor allem die vier »Focus Sessions«, die aktuelle Fortschritte in ausgewählten Themenkomplexen zusammengefasst hatten. Besonderen Zuspruch fanden die beiden Sessions zu »Emerging AI Hardware Technologies« und »Quantum Computing Infrastructure«, die praktisch durchgängig von invited Papers getragen wurden.

Jobangebote+ passend zum Thema

CMOS-Skalierung geht weiter

Auf dem IEDM werden traditionell die Weiterentwicklungen bei den Transistorstrukturen beleuchtet, und auf diesem Gebiet hat die Halbleitertechnik deutliche Fortschritte erzielt:

1. TSMC 5 nm-CMOS-Plattform

2. Intel mit heterogener 3D-Integration

3. IMEC mit Forksheet-Strukturen

4. TSRI und UC Berkeley mit 3D-Stacking bei niedriger Temperatur

5. IMEC mit vertikalen Strukturen für ultraskalierte Schaltungen

TSMC mit 5-nm-CMOS-Plattform

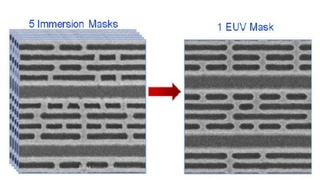

TSMC hat mit seiner 5-nm-CMOS-Technologie-Plattform einen neuen Pflock eingerammt: Der neue Halbleiterprozess wurde sowohl für mobile als auch für Hochleistungsrechner optimiert ist. Er bietet fast die doppelte Logikdichte (1,84x) und wahlweise eine 15-prozentige Geschwindigkeitssteigerung oder eine 30-prozentige Reduzierung der Leistungsaufnahme gegenüber dem vorhergehenden 7-nm-Prozess. TSMC setzt bei 5 nm auf eine umfassende Nutzung der EUV-Lithographie, um die Immersions-DUV-Lithographie an wichtigen Punkten des Herstellungsprozesses zu ersetzen. Im Ergebnis wird die Gesamtzahl der Masken gegenüber der 7-nm-Technologie deutlich reduziert. Außerdem nutzt die 5-nm-Plattform FinFETs mit hoher Ladungsträgerbeweglichkeit im Kanal und SRAM-Zellen mit hoher Dichte. Das SRAM kann für Low-Power- oder High-Performance-Anwendungen optimiert werden, so dass die High-Density-Version (0,021 μm2) das wohl derzeit dichteste SRAM sein dürfte, über das bis dato berichtet wurde. Einen detaillierten Bericht finden Sie hier.

Intel setzt auf heterogene 3D-Integration zur Skalierung

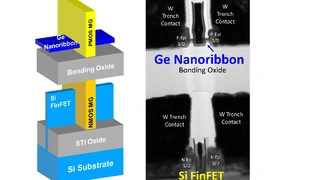

CMOS-Technologien erfordern sowohl NMOS- als auch PMOS-Transistoren, aber die Leistungsfähigkeit von PMOS liegt gegenüber NMOS zurück. Diese Fehlanpassung muss behoben werden, um zukünftigen Chips das letzte bisschen Leistung und Energieeffizienz abzuringen. Eine Möglichkeit, dies zu erreichen, ist der Bau von PMOS-Transistoren mit Kanälen mit höherer Ladungsträgerbeweglichkeit als ihre NMOS-Pendants, aber weil diese aus anderen Materialien als Silizium (Si) hergestellt werden, die eine unterschiedliche Verarbeitung erfordern, ist es eine Herausforderung, den einen Typ zu bauen, ohne den anderen zu beschädigen. Die Intel-Forscher haben dies mit einer 3D-Sequential-Stacking-Architektur umgangen. Sie bauten zunächst Si FinFET-NMOS-Transistoren auf einem Silizium-Wafer. Auf einem separaten Si-Wafer stellten sie eine einkristalline Ge-Schicht her, die als Pufferschicht verwendet wurde. Sie drehten den zweiten Wafer um, verbanden ihn mit dem ersten, härteten beide, um eine lückenlose Grenzfläche zu erzeugen, spalteten den zweiten Wafer bis auf die Ge-Schicht ab und bauten darauf Gate-All-Around-Ge-Kanal-PMOS-Bauelemente (GAA) auf. Dabei traten keine Leistungseinbußen bei den zugrunde liegenden NMOS-Bauteilen auf, und in einem Inverter-Testschaltkreis zeigten die PMOS-Bauteile die beste Ion-Ioff-Leistung, die jemals für Ge-Kanal-PMOS-Transistoren berichtet wurde (Ion = 497 μA/μm und Ioff = 8 nA/μm bei 0,5V). Die Forscher sagen, dass diese Ergebnisse zeigen, dass eine heterogene 3D-Integration für die CMOS-Logik in hochskalierten Technologieknoten vielversprechend ist. Neben der heterogenen 3D-Integration berichtete Intels Robert Chou in einer Keynote über weitere technologische Ansätze zur Fortführung von Moore’s Law.

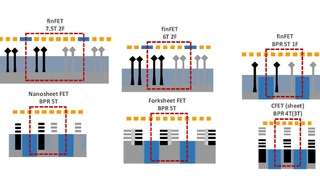

IMEC mit Forksheet-Transistorstruktur

Das flämische Mikroelektronikforschungszentrum IMEC präsentierte erste Standardzellen-Simulationsergebnisse seines »Forksheet«-Transitors, der für Knoten von Sub-3-nm-Logikprozessen ausgelegt ist. Im Vergleich zu Nanosheet-Bauteilen führt der reduzierte n-to-p Abstand zu einer 10-prozentigen Leistungssteigerung. In Kombination mit Skalierungsverstärkern soll die neue Bausteinarchitektur die Höhe der Standard-Logikzellen auf 4,3 Tracks reduzieren, was in Kombination mit der Optimierung der Zellenstruktur zu einer mehr als 20-prozentigen Flächenreduzierung führen kann. Die Ergebnisse lassen die Forksheet-Architektur als eine mögliche Lösung zur Erweiterung der Skalierbarkeit von Nanosheet-Strukturen über den 3-nm-Logik-Technologieknoten hinaus erscheinen.

Forksheet-Transistoren wurden kürzlich vom IMEC als natürliche Erweiterung von vertikal-gestapelten lateralen Gate-All-Around-Nanosheet-Transistoren vorgeschlagen. Im Gegensatz zum Gate-All-Around Nanosheet-Transistor werden die Nanosheets im Forksheet nun durch eine Tri-Gate-Gabelstruktur gesteuert, die durch die Einführung einer dielektrischen Wand zwischen den P- und NMOS-Bauelementen vor der Gate-Strukturierung realisiert wird. Diese Wand isoliert den p-Gate-Graben physikalisch vom n-Gate-Graben, wodurch ein viel engerer n-zu-p-Abstand ermöglicht wird – eine Herausforderung, die mit FinFET- oder Nanosheetstrukturen nicht gelöst werden konnte. Aufgrund dieser reduzierten n-zu-p-Abstände wird erwartet, dass das Forksheet eine überlegene Flächen- und Leistungsskalierbarkeit aufweist.

Top 10 Trends in der Halbleitertechnik 2019

TSRI und UC Berkeley mit 3D-Stacking bei niedriger Temperatur

Ein Team unter der Leitung des Taiwan Semiconductor Research Institute und mit Beteiligung der UC Berkeley berichtete über die monolithische 3D-Fertigung von GAA-Transistoren bei weniger als 400°C. Die relativ niedrige Prozesstemperatur war der Schlüssel dazu, Transistoren zu bauen und zu stapeln, ohne bestehende Bauelemente zu beschädigen. Die stapelbare Struktur hatte einen 5 nm breiten, 34 nm hohen rechteckigen polykristallinen Nanowire-Kanal. Die GAA-Bausteine zeigten ein rekordverdächtig hohes Ion-Ioff-Verhältnis (108) und einen niedrigen Ioff-Strom (pFETs < 10-2 nA/μm). Die Basis dafür legten plasmagestütztes Ätzen von Atomschichten zur Seitenwandstrukturierung des Kanals, die Plasma-Ionen-Implantation und der Einsatz von Laserpulsen im fernen Infrarot für eine optimierte Aktivierung. Die Forscher demonstrierten die Vorteile dieser gestapelten Struktur in einer SRAM-Schaltung für Compute-in-Memory-Anwendungen.

IMEC mit vertikalen Transistoren für die Ultra-Skalierung

Wissenschaftler des flämischen IMEC präsentierten p- und n-Typen für vertikale GAA-Nanowire- und Nanosheet-Transistoren mit SiGe/Si-Säulen und selbstjustierenden Spacern (Abstandshaltern), die zu hochskalierten Schaltungen führen könnten. Die Forscher führten umfassende Studien zu den Auswirkungen der Bauelemente-Dotierung und der physikalischen Dimensionen auf die Leistung, Variabilität, Rauschen und Zuverlässigkeit von Transistoren durch, und zwar für Bauelemente ohne Sperrschicht im Vergleich zu Bauelementen im Inversionsmodus, die mit einem Replacement-Metal-Gate-Prozess gefertigt werden. Zur Herstellung der selbstjustierenden Spacer, die das Gate an Source/Drain ausrichten, nutzten die Forscher die unterschiedlichen Oxidwachstumsraten von Si und Ge. Sie gehen davon aus, dass diese vertikalen Bauelemente, wenn sie als Selektor für einen STT-MRAM verwendet werden, eine erhebliche Flächenreduzierung (64 %) gegenüber FinFETs ermöglichen würden, zusammen mit einer erheblichen Reduzierung der Lese-/Schreibenergie und der Latenzzeit.

- Unsere Top 10 der Halbleiter-Trends

- KI, Neuronale Netze und Neuromorphes Computing