IEDM 2017

3D-Integration im Quadrat für allgegenwärtiges Computing

Auf dem 63. IEDM in San Francisco erklärte Jack Y.C. Sun, CTO von TSMC, wie er sich die System-Skalierung für das intelligente allgegenwärtige Computing vorstellt. Zentrales Element ist die 3D-Integration in zwei Richtungen, auf Bauelemente- und Systemebene.

Das International Electron Devices Meeting ist seit 63 Jahren der weltweit führende Treffpunkt für künftige Halbleiter-Technologien auf Transistorebene. Rund 1700 Teilnehmer haben sich in diesem Jahr auf den Weg nach San Francisco gemacht. Mit der umfangreichen Erfahrung in der Herstellung von Halbleiterschaltungen, wie sie die weltgrößte Foundry TSMC mit seinem Prozesstechnik-Baukasten sicherlich hat, dürfte deren CTO Jack Y.C. Sun einer der gefragtesten Keynote-Speaker aus Asien sein.

Jobangebote+ passend zum Thema

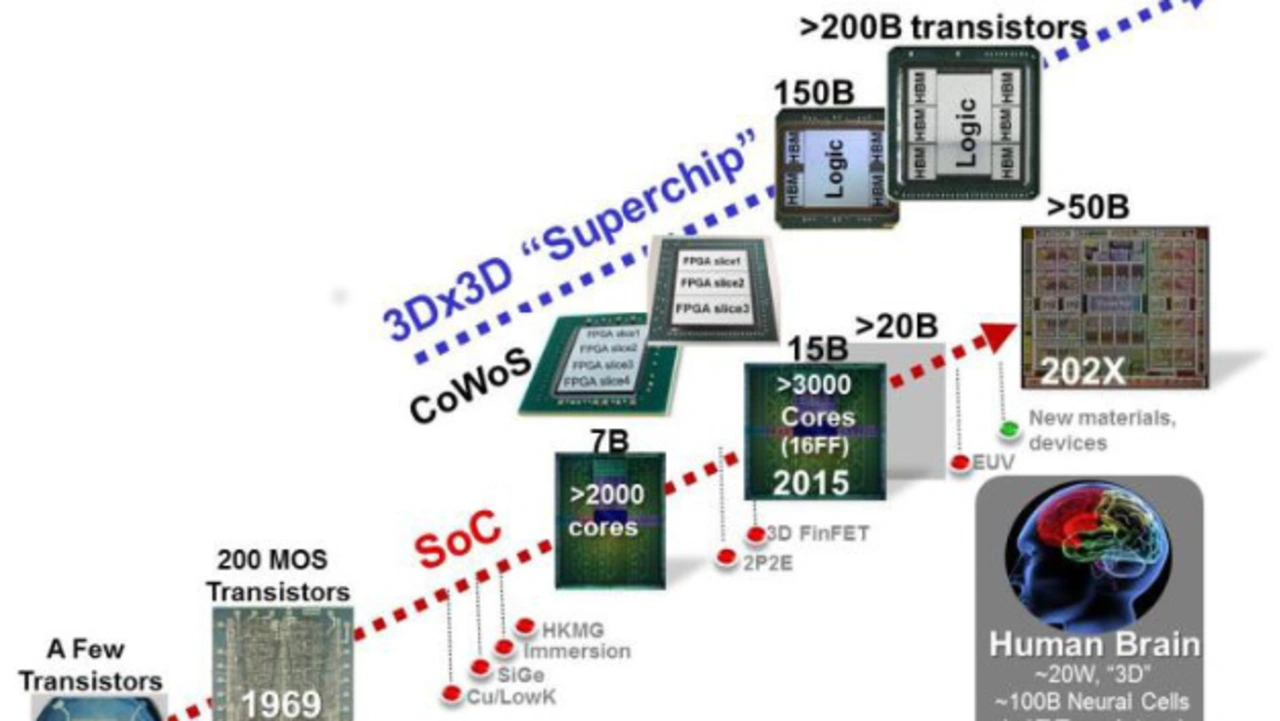

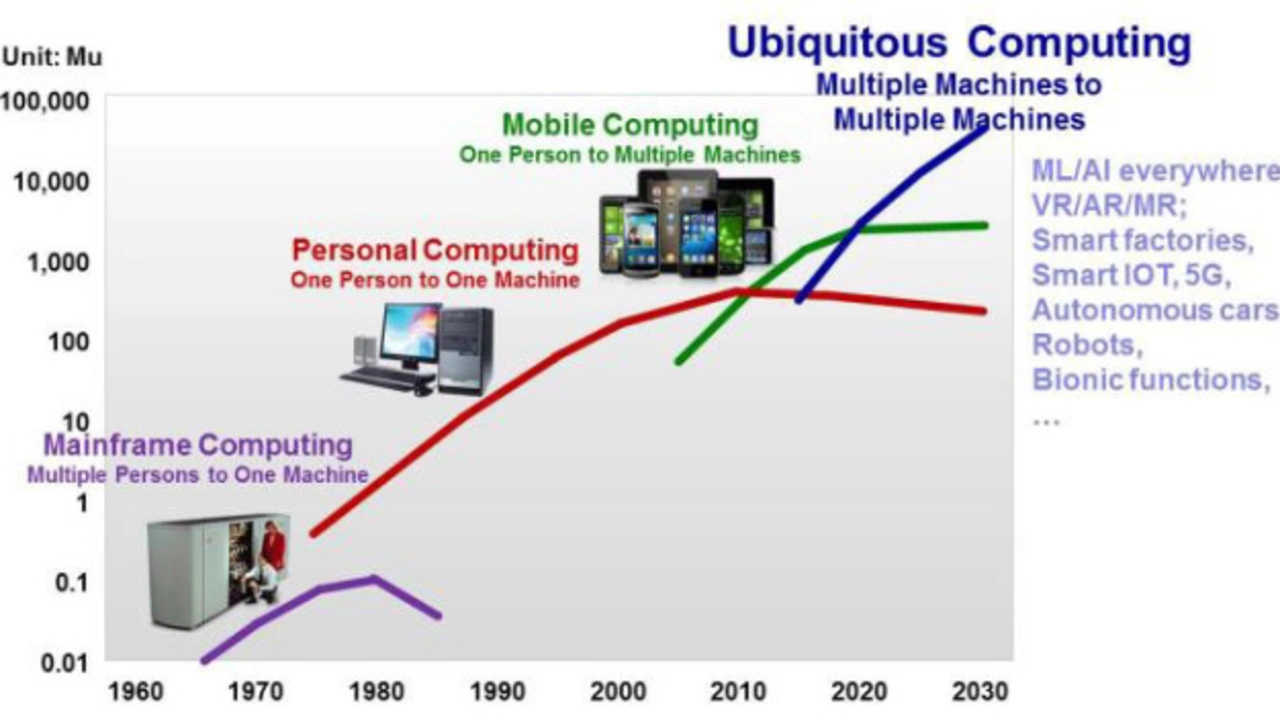

In seinem Vortrag beleuchtete der Taiwaner, wie Wafer-basierte 3Dx3D-System-Skalierung Maschinelles Lernen und Künstliche Intelligenz sowie das mobile Computing revolutionieren. Die 3D-CMOS-Skalierung birgt weiterhin Herausforderungen und Chancen für eine unerbittliche Innovation bei Materialien, Prozessen, Transistorstrukturen, Schaltungen, Entwurf, EDA, Computerarchitekturen, Algorithmen und Software. 3D-Stacking und heterogene Systemintegration bereichert nicht nur, sondern verstärkt sogar noch die Vorzüge von 3D-CMOS-Logik, 3D-Speicher, integrierten Spezialtechniken und 3D-Sensoren für das intelligente, allgegenwärtige Computing. Mit 3Dx3D-Integration können so bis in die 2020er hinein Subsysteme entstehen, deren kumulierte Transistorzahl die Komplexität des menschlichen Gehirns erreichen können.

In letzter Zeit gab es enorme Fortschritte in Wafer-basierter 3Dx3D-System-Skalierung. Nicht nur die Transistorzahl auf einem SoC steigt kontinuierlich, sondern auch die des Gesamtsystems durch zahlreiche aufeinander gestapelte Chips (Stacking). Ein solcher 3Dx3D-Superchip kann heute ohne weiteres 150 Mrd. Transistoren umfassen und Daten mit 0,9 Tbyte/s übertragen bei Rechenleistungen im Zehn-TFlops-Bereich. Als Beispiel zeigte Sun die zweite Generation des AI-Chips Volta von Nvidia.

- 3D-Integration im Quadrat für allgegenwärtiges Computing

- 3D-CMOS- und SoC-Skalierung

- Heterogene 3D-System-Integration