Forschungsprojekt Propedes

Mehr Sicherheit für Fußgänger

Fortsetzung des Artikels von Teil 8

Applikationsspezifisch konfigurierbare Soft-Core-Prozessoren

Mit Hilfe des Multi-FPGA-basierten Labordemonstrators konnten die unterschiedlichen Architekturvarianten aus dedizierten Hardware-Beschleunigern und eingebetteten Prozessorkernen untersucht werden. Das Institut für Mikroelektronische Systeme (IMS) hat dazu in Zusammenarbeit mit Pro Design eine heterogene Hardware-Architektur konzipiert und implementiert, die mehrere Hardware-Beschleuniger (Co-Prozessoren) und einen konfigurierbaren und erweiterbaren Prozessor enthält. Dieser Soft-Core-Prozessor liegt als Hardware-Beschreibung in einer Hardware-Beschreibungssprache (Verilog/VHDL) vor und kann somit beliebig in das FPGA integriert werden.

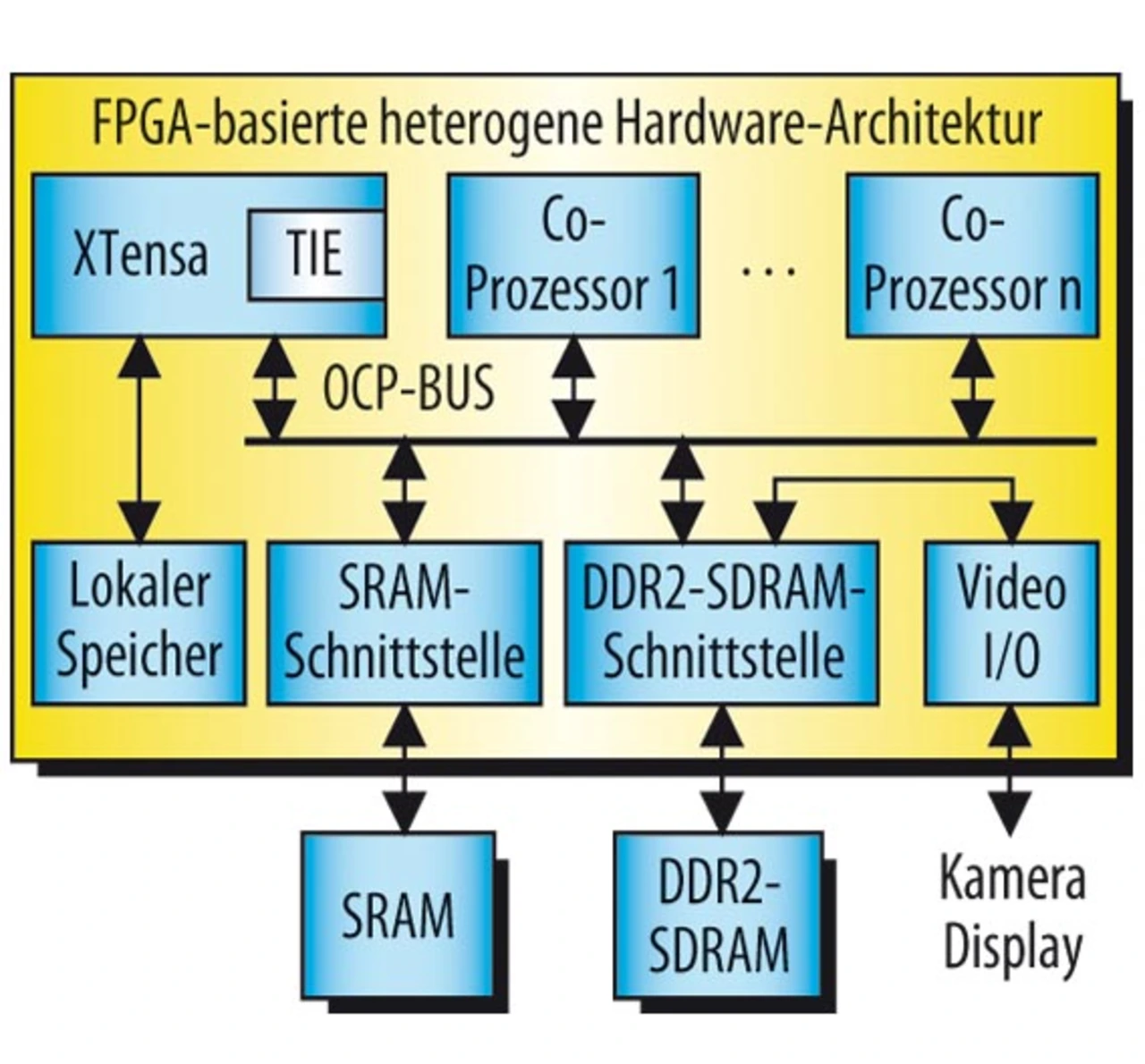

Bild 7 zeigt diese Hardware-Architektur. Der konfigurierbare und erweiterbare Soft-Core-Prozessor der Firma Tensilica (XTensa LX ) wird über eine Multi-Layer-Busstruktur mit der Peripherie verbunden. Der Prozessorkern ist in zweierlei Hinsicht anpassbar. Einerseits kann die Ausstattung des Prozessorkerns (z.B. Cache-Größen, Busanbindung, Multiply-Accumulate-Einheit) der Anwendung entsprechend konfiguriert werden. Andererseits kann der Prozessor um neue Funktionseinheiten und neue Befehle über die Verilog-ähnliche Hardware-Beschreibungssprache TIE (Tensilica Instruction Extension) erweitert werden. Der Prozessor kann auf unterschiedliche Speicher zugreifen. Die Architektur besitzt lokalen Speicher mit geringer Latenz sowie externe SRAM- und DDR2-SDRAM-Speicher, welche über die OCP-basierte Infrastruktur mit dem Prozessor verbunden sind. Reguläre Verarbeitungsschritte, wie zum Beispiel die Bildvorfilterung, können in autark arbeitende Co-Prozessoren ausgelagert werden, die über die OCP-Infrastruktur eigenständig auf die Bilddaten im gemeinsam genutzten externen Speicher zugreifen. Die Abarbeitung in den Co-Prozessoren kann somit komplett unabhängig und parallel zum Prozessorkern erfolgen.

- Mehr Sicherheit für Fußgänger

- Nachtsichtassistenten der nächsten Generation

- NIR-Radar

- NIR-FIR

- Fusionsverfahren

- In Propedes entwickelte Software-/Hardware-Architekturen für mehr Rechenleistung

- Anbindung an das ADTF-Framework

- Optimale Partitionierung der Videoalgorithmen

- Applikationsspezifisch konfigurierbare Soft-Core-Prozessoren

- Umsetzung auf Multi-FPGA-Hardware-Plattform

- FPGA-basierter Ansatz bietet viel Potential

- Die Autoren