Forschungsprojekt Propedes

Mehr Sicherheit für Fußgänger

Fortsetzung des Artikels von Teil 9

Umsetzung auf Multi-FPGA-Hardware-Plattform

Auf diese heterogene Hardware-Architektur wurden vom IMS relevante Algorithmen der Fahrerassistenz abgebildet. Es entstanden unterschiedliche Co-Prozessoren und der Prozessor wurde um Spezialbefehle erweitert. Die Umsetzung der Hardware-Architektur erfolgte auf der oben beschriebenen Multi-FPGA-Hardware-Plattform. Ein Ziel des Propedes-Projekts war die Erforschung sowie der Vergleich der unterschiedlichen Abbildungs- und Partitionierungsvarianten der Algorithmen. Von besonderem Interesse war hierbei auch die Untersuchung der Anpassung des Prozessorkerns an die komplexen Algorithmen der videobasierten Fahrerassistenz und die daraus resultierenden Zuwächse an Rechenleistung. Diese können jedoch nur erreicht werden, wenn ein Zusammenspiel aus Prozessor-Erweiterungen und eine gleichzeitige Optimierung der Software erfolgt. Prinzipiell lassen sich die Hardware- und Software-Optimierungen wie folgt zusammenfassen:

- Parallele Berechnung möglichst vieler Ergebnisse: Dies kann durch Single-Instruction-Multiple-Data (SIMD) oder durch neue komplexe Funktionseinheiten erreicht werden, die mehrere Einzeloperationen zu einer komplexen Operation zusammenfügen. Dies ermöglicht einen höheren Datendurchsatz, so dass das Laden von Daten zur Verarbeitung mit einer möglichst geringen Verzögerung erfolgt.

- Maximale Wiederverwendung einmal geladener Daten: Häufig wird ein Datum in einem Algorithmus mehrfach genutzt, was zu einem Mehrfachzugriff auf den externen Speicher führen kann. Neue Datenregister, lokale Speicher und Anpassungen am Algorithmus minimieren den externen Speicherzugriff.

- Effiziente Ausnutzung der Prozessor-Caches: Daten im externen Speicher müssen so organisiert sein, dass der Cache mit den gewählten Parametern wie Zeilenlänge oder Verdrängungsmechanismus möglichst effizient genutzt werden kann. Dies bedeutet, dass die Daten in einer Cache-Zeile möglichst alle genutzt werden, bevor die Cache-Zeile ersetzt wird.

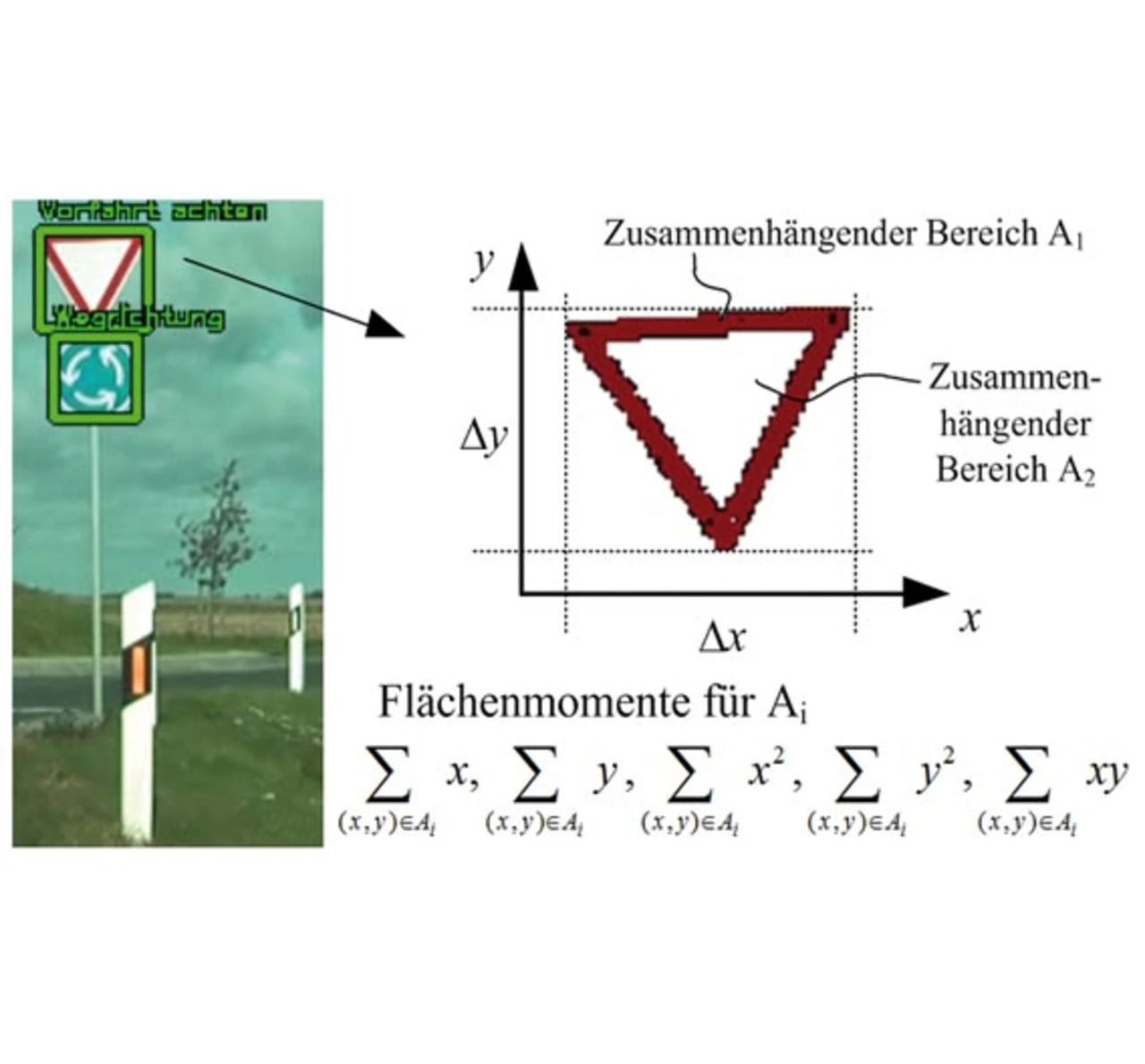

Diese Vorgehensweise soll an folgendem Beispiel aus einer videobasierten Verkehrszeichenerkennung erläutert werden. Durch eine geeignete Vorverarbeitung wird in einem Bild ein Bildausschnitt mit einem möglichen Verkehrszeichen extrahiert. Zur Erkennung des Verkehrszeichens erfolgt eine Binarisierung des Bildes mit anschließender Indizierung zusammenhängender Bereiche im Bild. Als Merkmale zur Klassifikation werden unter anderem die Höhe und Breite sowie weitere Flächenmomente des umschließenden Rechtecks für jeden zusammenhängenden Bereich gebildet (Bild 8). Dazu wird für jeden Bereich ein Akkumulatorspeicher angelegt, der die Flächenmerkmale berechnet. Anschließend wird das Index-Bild Pixel für Pixel durchlaufen, die Multiplikationen gebildet und entsprechend der Objektzugehörigkeit zum jeweiligen Akkumulatorspeicher hinzuaddiert. Hierbei werden die oben genannten Optimierungsstrategien wie folgt beachtet:

- Die Multiplikationen werden parallel in einer Instruktion durchgeführt. Die Prozessor-Pipeline ermöglicht es, die Zahl der Multiplizierer gering zu halten.

- Die Akkumulatorspeicher befinden sich im lokalen Prozessorspeicher, da sie mehrfach verwendet werden. Dies reduziert den Zugriff auf den externen Speicher. Des Weiteren wird die Bestimmung der Formmerkmale mit der Indizierung der zusammenhängenden Bereiche kombiniert, so dass das Ergebnis der Indizierung sich noch in den Prozessorregistern befindet. Daher kann der Objektindex direkt für die Bestimmung der Formmerkmale verwendet werden.

- Die pixel-weise Verarbeitung des Index-Bildes sowie die Nutzung lokaler Akkumulatorspeicher ermöglicht es, alle Werte einer Cache-Zeile zu nutzen, bevor die Cache-Zeile aus dem Cache verdrängt wird.

- Mehr Sicherheit für Fußgänger

- Nachtsichtassistenten der nächsten Generation

- NIR-Radar

- NIR-FIR

- Fusionsverfahren

- In Propedes entwickelte Software-/Hardware-Architekturen für mehr Rechenleistung

- Anbindung an das ADTF-Framework

- Optimale Partitionierung der Videoalgorithmen

- Applikationsspezifisch konfigurierbare Soft-Core-Prozessoren

- Umsetzung auf Multi-FPGA-Hardware-Plattform

- FPGA-basierter Ansatz bietet viel Potential

- Die Autoren