Forschungsprojekt Propedes

Mehr Sicherheit für Fußgänger

Fortsetzung des Artikels von Teil 5

In Propedes entwickelte Software-/Hardware-Architekturen für mehr Rechenleistung

Die Berechnung der Merkmale aus den Sensorbilddaten und die Sensorfusion in möglichst kurzer Zeit erfordern eine hohe Rechenleistung. Daher muss der Klassifikationsalgorithmus auf mehrere parallel arbeitende Recheneinheiten aufgeteilt werden, die i.A. speziell an die jeweiligen Teilverfahren angepasst sind. Diese Partitionierung in ein paralleles, heterogenes Verarbeitungssystem ist für die resultierende Rechenleistung des Gesamtsystems entscheidend und stellt eine wesentliche Herausforderung dar. Die Erarbeitung einer geeigneten Partitionierungsmethodik war daher der zweite Untersuchungsgegenstand im Forschungsprojekt Propedes.

Eine Teiloperation kann hinsichtlich des Rechenaufwands, der Regularität (Zugriffsmuster auf Ein- und Ausgangsdaten, Variation von Rechenschritten) und der Autonomie (Zeit zwischen zwei Steuereingriffen) kategorisiert werden. In der klassischen Signalverarbeitung werden zwei Kategorien unterschieden: Bei den regulären Low-Level-Operationen mit hohem Rechenaufwand und hoher Autonomie (mehrere Millisekunden pro Teiloperation) eignet sich eine Umsetzung in Hardware-Beschleuniger, d.h. Hardware-Blöcke, die mit wenigen Steuerparametern sehr rechenintensive Aufgaben durchführen. High-Level-Operationen mit sehr geringem Rechenaufwand werden zusammengefasst und auf programmierbaren, eingebetteten Prozessoren ausgeführt. Dabei sind Regularität und Autonomie von geringerer Bedeutung.

Bei der Fußgängererkennung zeigt sich, wie bei vielen modernen Algorithmen, ein nachhaltiger Trend hin zu immer komplexeren Entscheidungs-abläufen. Für die Verarbeitungseinheiten bedeutet dies zum einen, dass die Rechenleistung für die High-Level-Verarbeitung nicht mehr durch einzelne Prozessoren bereitgestellt werden kann. Zum anderen steigt die Zahl und Komplexität der Steuereingriffe in der Low-Level-Datenverarbeitung. Dadurch müssen Operationen viel feingranularer aufgeteilt werden. Gleichzeitig nimmt die Anzahl und Komplexität der Teilverfahren zu, die in einem Algorithmus integriert sind.

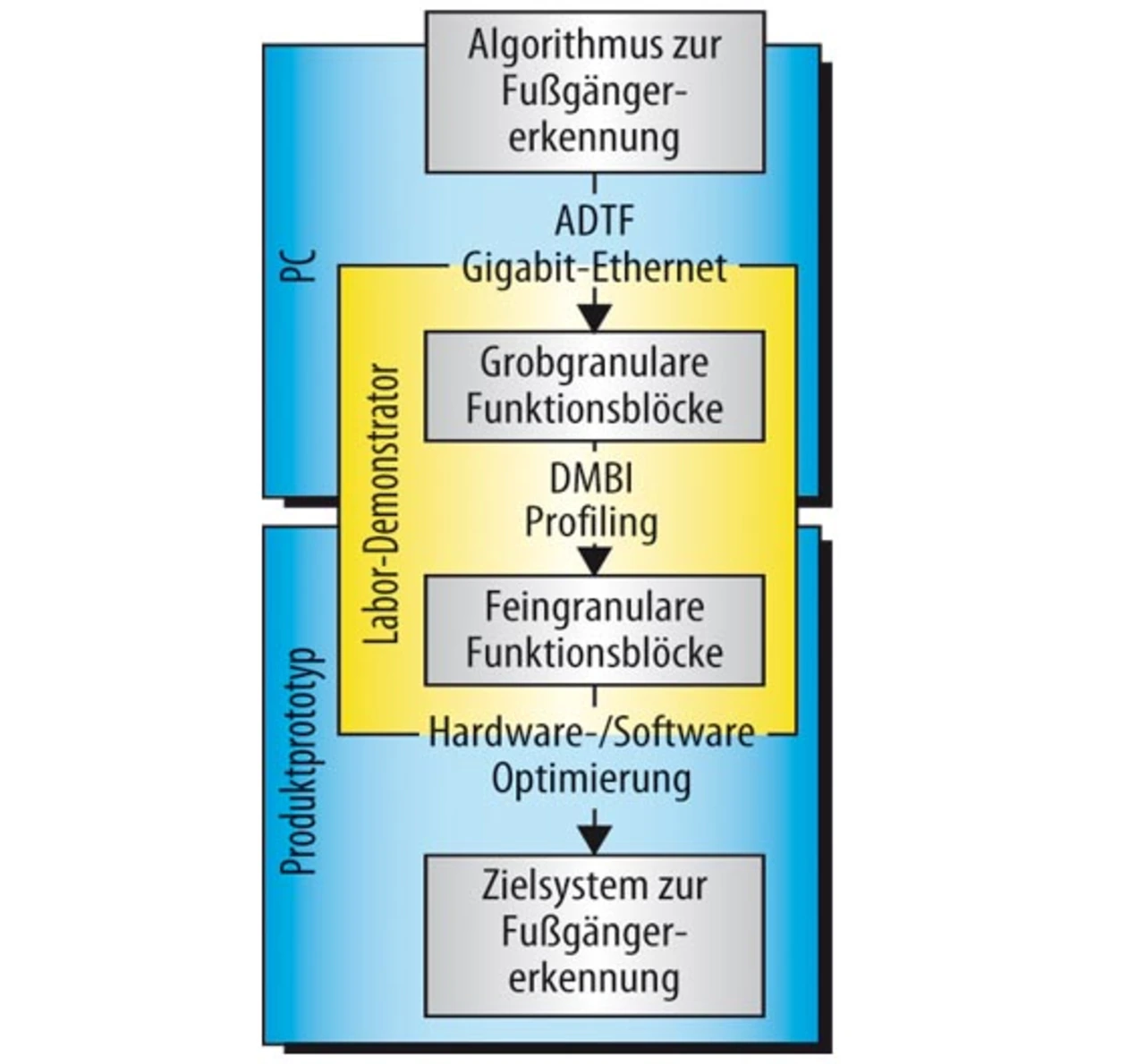

Daher wurde ein konsistenter und effizienter Entwurfsablauf gewählt, der die schrittweise Umsetzung meist sehr abstrakter, komplett in Software erfolgter Beschreibungen in eine adäquat partitionierte Implementierung unterstützt. Der Weg von der Referenzimplementierung zum Produktprototypen wurde dazu durch Einsatz eines HiL-Systems (Hardware-in-the-Loop) als Zwischenschritt vereinfacht (Bild 4).

- Mehr Sicherheit für Fußgänger

- Nachtsichtassistenten der nächsten Generation

- NIR-Radar

- NIR-FIR

- Fusionsverfahren

- In Propedes entwickelte Software-/Hardware-Architekturen für mehr Rechenleistung

- Anbindung an das ADTF-Framework

- Optimale Partitionierung der Videoalgorithmen

- Applikationsspezifisch konfigurierbare Soft-Core-Prozessoren

- Umsetzung auf Multi-FPGA-Hardware-Plattform

- FPGA-basierter Ansatz bietet viel Potential

- Die Autoren