Forschungsprojekt Propedes

Mehr Sicherheit für Fußgänger

Fortsetzung des Artikels von Teil 7

Optimale Partitionierung der Videoalgorithmen

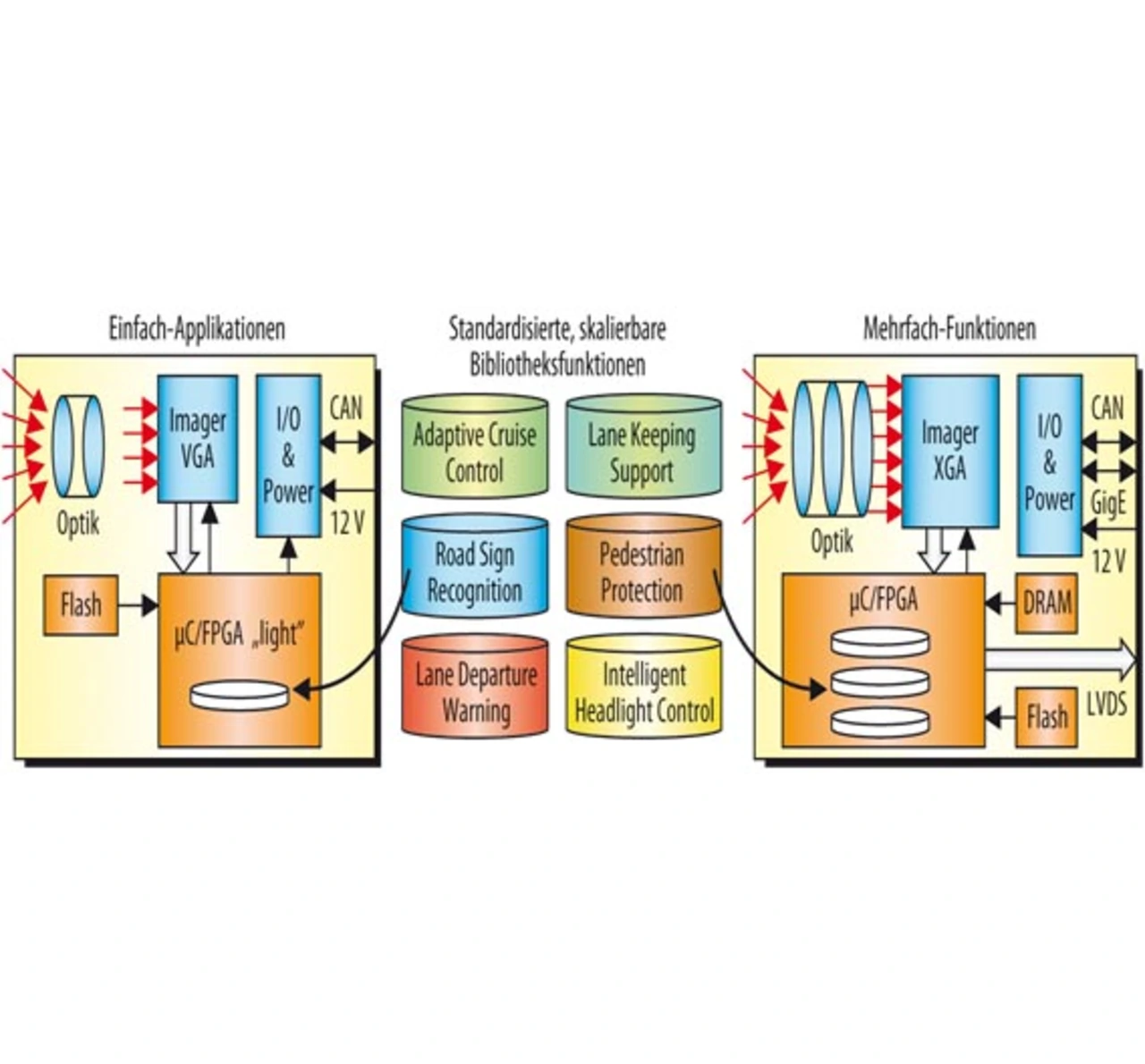

Für Feldversuche im fahrenden Auto hat die Robert Bosch GmbH einen zweiten Funktionsdemonstrator mit dem Ziel entwickelt, eine optimale Partitionierung der Videoalgorithmen unter seriennahen Randbedingungen und vorgegebenen Hardware-Architekturen zu finden. Dabei wurde das Grundkonzept eines skalierbaren Videorechners mit dedizierten FPGA- und Mikroprozessor-Komponenten unter dem Aspekt einer maximalen Wiederverwendbarkeit modular entwickelter Software-Komponenten stetig optimiert und verfeinert. Die Grobsortierung und Aufteilung der Algorithmen für eine Implementierung in Hardware-Beschleunigern (FPGA) bzw. Software (Mikroprozessor) wurde iterativ in einer Vielzahl von Portierungsschritten durchgeführt, wobei insbesondere Aspekte wie Echtzeitfähigkeit, Ausnutzung der vorhandenen Ressourcen und möglichst einfache Validierungsverfahren eine wichtige Rolle spielten. Als finale Videorechner für den Serieneinsatz sind entsprechende FPGAs mit eingebetteten Prozessoren vorgesehen, die auf wiederverwendbare, bereits vorpartitionierte Module für FPGA und Prozessor zugreifen können (Bild 6).

- Mehr Sicherheit für Fußgänger

- Nachtsichtassistenten der nächsten Generation

- NIR-Radar

- NIR-FIR

- Fusionsverfahren

- In Propedes entwickelte Software-/Hardware-Architekturen für mehr Rechenleistung

- Anbindung an das ADTF-Framework

- Optimale Partitionierung der Videoalgorithmen

- Applikationsspezifisch konfigurierbare Soft-Core-Prozessoren

- Umsetzung auf Multi-FPGA-Hardware-Plattform

- FPGA-basierter Ansatz bietet viel Potential

- Die Autoren