Systemdesign / Co-Simulation

Von der Idee zum Prototyp - schnell, flexibel und effizient

Fortsetzung des Artikels von Teil 3

Synthese auf dem FPGA

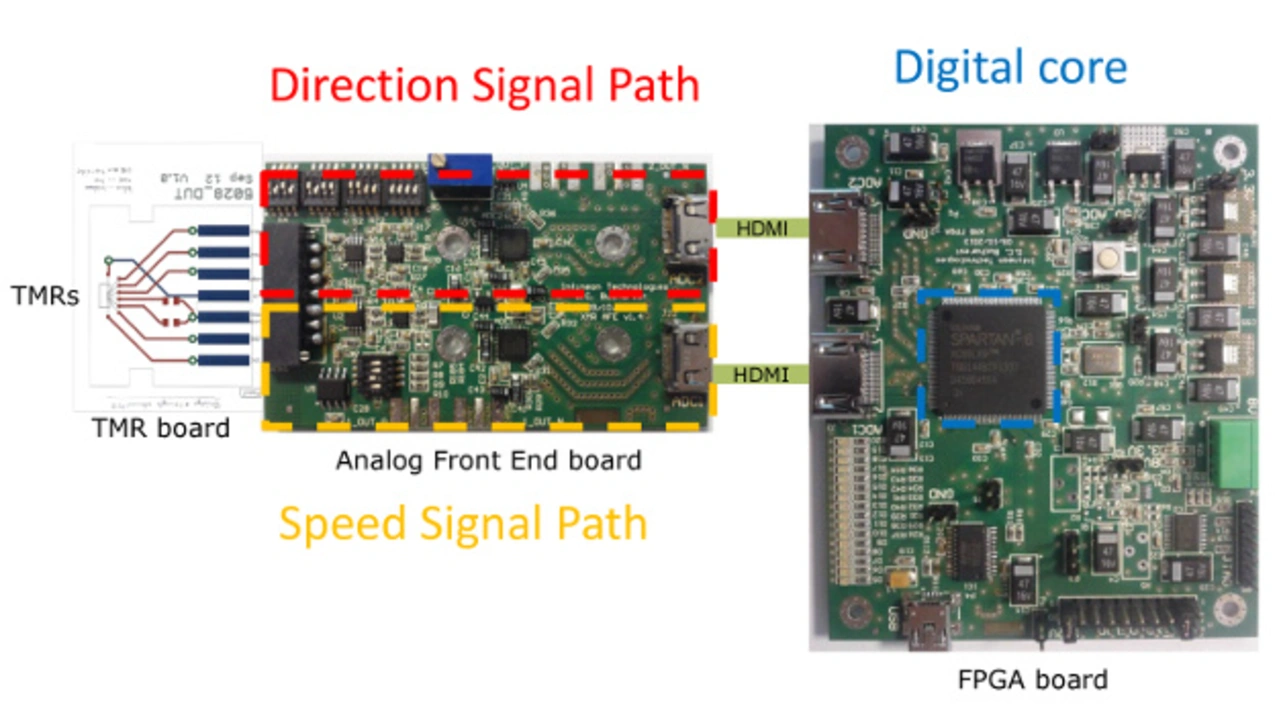

Nach Validierung des HDL-Codes im vorherigen Schritt, war es möglich, die reale Hardware zu entwerfen. Die im Labor verwendete Hardware bestand aus drei Platinen: xMR-Board, AFE-Platine (Analoges Frontend) und FPGA-Board (Bild 6).

Das xMR-Board besteht aus Silizium-Dies mit einem oder mehreren Sensorelementen (GMR oder TMR), die auf einer kleinen Leiterplatte gebondet sind. Die Leiterplatte wird dann an das AFE angeschlossen. Die AFE-Platine modelliert das analoge Front-End eines Geschwindigkeitssensors mit kaskadierten Verstärkern und Analog-Digital-Wandlern. Dieses Board ist teilweise über DIP-Schalter konfigurierbar:

sowohl die Verstärkungen als auch die Sensorelement-Konfigurationen sind änderbar. Schließlich wird auf der FPGA-Platine der digitale Kern der Sensoren implementiert. Das Board verwendet ein Xilinx Spartan 6 FPGA und bietet einige Eingangs- und Ausgangs-Pins für Sensorkonfiguration und Debugging. In Zukunft könnten einige weitere Optionen in Betracht kommen: etwa ein programmierbares Frontend statt AFE-Platine, oder ein System-on-Chip statt FPGA.

Automatischer Vergleich

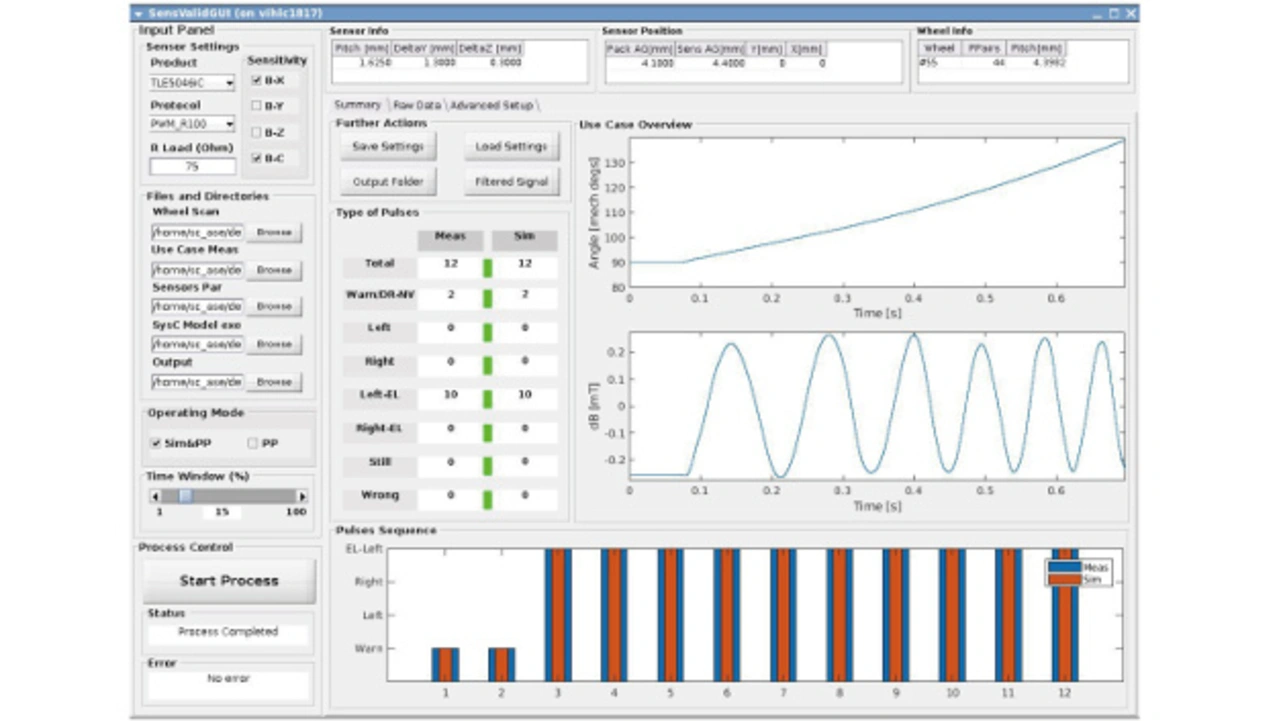

Schließlich wird im Rahmen der neuen Methodik eine automatisierte Co-Verifizierung der Hardware des goldenen Referenzmodells für SystemC durchgeführt. Die Validierungsmethode wird durch den folgenden Arbeitsablauf beschrieben: sowohl die Ausgänge als auch die Stimuli des Systems werden gemessen. Für die Simulation werden dem Modell, die zuvor auf dem realen Prüfstand gemessenen Stimuli, zur Verfügung gestellt.

Ein Algorithmus leistet die Nachverarbeitung der Daten, die sowohl von der Hardware als auch von der Software stammen, um die Stimuli zu erzeugen und den endgültigen Vergleich zu ermöglichen. Anschließend werden die nachverarbeiteten Daten erfasst und nach vordefinierten Validierungskriterien bewertet. Somit wird die Hardware gegenüber dem Modell überprüft und eventuelle Fehlanpassungen identifiziert. Bild 7 zeigt die grafische Benutzeroberfläche (GUI) der Co-Verifizierungsumgebung.

Jobangebote+ passend zum Thema

- Von der Idee zum Prototyp - schnell, flexibel und effizient

- Sensorentwicklung in SystemC

- Automatische HDL-Übersetzung

- Synthese auf dem FPGA

- Ergebnisse und Schlussfolgerung