Hardwaregestützte IC-Verifikation

Ein System für virtuelle Plattformen, Emulation und Prototyping

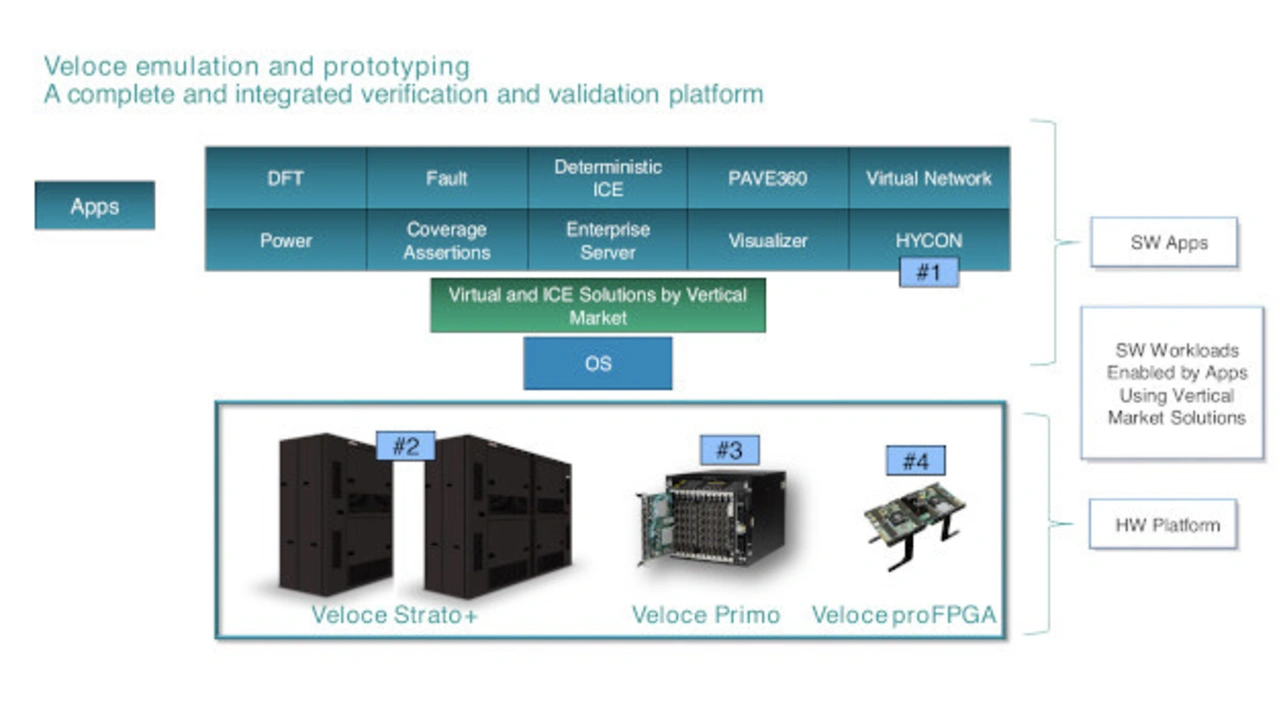

Mit seiner neuen Generation des hardwareunterstützten IC-Verifikationssystems Veloce schafft Siemens Digital Industries erstmals ein integriertes Komplettangebot. Es kombiniert Techniken für virtuelle Plattformen, Hardware-Emulation und FPGA-Prototyping.

Neu im Hardware-unterstützten Verifikationssystem Veloce von Siemens Digital Industries sind:

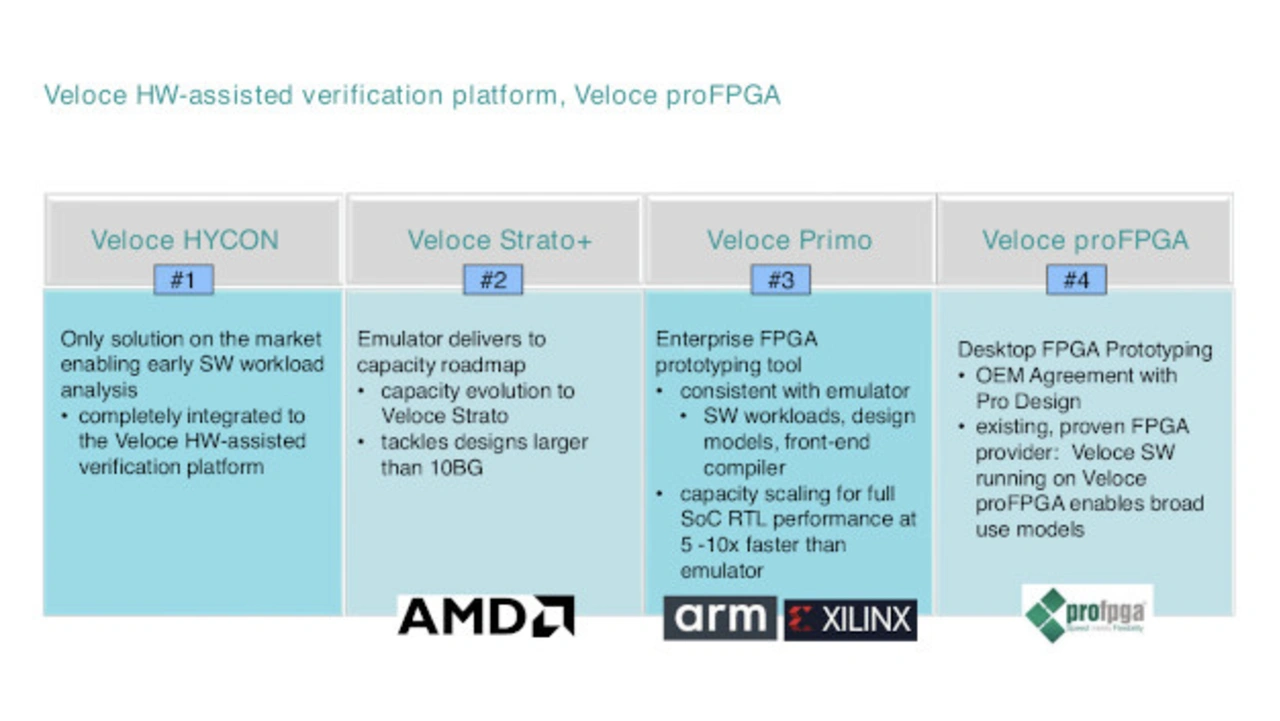

- Veloce HYCON (HYbrid CONfigurable) für virtuelle Plattform-/Software-gestützte Verifikation. Veloce HYCON ermöglicht es IC-Entwicklern, komplexe hybride Emulationssysteme für ihre System-on-Chip-Entwürfe der nächsten Generation zu entwickeln und einzusetzen.

- Veloce Strato+, eine Kapazitätserweiterung für den Veloce Strato Hardware-Emulator. Mit einer Kapazität von bis zu 15 Mrd. Gattern, kombiniert Veloce Strato+ hohen Gesamtdurchsatz mit hoher Co-Modell-Bandbreite und kurzer Zeit zum Überprüfen der Ergebnisse (Time to Visibility).

- Veloce Primo für FPGA-Prototyping auf Unternehmensebene, mit branchenweit führender Laufzeitleistung und außergewöhnlich schnellem Prototyping.

- Veloce proFPGA für Desktop-FPGA-Prototyping. Dank des modularen Konzepts erlaubt Veloce proFPGA eine Anpassung der Kapazität an die Anforderungen der IC-Entwickler.

Jobangebote+ passend zum Thema

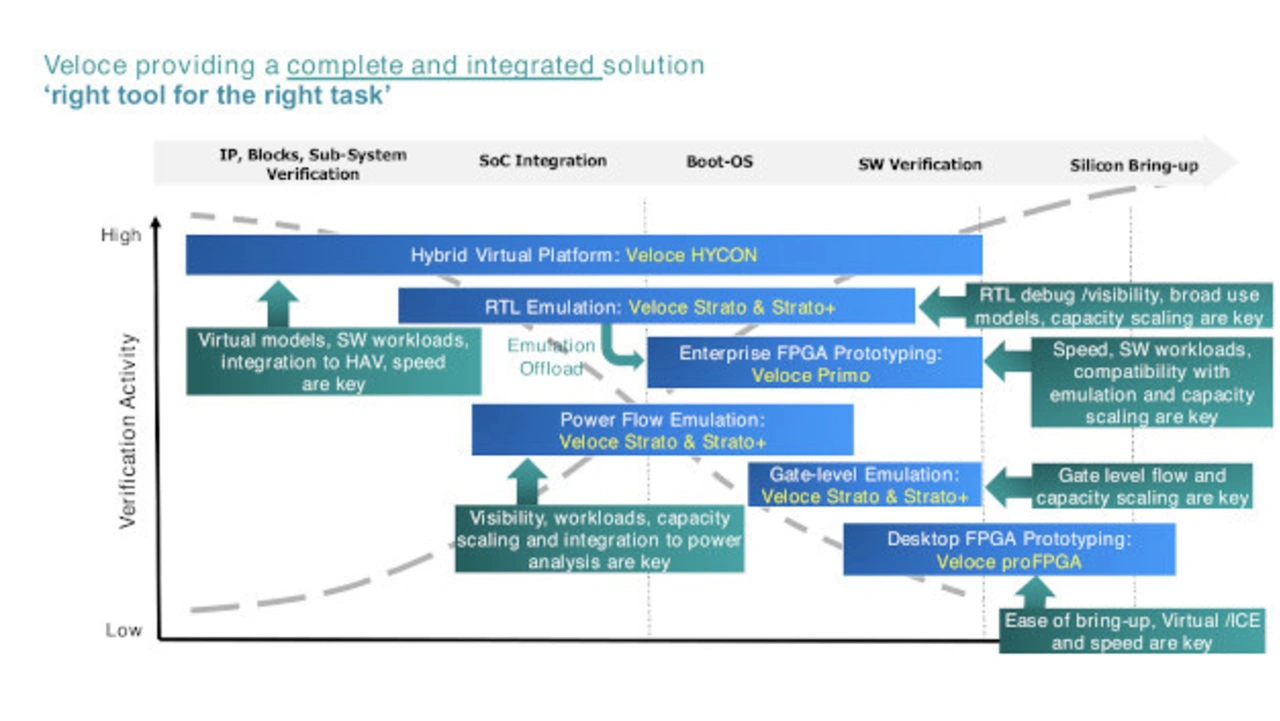

Mit diesem hochgradig kohärenten System will Siemens Digital Industries einen neuen Standard für die zukünftige Richtung der hardwaregestützten Verifikationsmethoden setzen. Veloce soll die Hardware-, Software- und Systemverifikation auf die nächste Stufe der Digitalisierung heben, indem es die Verifikationszyklen rationalisiert und gleichzeitig hilft, die Verifikationskosten zu senken.

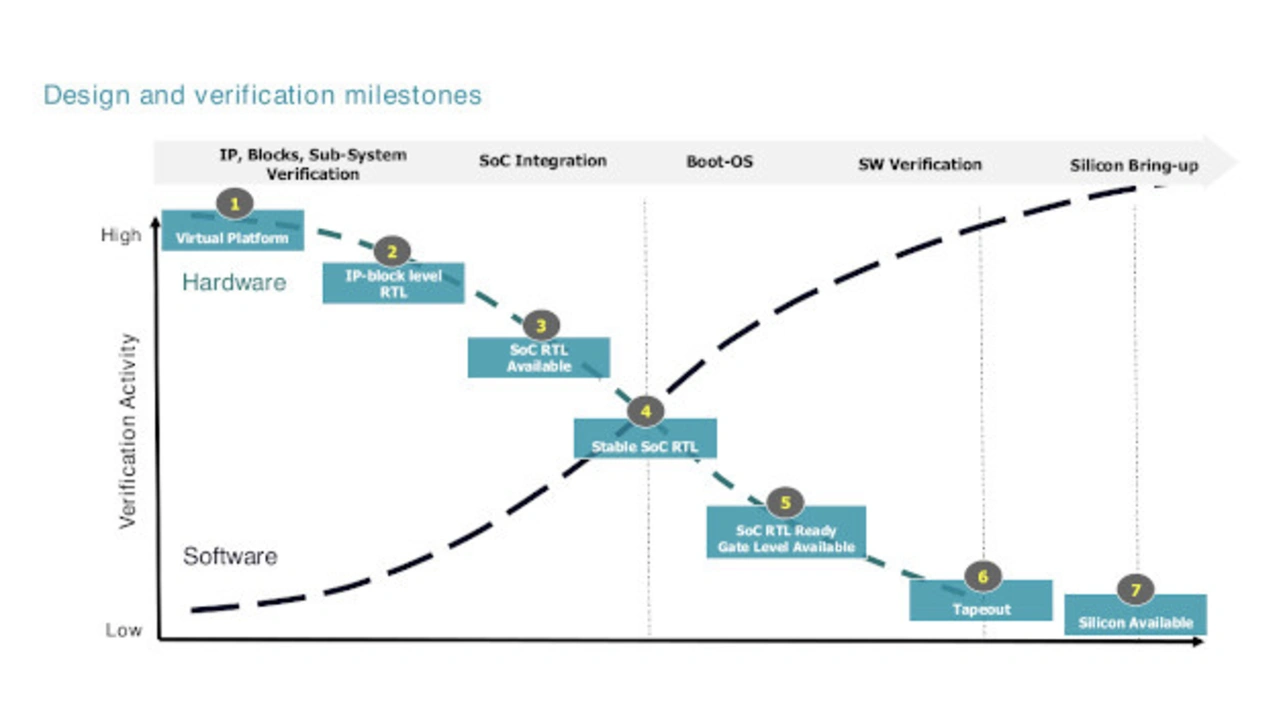

Früh mit realer Software verifizieren

Dieser nahtlose Ansatz zur Verwaltung von Verifikationszyklen legt den Schwerpunkt auf die Ausführung von marktspezifischen, realen Arbeitslasten, Frameworks und Benchmarks zu Beginn des Verifikationszyklus für die Energie- und Leistungsanalyse. Dies ermöglicht es IC-Entwicklern, virtuelle SoC-Modelle zu einem frühen Zeitpunkt im Zyklus zu erstellen und mit der Integration realer Firmware und Software auf Veloce Strato+ zu beginnen, um einen tiefen Einblick in die unterste Ebene der Hardware zu erhalten. IC-Entwickler können dann den Entwurf auf Veloce Primo verschieben, um die Software/Hardware-Schnittstellen zu validieren und Software auf Anwendungsebene auszuführen, womit sie näher an den tatsächlichen Systemgeschwindigkeiten arbeiten.

Um diesen Ansatz so effizient wie möglich zu gestalten, verwenden Veloce Strato+ und Veloce Primo dieselbe RTL-Datei, dieselbe virtuelle Verifikationsumgebung, dieselben Transaktoren und Modelle, um die Wiederverwendung von Verifikationsmaterial, Umgebung und Testinhalten zu maximieren. Dies ist eine notwendige Grundlage für eine nahtlose Methodik.

Erweiterter Emulator Veloce Strato+

Innovationen in der IC-, System- und Software-Entwicklung ermöglichen es Siemens Digital Industries mit dem Veloce Strato+, die Kapazitäts-Roadmap zu erfüllen, die 2017 bei der Einführung der Veloce-Strato-Plattform veröffentlicht wurde. Der zentrale Baustein, ein »Crystal 3+« genanntes SIP – ein 2,5D-Multi-Chip-Modul –, erhöht die Systemkapazität um das 1,5-fache gegenüber dem vorherigen Veloce-Strato-System. Dank dieser Innovation ist der Veloce Strato+ mit einer verfügbaren Kapazität von 15 Mrd. Gattern führend auf dem Emulationsmarkt.

»Mit dem Eintritt in den neuen Halbleiter-Megazyklus erfordert die Ära des Software-zentrierten SoC-Entwurfs einen dramatischen Wandel bei den funktionalen Verifikationssystemen, um den neuen Anforderungen gerecht zu werden«, sagte Ravi Subramanian, Senior Vice President und General Manager, Siemens EDA. »Die Einführung des Veloce-Systems der nächsten Generation, das diese wichtigen neuen Anforderungen adressiert, ist ein direktes Ergebnis der gezielten Investitionen von Siemens, um unseren Kunden ein komplettes, integriertes System mit einer klaren Roadmap für das nächste Jahrzehnt zu bieten.«

»AMD nutzt die Veloce-Emulationsplattformen als Teil unserer Pre-Silicon-Verifikations- und Validierungslösungen«, sagte Alex Starr, Corporate Fellow, Methodology Architect, AMD »Die Hochleistungsdesigns, die wir entwickeln, erfordern skalierbare, zuverlässige und innovative Emulationslösungen. Wir freuen uns, dass wir mit Siemens zusammenarbeiten, um den Einsatz des Veloce-Strato+-Systems mit hoher Kapazität bei AMD zu ermöglichen. Darüber hinaus freuen wir uns, dass AMD EPYC Prozessoren der 2. und 3. Generation für den Einsatz mit Veloce-Strato- und Veloce-Strato+-Plattformen qualifiziert sind. Die Hochleistungsfähigkeiten beider Prozessorfamilien bringen dem Veloce-Ökosystem und seinen Kunden, wie AMD, ein neues Maß an Produktivität.«

Das Veloce-Strato-System erweitert außerdem die Liste der qualifizierten Prozessoren, indem es ab heute die AMD EPYC 7003 Prozessorserie hinzufügt. Diese neuen Prozessoren sind vollständig qualifiziert, um mit den Veloce-Strato-Systemen als Runtime-Hosts und Co-Model-Hosts zu laufen.

FPGA-Prototyping mit anpassbarer Kapazität

Veloce Primo und Veloce proFPGA stellen den branchenweit leistungsfähigsten und vielseitigsten Ansatz für FPGA-Prototyping dar. Das FPGA-Prototyping-System auf Unternehmensebene, Veloce Primo, bietet gleichzeitig eine herausragende Leistung mit einer Kapazität von bis zu 320 FPGAs und ein konsistentes Arbeitsmodell mit Veloce Strato in Bezug auf Software-Arbeitslasten, Entwurfsmodelle und Kompilierung. Diese grundlegende Abstimmung zwischen Emulation und Prototyping trägt dazu bei, die Kosten der Verifikation zu reduzieren, indem das richtige Werkzeug für die jeweilige Aufgabe eingesetzt wird, wobei Emulation und Prototyping komplementär zusammenarbeiten, um ein besseres Ergebnis in einem kürzeren Zyklus zu erzielen. Veloce Primo unterstützt außerdem sowohl virtuelle als auch In-Circuit-Emulations-Modelle für höchstmögliche Leistung unter Beibehaltung genauer Taktverhältnisse in beiden Modi.

»Die steigende Nachfrage nach Computing in allen Branchen bedeutet, dass die Zeit bis zur Markteinführung entscheidend ist«, sagte Tran Nguyen, Senior Director of Design Services bei ARM. »Die Enterprise-FPGA-Prototyping-Lösung Veloce Primo von Siemens hilft ARM, Entwurfs-Probleme schnell zu lösen und Verifikationsziele zu erreichen, damit unser Wirtschaftsökosystem qualitativ hochwertige ARM-basierte SoCs liefern kann, um das schnelle Innovationstempo zu unterstützen.«

»Wir freuen uns, Siemens mit der Einführung von Veloce Primo auf dem FPGA-Prototyping-Markt begrüßen zu dürfen«, sagte Hanneke Krekels, Senior Director, Core Vertical Markets, bei Xilinx. »Xilinx hat eine langjährige Beziehung zu Siemens, sowohl als Kunde als auch als Kooperationspartner, und wir freuen uns, dass wir unser jüngstes und branchenführendes Virtex UltraScale+ VU19P-Bauteil, das Skalierbarkeit und Kapazität ermöglicht, in dieses neue Produktangebot einbringen können.«

Veloce proFPGA ist eine bewährte Desktop-Plattform, die von Pro Design (OEM) für das hardwaregestützte Verifikationssystem Veloce übernommen wurde. Sie ist modular konzipiert, für eine Kapazität von 40 M Gattern bis 800 M Gattern, und basiert auf High-End-FPGAs einschließlich Stratix 10 GX 10M von Intel und Virtex UltraScale+ VU19P von Xilinx.

»Die fortschrittliche Technik der proFPGA-Familie bietet viele Vorteile für die Validierung heutiger AI/ML-, 5G- und Rechenzentrums-ASIC-Designs«, sagt Gunnar Scholl, CEO von Pro Design. »Wir freuen uns sehr über die Partnerschaft mit Siemens. Unsere kollektive Erfahrung, unser Wissen und unsere Strategie für den FPGA-Desktop-Prototyping-Markt werden anerkannt, und wir freuen uns darauf, die Marktdurchdringung in diesem Bereich durch die Zusammenarbeit mit Siemens zu beschleunigen.«