Siemens EDA

Paketbasierter Test reduziert Aufwand bei DFT

Das Tessent Streaming Scan Network (SSN) von Siemens EDA entkoppelt DFT-Anforderungen auf Kern- und Chipebene, ermöglicht per IJTAG parallele Tests und optimiert die Bandbreitennutzung. So sinken Designkomplexität, Fülldatenmenge und Testkosten deutlich.

DFT-Manager müssen häufig schwierige, manchmal kostspielige Kompromisse zwischen dem Aufwand für die Testimplementierung und den Testkosten in der Fertigung eingehen. Die traditionelle Methode zur Bewertung dieser Abwägungen war die Verwendung hierarchischer DFT-Methoden in einem Teile-und-herrsche-Ansatz. Bei hierarchischen DFT-Verfahren erfolgt die gesamte Umsetzung, einschließlich der Mustererstellung und -verifizierung, auf Kernebene. Dies bringt einige Herausforderungen mit sich.

Um eine Gruppe von Kernen simultan mit dem Pin-Multiplex-Scan-Verfahren zu testen, werden die Ein- und Ausgänge der Scankanäle direkt über einen Satz von Multiplexern mit einer festgelegten Anzahl an Chip-Level-Pins verbunden. Welche Kerne simultan getestet werden können, hängt von dem Multiplexer-Netzwerk ab, welches in einem frühen Stadium des Design-Flows festgelegt werden muss. Zugriffskonfigurationen müssen erstellt werden, wenn mehr Kerne und/oder Chip-Level-Pins zum Testen zur Verfügung stehen. Dies wirkt sich auf den Aufwand für die DFT-Implementierung, die Siliziumfläche, die Komplexität des Pattern-Retargetings und die Testzeit aus.

Das kachelbasierte Layout sorgt für eine höhere Komplexität und Einschränkungen der DFT-Architekturen. Die Kerne sind so konzipiert, dass sie aneinanderstoßen und die Verbindungen von einem Kern zum nächsten verlaufen. Dadurch wird das Top-Level-Routing praktisch eliminiert. Jede Verbindung zwischen den Kernen muss durch die Kerne fließen, die sich dazwischen befinden.

Diese Einschränkungen können durch einen paketbasierten Testübertragungsmechanismus effektiver verwaltet werden, bei dem die DFT-Anforderungen auf Kern- und Chipebene entkoppelt werden. Genau einen solchen Übertragungsmechanismus bietet das Tessent Streaming Scan Network (SSN) von Siemens EDA. Tessent SSN ermöglicht eine von den IO-Beschränkungen der Chips gänzlich unabhängige Komprimierungskonfiguration auf Kernebene. Simultan getestete Kerne werden durch IJTAG-Programmierung aktiviert, nicht durch feste Verdrahtung. Dieser Ansatz reduziert den Aufwand für DFT-Planung und Implementierung drastisch.

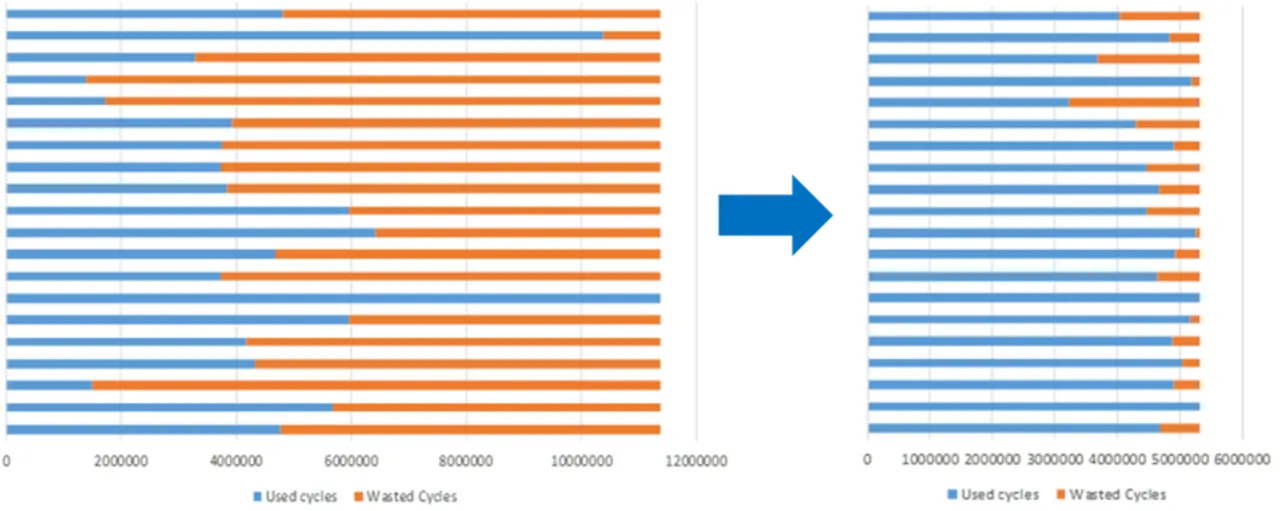

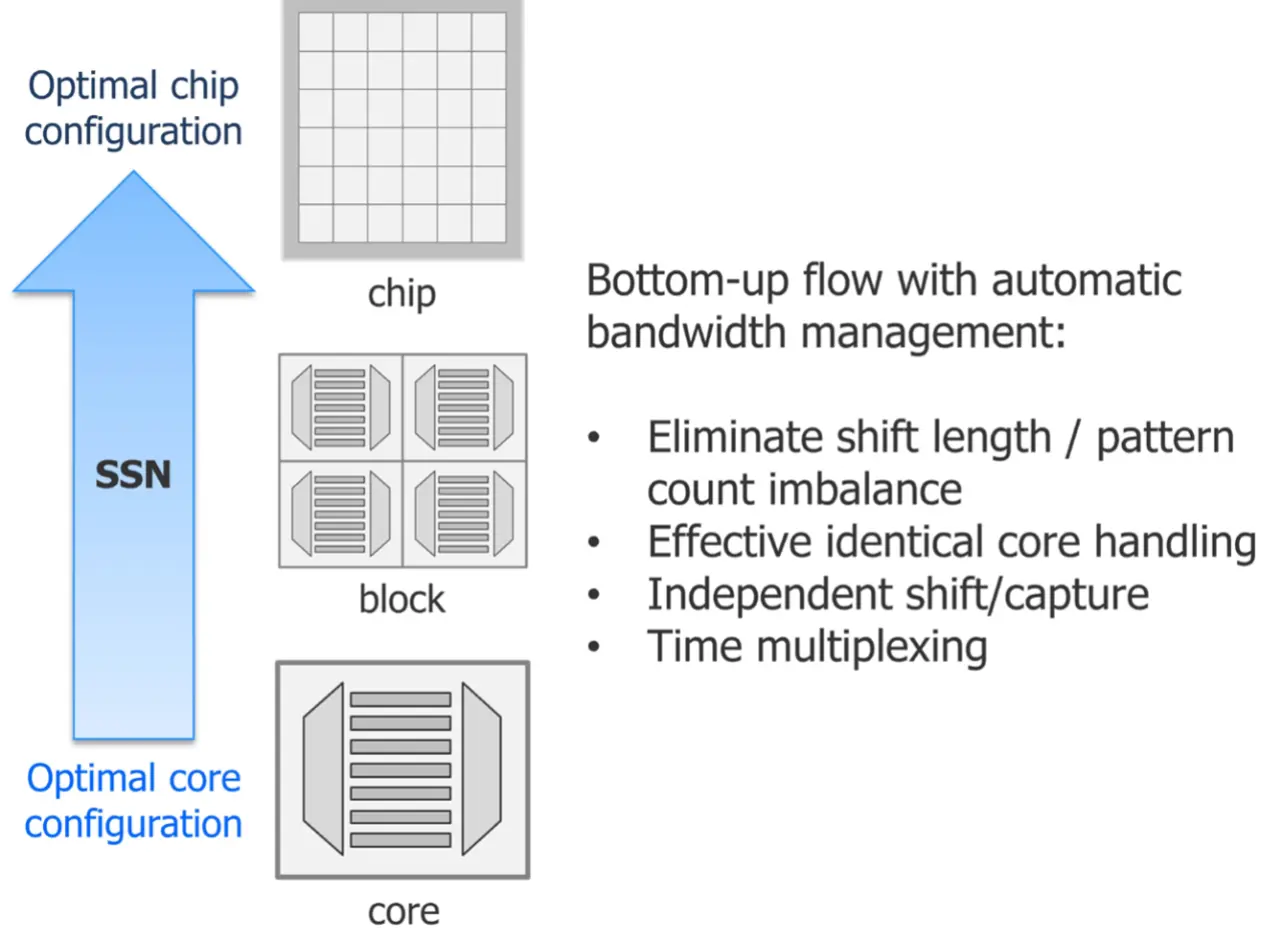

Mit Tessent SSN werden die Komprimierung und die Anzahl der Scankanäle für einen Kern anhand des kompaktesten Musters für diesen Kern bestimmt. Die Scankomprimierung kann einmalig und für alle in mehreren Designs verwendeten Kerne konfiguriert werden. SSN verteilt die verfügbare Netzwerkbandbreite automatisch auf die aktiven Kerne basierend auf dem Scanmustervolumen für jeden Kern, wodurch Leerräume in den Testdaten eliminiert werden (Bild 1).

Jobangebote+ passend zum Thema

Die Balken links in Bild 1 stellen das Scanmuster-Retargeting ohne SSN dar. Die Balken rechts stellen das Scanmuster-Retargeting mit SSN dar. Jeder Balken steht für einen Kern; die Länge jedes Balkens ist repräsentativ für die Scandaten jedes Kerns, die an das Kern-Retargeting geliefert werden. Blau sind Scandaten und orange sind Fülldaten (Padding). Es gibt viel Orange, weil viele Kerne weniger Scandaten haben als die beiden langen blauen Kerne. Solange das Retargeting des Scanmusters läuft, während die blauen Kerne laufen, müssen auch die orangefarbenen Kerne laufen, sodass zunächst viele Nullen anfallen (z. B. Fülldaten, Padding), bis die blauen Kerne ihre Scandaten erhalten.

Das Bild auf der rechten Seite zeigt, wie SSN das Retargeting des Scanmusters verändert. Es ist viel weniger Orange zu sehen, da SSN die Netzwerkbandbreite automatisch von den Kernen, die weniger Bandbreite benötigen, zu jenen Kernen überträgt, die viel Bandbreite benötigen, wodurch Fülldaten/Padding beseitigt werden.

Anstatt den DFT-Implementierungsaufwand und die Fertigungstestkosten gegeneinander abwägen zu müssen, lassen sich mit SSN die optimale Testdatenzeit und das optimale Testdatenvolumen für ein System-on-a-Chip (SoC) ohne teure Design-Iterationen erzielen.

Wie funktioniert das?

Viele SoCs, die durch parallele Verarbeitung einen hohen Durchsatz erreichen, enthalten zahlreiche mehrfach replizierte Kerne. Beim Scannen von Multiplex-Pinarchitekturen können die Scan-Eingangsdaten an identische Kerninstanstanzen übertragen werden. Die Scan-Ausgangsdaten werden in der Regel unabhängig beobachtet, um ein verlustfreies Mapping und die Beobachtbarkeit für die Diagnose zu gewährleisten.

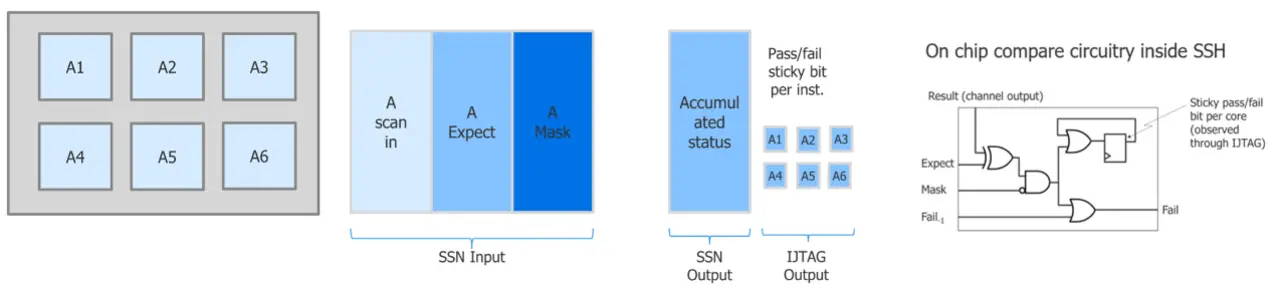

Bei Tessent SSN handelt es sich um eine bus-basierte Scandaten-Verteilungsarchitektur. Sie bietet eine skalierbare Methode zur gleichzeitigen Prüfung einer beliebigen Anzahl identischer und nicht identischer Kerne. Unabhängig von der Anzahl der verfügbaren Chip-Level-Pins ermöglicht sie das Testen identischer Kerninstanzen in nahezu konstanter Testzeit. Wie in Bild 3 dargestellt, werden Eingangsdaten, erwartete Antworten und Vergleichs-/Nichtvergleichsmaskendaten in jedem Paket bereitgestellt und gescannt.

Jede identische Kerninstanz verwendet die selben Paketdaten, während sie sich synchron durch das Netzwerk bewegt. Jeder Kern führt seinen On-Chip-Vergleich durch. Mit dem On-Chip-Vergleich können die »gleichen Paketdaten« für mehrere identische Kerne verwendet werden. Die Sticky-Status-Bits befinden sich in jedem Kern und zeigen eindeutig an, welcher Kern ausgefallen ist, anders als bei zusammenfassenden Daten, die aussagen, dass etwas ausgefallen ist.

Implementierung von Tessent SSN in einem Design

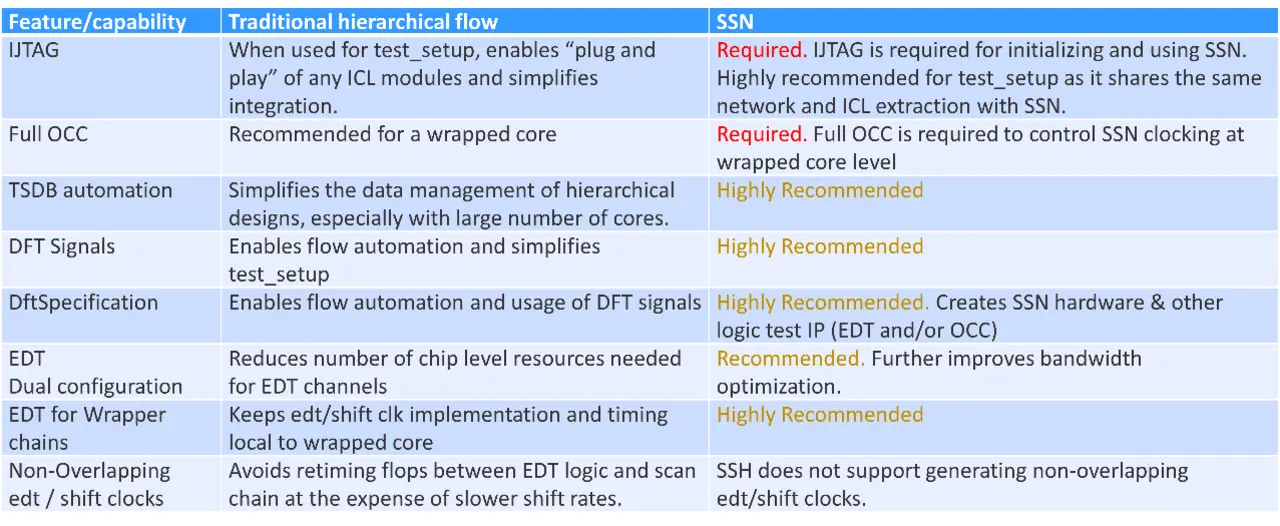

Die Tabelle fasst die Anforderungen und Empfehlungen für die Implementierung von SSN in einem Design zusammen. Zum Beispiel ist eine IJTAG-Infrastruktur erforderlich, um die SSN-Schaltung zu programmieren. Für unabhängige Shift- und Capture-Vorgänge wird ein standardmäßiger On-Chip-Taktcontroller benötigt. Dieser kann von Tessent oder einem Drittanbieter bezogen werden.

Zwei Dinge sind in der Planungsphase zu berücksichtigten: Zunächst sollte die Komprimierung auf Kernebene optimiert werden, um die besten Ergebnisse für diesen Kern in der Isolation zu erzielen (z.B. den kompaktesten Mustersatz). Es besteht keine Notwendigkeit, Ressourcen auf Chipebene oder die geplante SSN-Busbreite zu beachten. Zweitens sollte der SSN-Bus auf Chipebene basierend auf der Anzahl der verfügbaren Pins und dem Blockdiagramm des Entwurfs konzipiert werden. Der SSN-Datenpfad ist so zu planen, dass er alle physikalischen Bereiche des Designs durchläuft. Die Scan-Eingänge und -Ausgänge, die für das Nicht-SSN-Design genutzt werden, sind als Ein- und Ausgänge für den parallelen SSN-Datenbus wiederverwendbar. Neben der eigentlichen Konnektivität gilt es, bei Bedarf auch Multiplexer für Debug-Rückpfade und Pipelines entlang des parallelen SSN-Busses einzuplanen, die für den Takt erforderlich sind. Nicht erforderlich ist hingegen, im Voraus zu planen, welche Bereiche des Designs parallel oder in einer bestimmten Reihenfolge ablaufen.

Eine umfassende Reihe von SSN-Verifizierungsfunktionen, einschließlich DRCs, dedizierten Testbenches und Netzwerkintegritätsmustern, steht im gesamten Workflow zur Verfügung. Damit lässt sich sicherstellen, dass potenzielle Probleme oder Fehler frühzeitig erkannt werden, und zwar nach dem SSN-Einbau und vor der Synthese. Im weiteren Ablauf helfen Loopback-Muster dabei, das SSN-Netzwerk bis zu den einzelnen Kernen zu validieren, ohne die Scanmuster vollständig zu simulieren.

Der Ablauf der Fehlerdiagnose ist nahezu identisch mit einem hierarchischen DFT-Ablauf. Auf dem Testgerät erfasste Fehler werden auf Fehler auf Kernebene zurückgeführt. Nach dem Reverse-Mapping erfolgt eine aufs Layout bezogene Diagnose ohne Einschränkungen.

Post-Silizium-Zugang

Tessent SSN kann auch in Post-Silizium-Anwendungen verwendet werden. So kann SSN beispielsweise Umschaltaktivitäten im Design von Zuverlässigkeitstests bei hohen Temperaturen (High-Temperature Operating Life, HTOL) erstellen. Da der SSN-Bus mit einem Single-Bit-SSN-Bus betrieben werden kann, müssen keine speziellen Muster oder Anforderungen an die Leiterplatte erstellt werden.

Neben dem Aufwand für die DFT-Implementierung und dem Testdatenvolumen ist es auch wichtig, die Fehlersuche, Ertragsanalyse und Fehleranalyse (FA) zu erleichtern. SSN umfasst spezielle Funktionen, die sicherstellen, dass etablierte FA-Techniken wie elektrische Fehlerisolierung (Electrical Fault Isolation, EFI) zusammen mit SSN verwendet werden können.

Auf dem jüngsten Internationalen Symposium für Tests und Fehleranalyse (ISTFA 2024) präsentierte Lesly Endrinal, Silicon Failure Analysis Engineering Lead bei Google, Erkenntnisse zur Verwendung von SSN. Das Paper »Solving Complex Electrical Fault Isolation Challenges with Innovative DFT Strategies« (Lösung komplexer Herausforderungen bei der Isolierung elektrischer Fehler mit innovativen DFT-Strategien) stellte neue Funktionen vor, die die Fehleranalyse bei mit SSN getesteten Designs erleichtern sollen. Es wurden drei innovative DFT-Funktionen und -Strategien vorgestellt, die eine elektrische Fehlerisolierung in der SSN-Architektur ermöglichen. Da DFT- und Testtechnologien immer komplexer und unzugänglicher werden, wird es für EDA-Anbieter und -Entwickler von entscheidender Bedeutung, sich ihrer Auswirkungen auf die EFI stärker bewusst zu sein. Eine proaktive Vorgehensweise bei der Entwicklung von Zugängen für FA kann zu einer nahtloseren Feststellung des Ertrags und Fehlersuche im Design führen.

Was sagt die Branche dazu?

Viele andere Branchenführer haben in den letzten Jahren vom erfolgreichen Einsatz von Tessent SSN berichtet. Auf der International Test Conference (ITC) North America 2024 führte Vishal Agarwal, Sr. Director, H/W Engineering bei NVIDIA, aus, wie SSN in ihren anspruchsvollen Designs zum Einsatz kommt. Anurag Jindal, Leiter der DFX-Gruppe bei Ericsson, stellte die Produktivitätssteigerungen durch die Verwendung von Tessent-Produkten, einschließlich SSN, vor. Auf der nordamerikanischen Siemens User2User-Konferenz erklärte Mikey Shahar von Intel: »Intel hat die Testzeit pro Teil erheblich um 10 bis 25 Prozent reduziert, was zu Einsparungen von ca. 50 Millionen Dollar führte.«

Darshan Kobla, Senior Director bei Microsoft und Leiter der Teststrategie für alle Produktsegmente, empfahl in seinem Vortrag auf der ITC NA 2023, bei komplexen Designs den DFT-Aufwand gering und vorhersehbar zu halten. In dieser Präsentation wurde erläutert, wie SSN und Pakettests bei Microsoft erfolgreich eingesetzt wurden. Auf der ITC NA 2022 präsentierte Dan Trock, Principal Engineer bei Amazon Web Services, Erkenntnisse zur Reduzierung von Designaufwand, Testzeit und Leistung mit SSN bei AWS-eigenen Chips.

Fazit

Tessent SSN ermöglicht die gleichzeitige Prüfung einer beliebigen Anzahl von Kernen mit wenigen Chip-Level-Pins. SSN reduziert die Testzeit und das Testdatenvolumen. Damit verfügen DFT-Ingenieure über eine echte SoC-DFT-Lösung, bei der sie keine Kompromisse zwischen Implementierungsaufwand und Fertigungstestkosten machen müssen.