Systemdesign / Co-Simulation

Von der Idee zum Prototyp - schnell, flexibel und effizient

Fortsetzung des Artikels von Teil 2

Automatische HDL-Übersetzung

Beim Schreiben des SystemC-Codes des digitalen Kerns wurde eine erforderliche VHDL-Übersetzung berücksichtigt. Daher wurden alle Sprachkonstrukte, die in SystemC zwar möglich, aber nicht synthetisierbar sind, sowie redundante Datentypen und komplexe C++-Strukturen vermieden.

Um jedes SystemC-Modul des digitalen Kerns in VHDL zu übersetzen, wurde Mentor Catapult verwendet. Das Ergebnis ist ein Satz VHDL-Module mit derselben Hierarchie wie die SystemC-Module.

Insgesamt wurden etwa fünfzehn SystemC-Module konvertiert, die jeweils eine Komplexität von etwa fünfhundert Zeilen Programmcode haben. Ein erfahrener Digital-Designer hätte Monate gebraucht, um das Verhalten des SystemC-Modells für die FPGA-Synthese in HDL zu konvertieren. Mit Mentor Catapult dauerte der Übersetzungsprozess nur etwa einen Tag. Dieser High-Level-Syntheseansatz kann so den Programmieraufwand um Monate reduzieren. Dies ist ein entscheidendes Kriterium für die schnelle Entwicklung von Prototypen.

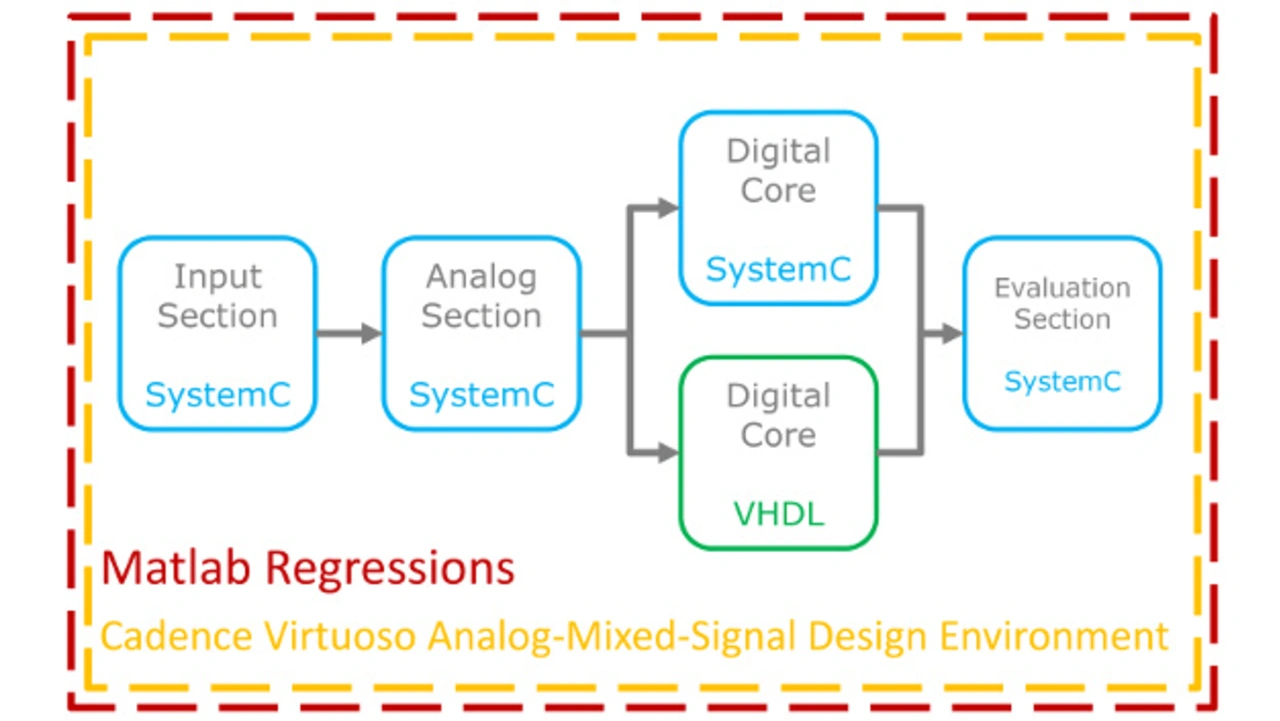

Automatische Co-Simulation von HDL und SystemC

Um die Übersetzung zu überprüfen, simulierte Cadence Virtuoso die VHDL-Übersetzung von digitalem Kern und SystemC-Modell. In Virtuoso wurde ein Schaltplan realisiert und das SystemC-Modul Input Section instanziiert. Der analoge Teil des Sensors wurde in das SystemC-Modul Analog Section eingebunden und mit den von der Input Section kommenden Signalen gespeist. Dasselbe erfolgte für den A/D-Wandler: die Ausgänge der Analog Section und des A/D-Wandlers wurden mit dem digitalen SystemC-Kernmodul und dessen VHDL-Übersetzung verbunden. Die Ausgänge der beiden Digital-Core-Implementierungen (VHDL und SystemC) wurden mit zwei analogen Interface-SystemC-Modulen verbunden. Zwei SystemC-Module Evaluation Section wurden instanziiert, um die Ausgänge der beiden analogen Schnittstellenmodule auszuwerten. Eine vereinfachte Struktur zeigt Bild 4.

Jobangebote+ passend zum Thema

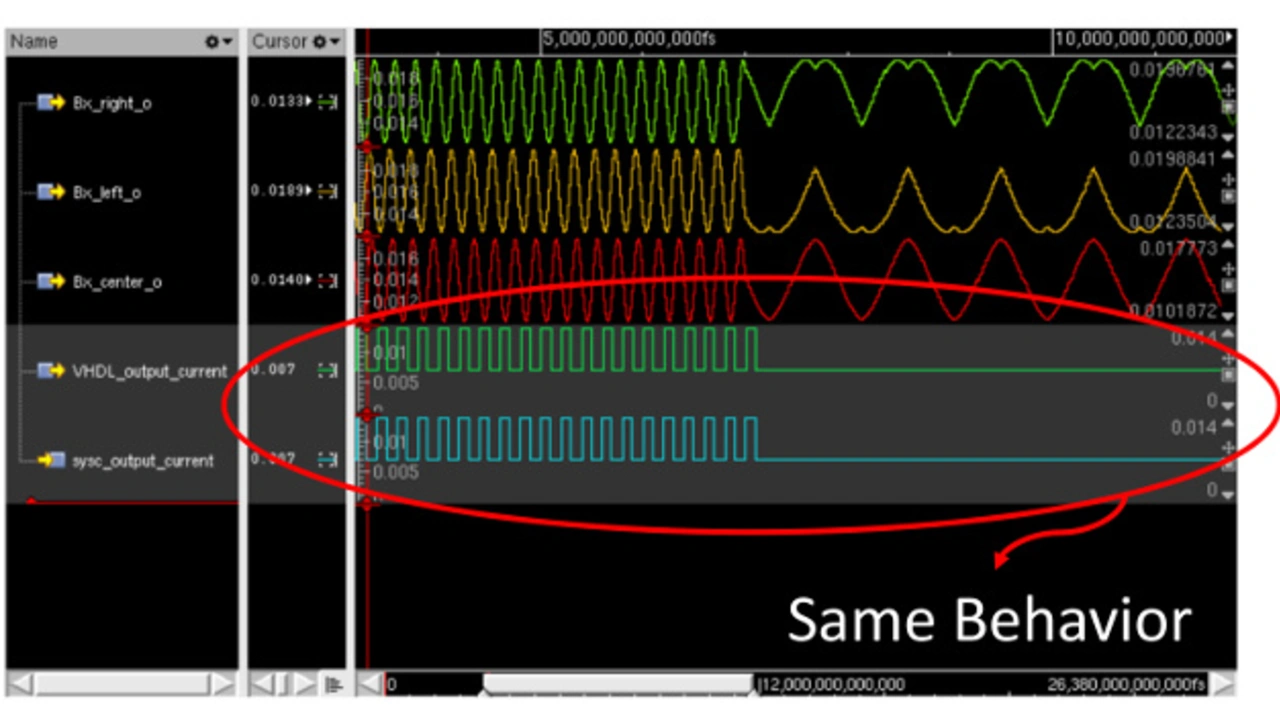

Der beschriebene Ablauf ermöglichte die Co-Simulation des SystemC- und VHDL-Codes des digitalen Kerns unter Verwendung der selben Eingänge und der selben Auswertelogik. Als Ergebnis der Co-Simulation liegen dann zwei verschiedene Reports vor, einer für VHDL und einer für SystemC, welche die Ausgangsimpulse der beiden Ausgangssignale charakterisieren und vergleichen. Bild 5 zeigt Beispielergebnisse für die Co-Simulation.

Die Ergebnisse bestätigten eine korrekte VHDL-Übersetzung und eine hinreichende Übereinstimmung mit dem SystemC-Verhalten, abgesehen von gerinfügigen Timing-Unterschieden: die Ursache liegt in der Implementierung der High-Level-Synthese im Tool. Mit dem Catapult-Tool wurde eine vollständige Übereinstimmung erzielt.

- Von der Idee zum Prototyp - schnell, flexibel und effizient

- Sensorentwicklung in SystemC

- Automatische HDL-Übersetzung

- Synthese auf dem FPGA

- Ergebnisse und Schlussfolgerung