Nachhaltigkeit

Das SSTS-Programm des Imec

Fortsetzung des Artikels von Teil 1

Softwareplattform als virtuelle Fab

Die Grundlage des SSTS-Programms ist die Softwareplattform »imec.netzero«, die das Imec selbst entwickelt hat. Sie fungiert als virtuelle Fab, um einen quantifizierten Bottom-up-Blick auf die IC-Fertigung für eine breite Palette von Technologien einschließlich zukünftiger Technologien zu liefern.

Obwohl imec.netzero ein großartiges Tool ist, um die meisten der großen Probleme der Industrie zu identifizieren, zu dokumentieren und zu klassifizieren, betont das Forschungszentrum, dass die Mitarbeit der Industrie dringend notwendig ist, denn nur dann ist es möglich, auch andere Umweltprobleme aufzudecken, die sich aufgrund ihrer Komplexität der Analyse entziehen. Und auch nur dann können praktische Ansätze für diese Probleme gefunden und ihre Relevanz und Lösbarkeit für die Industrie beurteilt werden.

Dementsprechend arbeitet das Imec bereits jetzt mit Material- und Equipment-Herstellern sowie IDMs und Foundries zusammen, um branchenrelevante Verfahren zu entwickeln, die einerseits die Umweltbelastung reduzieren und gleichzeitig die Leistungsfähigkeit in der Fertigung erhalten. Vorteil des Imec: Die eigene Fabrik dient als Pilotumgebung, um einige der ersten Experimente durchzuführen und ihre Auswirkungen zu bewerten.

Zu den konkreten langfristigen Programmergebnissen gehören die Veröffentlichung von Leitlinien für die Programmteilnehmer, die Erstellung eines konkreten Fahrplans für die Industrie in Richtung Netto-Null, die Festlegung neuer Standards für die Umweltbewertung in der Halbleiterindustrie und die Weitergabe der gewonnenen Erkenntnisse und Daten an die wissenschaftliche Gemeinschaft und die breite Öffentlichkeit. Dabei scheint die größte Herausforderung nicht technischer Natur zu sein, sondern die einfache Tatsache, dass Zeit die knappste Ressource von allen sein könnte.

Jobangebote+ passend zum Thema

Bereits erste Erfolge

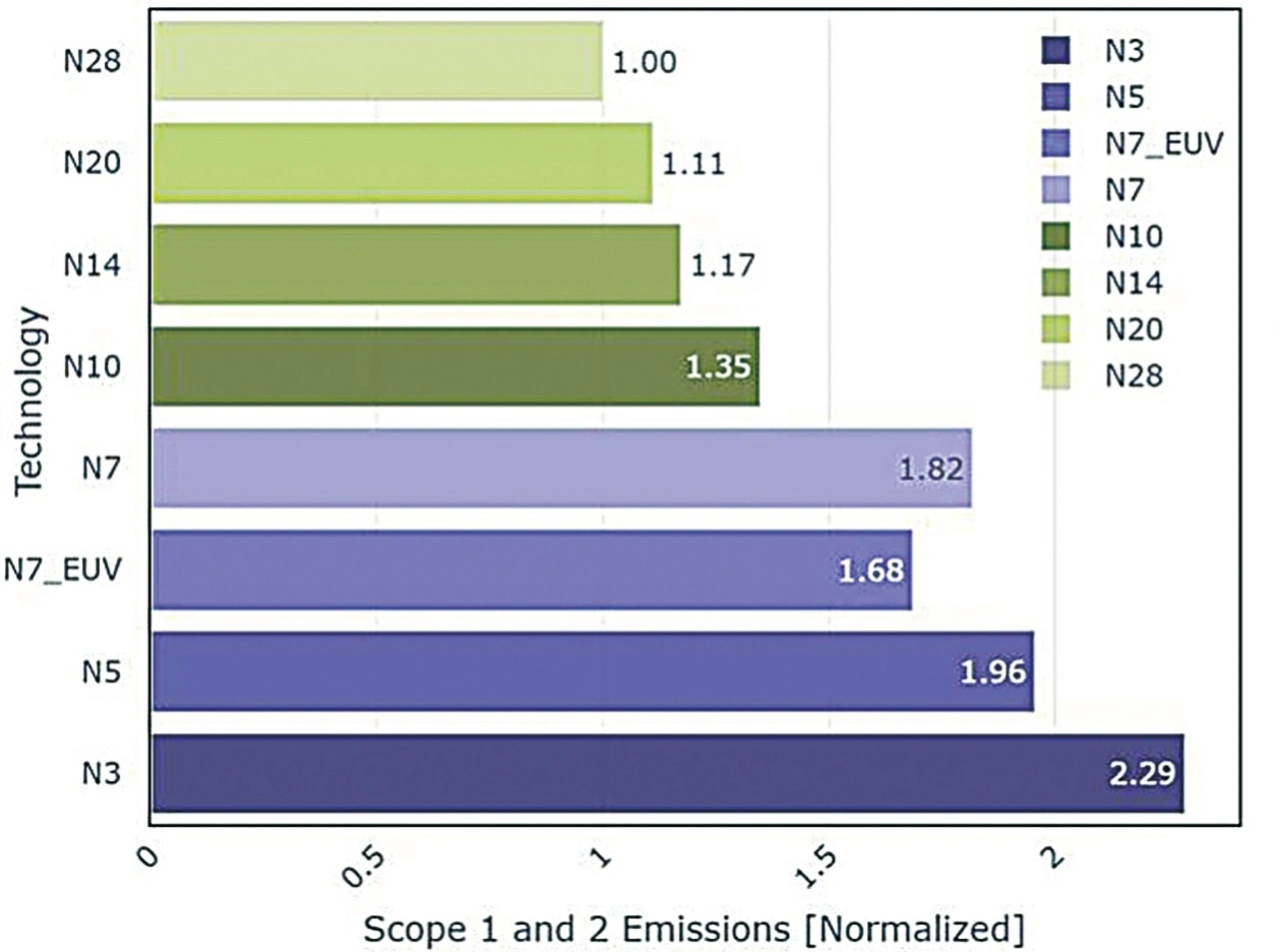

Auf der »Advanced Lithography + Patterning Conference« Ende Februar konnte das Imec Ergebnisse seines SSTS-Programms präsentieren und zum ersten Mal die Umweltauswirkungen von Prozessschritten zur Strukturierung in verschiedenen Logikprozesstechnologien quantifizieren. »Mithilfe unseres virtuellen Fab-Tools konnten wir zeigen, dass Lithografie und Ätzen zusammen für 45 Prozent der Emissionen in den Bereichen 1 und 2 bei der Produktion eines 3-nm-Logikwafers verantwortlich sind«, erklärt Emily Gallagher, Principal Member of Technical Staff bei Imec. »Darüber hinaus kann das Modellierungs-Tool die mit echten Fab-Experimenten verbundenen Gewinne quantifizieren. Beispielsweise spart eine Senkung der EUV-Dosis um zehn Prozent etwa 0,4 kg CO2eq pro Wafer. Dies würde in einer großen Fabrik zu einer Einsparung von etwa 40 Tonnen CO2eq pro Monat führen, was den Emissionen von 100 Hin- und Rückflügen von San Francisco, CA, nach Portland, Oregon, entspricht.«

Gallagher erklärt außerdem, dass das Imec in Zusammenarbeit mit seinem Partner Edwards kürzlich ein Wasserstoffrückgewinnungssystem für die EUV-Lithografie im 300-mm-Reinraum vom Imec installiert hat, mit dem das Forschungszentrum etwa 70 Prozent des Wasserstoffs wiederverwenden und zurückgewinnen kann. Gallagher weiter: »Darüber hinaus konzentrieren wir uns verstärkt auf Lösungen mit niedriger Dosis für die 0,33NA- und 0,55NA(High-NA)-EUV-Lithografie, was bekanntermaßen auch die Kosten für die Lithografie senkt. Wir haben auch Richtungen für eine verbesserte Nachhaltigkeit beim Ätzen identifiziert, wobei wir uns derzeit auf die allgemeine Reduzierung des konventionellen Gasverbrauchs konzentrieren. In einem nächsten Schritt werden wir zusammen mit unseren Partnern die Auswirkungen dieser vorgeschlagenen Lösungen auf den gesamten Ablauf des Halbleiterprozesses quantifizieren.«

- Das SSTS-Programm des Imec

- Softwareplattform als virtuelle Fab