IC-Entwicklung

Effizientere Simulation mit KI-basierter Modellfehlerschätzung

Um den Rechenaufwand für die Schaltungssimulation zu senken, werden oft vereinfachte Modelle genutzt. Doch die Ergebnisse der Simulation können in bestimmten Fällen fehlerhaft sein. Dann empfiehlt es sich, die genaueren, rechenintensiven Modelle zu nutzen. Eine Aufgabe für künstliche Intelligenz.

Im Gegensatz zum Zusammenlöten von Schaltungen mit einzelnen Bauteilen hat der Entwurf von integrierten Schaltungen einen Nachteil: Einmal gefertigt, hat der Entwickler so gut wie keine Möglichkeit mehr, die Schaltung zu verändern und Fehler zu beheben. Können einzelne Bauteile auf einer Leiterplatte wenigstens mit etwas Mühe noch ausgetauscht werden, so werden integrierte Schaltkreise in sehr teuren Prozessen monolithisch auf Wafern gefertigt. Ohne die Möglichkeit eines Try-and-Error-Ansatzes gilt für den Entwurf integrierter Schaltungen das Gleiche wie für den Bau einer Brücke. Hier müssen Statiker bereits vor dem Bau die Stabilität und Sicherheit mithilfe von Simulationen belegen. Genauso ist es unabdingbar, beim Entwurf von integrierten Schaltungen deren Funktionsfähigkeit bereits vor der Fertigung in Hardwaresimulationen zu überprüfen.

Seit den 70er- und 80er-Jahren sind Hardwaresimulationen ein fester Bestandteil der Electronic Design Automation (EDA) und haben sich seitdem stetig weiterentwickelt. Insbesondere gibt es unterschiedliche Ansätze, Schaltungen zu simulieren. Der klassische Ansatz, für jeden einzelnen Transistor physikalisch abgeleitete Modelle zu verwenden, kann fast schon als Goldstandard der Branche bezeichnet werden. Die Ergebnisse stimmen in der Regel gut mit den Messwerten der realen Schaltung überein.

Dieser Ansatz hat jedoch einen Nachteil: Es ist sehr rechenaufwendig, die Gleichungen der Simulation numerisch auf Transistorebene zu lösen. Moderne Prozessoren haben mehrere Milliarden Transistoren, sodass es so gut wie unmöglich ist, solche Simulationen für den gesamten IC durchzuführen. Aber auch die kleineren anwendungsspezifischen integrierten Schaltungen (Application-Specific Integrated Circuits, ASICs), die zum Beispiel in Autos, Kühlschränken oder Sensoren verbaut werden, sind komplex genug, dass Simulationen auf Transistorebene mehrere Stunden oder sogar Tage dauern. Gleichzeitig werden jedoch im Entwurfsprozess viele Simulationen benötigt, um die Funktionsweise der Schaltung unter vielen Bedingungen und mit unterschiedlichen Eingaben zu testen.

Jobangebote+ passend zum Thema

Vereinfachung durch Abstraktion

Um dieses Problem zu lösen, wird ein anderer Ansatz zur Simulation von Schaltungen verwendet: Das Verhalten wird nur abstrakt betrachtet. Im zuvor erwähnten Beispiel einer Simulation der Brückenstatik können Vereinfachungen vorgenommen werden. Der Einfluss des Windes auf die Brücke ist zwar wichtig, doch um ihre prinzipielle Tragfähigkeit zu überprüfen, kann zunächst auf komplexe Strömungsmodelle verzichtet werden. Dies macht die Berechnungen einfacher und hilft, den Entwurfsprozess zu beschleunigen.

Im Bereich der EDA sind Simulationen des abstrakten Schaltungsverhaltens essenziell. Die eingesparte Rechenzeit wird im Entwurfsprozess in der Regel dafür genutzt, mehr Tests zu simulieren, frei nach der wichtigen Devise: »Test Early, Test Often«. Der Grad an Abstraktion hat aber seinen Preis: Einfache Modelle der Brücke können solide Daten liefern. Ignoriert der Ingenieur den Wind jedoch komplett, kann es so kommen wie mit der Tacoma-Narrows-Brücke im US-Bundesstaat Washington, die 1940 spektakulär zusammenbrach.

Die Kenntnis des Modellfehlers als wichtige Information

Bei der Simulation von integrierten Schaltungen ist es also unabdingbar, Verhaltensmodelle zu nutzen. Der IC-Entwickler muss aber immer ein Auge auf die Modellfehler haben und wissen, dass unter bestimmten Bedingungen das Modell versagen kann. Nur wie ist es möglich, die Modellfehler im Blick zu behalten, ohne ständig rechenaufwendige Simulationen auf der Transistorebene durchzuführen?

Im Projekt KI-EDA hat das IMMS Institut für Mikroelektronik- und Mechatronik-Systeme eine Methode entwickelt, mit der dieser Modellfehler während der Simulation abgeschätzt werden kann. Ein neuronales Netzwerk wurde da- rauf trainiert, den Modellfehler eines Verhaltensmodells einer Schaltung in Abhängigkeit der Eingaben und Ausgaben des Modells zu schätzen. Ist der Modellfehler bekannt, können zum Beispiel einfache Verhaltensmodelle genutzt werden, wann immer die Bedingungen es zulassen und der Modellfehler niedrig ist.

Aufwendigere Simulationen auf Transistorebene werden dann eingesetzt, wenn es auch wirklich nötig ist. Alternativ kann die Information zum Modellfehler auch verwendet werden, um die Belastbarkeit des Simulationsergebnisses abzuschätzen.

| KI-EDA |

|---|

| Das Forschungsprojekt KI-EDA (Baukastensystem mit künstlicher Intelligenz für das beschleunigte Entwickeln von Spezialchips für die Industrie 4.0) mit einem Volumen von 3,63 Mio. Euro wurde vom Bundesministerium für Bildung und Forschung (BMBF) gefördert. Im Rahmen der Maßnahme »Mikroelektronik für Industrie 4.0 (ElektroniK I4.0)« unter der Verbundnummer es2eli4001 unterstützte das BMBF die Arbeiten mit 1,95 Mio. Euro. Die Arbeit des IMMS Institut für Mikroelektronik- und Mechatronik-Systeme wurde unter dem Kennzeichen 16ME0010 gefördert. Als zweiter Projektpartner hat sich Centitech (FRABA Gruppe) aus Aachen am Forschungsprojekt KI-EDA beteiligt, Verbundkoordinator war iC-Haus aus Bodenheim |

Modellfehler schätzen – eine neue EDA-Methode

In der Praxis werden integrierte Schaltungen in Blöcke unterteilt, die jeweils bestimmte Funktionen übernehmen. Diese IP-Blöcke (Intellectual Property) genannten Module können einzeln oder im Zusammenspiel als kompletter IC simuliert werden. Der Grundgedanke der Fehlerschätzung besteht darin, einem IP-Block für die Simulation ein vortrainiertes neuronales Netz in einem eigenen Block hinzuzufügen. Dieser beeinflusst die Schaltung in keiner Weise, kann die Ein- und Ausgänge des IP-Blocks mitlesen und nutzt diese als eigene Eingangsgrößen für die Schätzung. Der Vorteil dieses Ansatzes ist, dass der Fehler während der Simulation mitgeschätzt werden kann und nicht erst im Nachhinein berechnet werden muss. Alle gängigen Hardwaresimulatoren sind in der Lage, diese neuronalen Netze zu berechnen, solange sie in einer entsprechenden Programmiersprache vorliegen.

➔ Die Methode erfordert drei Arbeitsschritte:

➔ die Datengenerierung,

➔ das Training sowie

➔ die Einrichtung und die eigentliche Simulation.

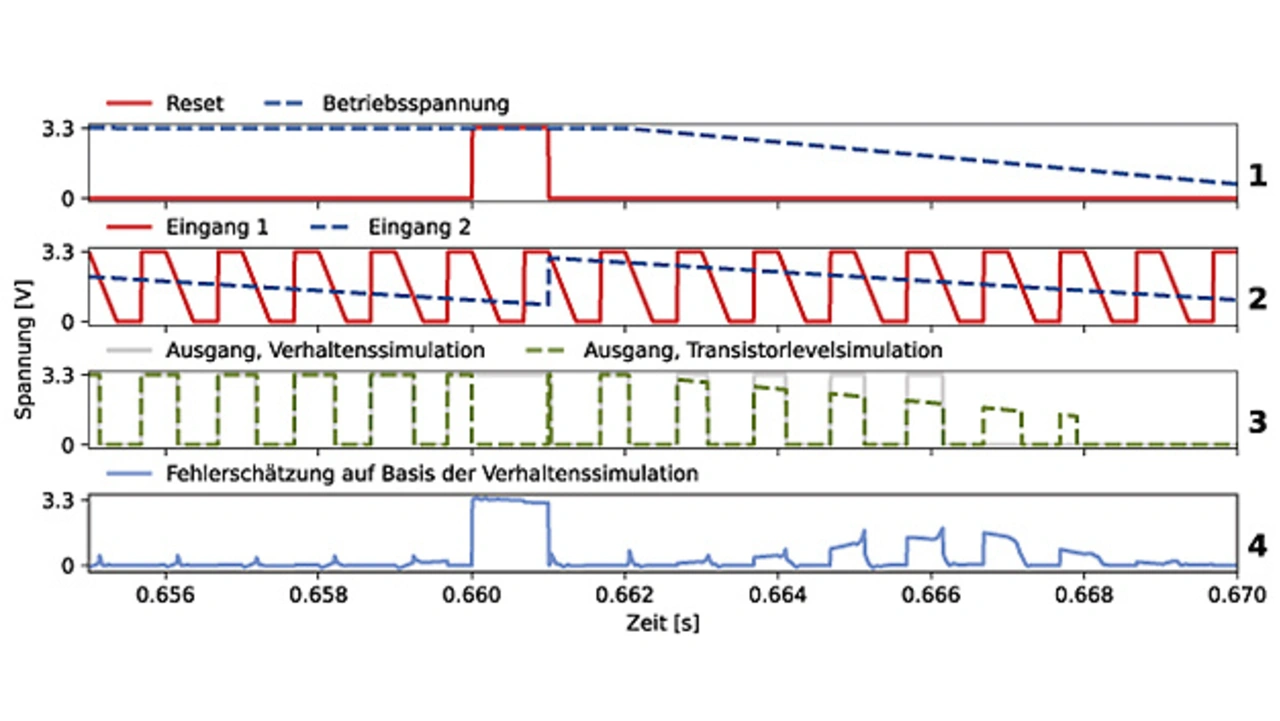

Im Folgenden werden diese Schritte anhand eines Komparators als einfacher Beispielschaltung erläutert. Dieser Komparator hat zwei Haupteingänge und vergleicht die dort anliegenden Spannungen miteinander. Je nachdem, welche Spannung größer ist, schaltet der Komparator seinen einzigen Ausgang auf high oder low. Zudem hat dieser Komparator Anschlüsse für ein Reset-Signal und die Betriebsspannung, in der Summe also fünf Ein- und Ausgänge.

Datengenerierung

Als lernendes Element wurde ein mehrlagiges Perzeptron (MLP) gewählt. Das ist eine spezielle Art von künstlichen neuronalen Netzen, die einen Eingabevektor in einen Ausgabevektor umwandeln und dabei eine beliebige Anzahl an Neuronen in Zwischenschichten haben können. Während des Trainings werden vor allem die Gewichte der neuronalen Ein- und Ausgänge der Zwischenschichten verändert, sodass spezifische Eingangswerte des Perzeptrons mit Ausgangswerten assoziiert werden. Es handelt sich somit um eine Regression.

Um das MLP zu trainieren, werden Simulationsdaten des Verhaltensmodells einer Schaltung sowie Daten einer Simulation auf Transistorebene benötigt. Werden für die beiden Simulationen übereinstimmende Eingangsdaten gewählt, kann die Differenz der Simulationsergebnisse als Maß des Modellfehlers verwendet werden.

Wie bei einer Regression üblich, ist das trainierte MLP in der Lage, Zwischenwerte mit genügender Genauigkeit zu interpolieren. Eine Extrapolation, also eine Abschätzung außerhalb des gelernten Wertebereichs, muss mit Vorsicht betrachtet werden. Daher empfiehlt es sich, möglichst viele und unterschiedliche Systemzustände der Schaltung in die Simulationsdaten zu integrieren.

Im Beispiel des Komparators empfiehlt es sich also, nicht nur verschiedene Spannungen an den Haupteingängen anzulegen, sondern dabei auch die Betriebsspannung zu variieren und den Reset des Komparators auszulösen. Auf diese Weise kann das MLP das Verhalten der Schaltung auch in ungewöhnlichen Situationen kennenlernen, was insbesondere für die Abschätzung von Modellfehlern von Vorteil ist. Der Datensatz sollte den möglichen Eingaberaum gut repräsentieren, muss ihn aber nicht vollkommen abdecken.

Training

Mithilfe der Simulationsdaten wird das MLP trainiert. Dies geschieht zweckmäßigerweise in einer allgemeinen Programmiersprache wie Python. Zum einen sind Hardware-Beschreibungssprachen und Simulatoren zwar in der Lage, neuronale Netzwerke zu berechnen. Für das iterative Training fehlen ihnen jedoch entsprechende Funktionen. Zum anderen stehen für allgemeine Programmiersprachen einfach zu nutzende Werkzeuge und Erweiterungen wie Scikit-learn zur Verfügung, die für das Training von MLPs optimiert sind.

Das in Python programmierte und trainierte MLP muss jedoch in eine Hardware-Beschreibungssprache übertragen werden, damit es in eine Schaltung integriert werden kann. Hierfür kann zum Beispiel ein Werkzeug wie Mako verwendet werden, das aus Vorlagen und entsprechenden Parametern entsprechenden Programmcode erzeugen kann. Das trainierte MLP liegt nun als fixierter Block vor und kann in eine Schaltung integriert und simuliert werden. Das MLP wird für jede Schaltung neu trainiert und kann nicht mit ihm unbekannten IP-Blöcken kombiniert werden.

Einrichtung und Simulation

Das neuronale Netz wird so in die Schaltung integriert, dass es die Ein- und Ausgänge des IP-Blocks mitlesen kann, das Verhalten des Schaltkreises jedoch nicht beeinträchtigt. Das auf den Beispielkomparator trainierte MLP benutzt also die Signale der beiden Haupteingänge des Komparators, dessen Betriebsspannung und das Reset-Signal sowie dessen Ausgang als eigene Eingänge. Daraus schätzt es den Modellfehler, der nicht in die Schaltung zurückgeführt wird (Bild). Mit diesem Aufbau können nun reguläre Tests entsprechend des geplanten Entwicklungsprozesses der integrierten Schaltung durchgeführt werden.

Modellfehler als Messwert

Es gibt mehrere Möglichkeiten, wie der abgeschätzte Modellfehler genutzt werden kann. Zum einen kann er als Ersatz für ein Konfidenzintervall der Ausgangswerte des simulierten IP-Blocks dienen. Zum anderen kann er als Abbruchkriterium der Simulation verwendet werden. Erreicht der Modellfehler im Vorfeld definierte kritische Werte, kann die Simulation abgebrochen und mit geänderten Parametern neu gestartet werden. Dies ist insbesondere bei längeren Simulationen nützlich, bei denen ein Ergebnis sonst erst nach mehreren Stunden oder Tagen vorliegt und das Versagen des Verhaltensmodells der Schaltung analysiert werden kann.

Um die Effektivität der Hardwaresimulation zu steigern, kann der Modellfehler als Messwert genutzt werden, anhand dessen dynamisch unterschiedliche Modelle für die Simulation verwendet werden. Dabei wird die Simulation mit dem schnell zu berechnenden Verhaltensmodell gestartet. Erreicht der Fehler dieses Modells ein kritisches Limit, wird die Simulation abgebrochen und automatisch mit den Zwischenwerten an dieser Stelle neu gestartet. Die neue Simulation kann entsprechend des Modellfehlers angepasst werden. So lässt sich beispielsweise die Schrittweite der Solver des Simulators verändern, um eine höhere Genauigkeit zu erreichen, oder der Block auf Transistorebene simulieren.

Aufwand und Nutzen von KI-gestützter Fehlerschätzung

Die verwendeten neuronalen Netze sind im Vergleich zu anderen KI-Verfahren sehr klein. Der im Beispiel verwendete Fehlerschätzer des Komparators hat insgesamt 45 Neuronen in zwei Schichten, kein Vergleich zu den ca. 80-100 Milliarden Neuronen von ChatGPT. Daher ist der Rechenaufwand, um zusätzlich zum Verhaltensmodell auch noch den Fehlerschätzer zu berechnen, überschaubar.

Im nichtoptimierten Beispiel des Komparators beträgt der zusätzliche Rechenaufwand des Fehlerschätzers im Vergleich zum Verhaltensmodell 75 %. Dem steht jedoch auch ein zusätzlicher Rechenaufwand von 350 % für die Simulation auf Transistorebene gegenüber. Die Fehlerschätzung gibt es also nicht umsonst, aber das Verhaltensmodell samt Fehlerschätzer lässt sich immer noch deutlich schneller berechnen als die Simulation auf Transistorebene.

Da diese Methode geeignet ist, den Fehler und damit auch das Verhalten der Schaltung abzuschätzen, stellt sich natürlich die Frage, warum das neuronale Netzwerk in der Simulation nicht gleich das gesamte Verhaltensmodell der Schaltung ersetzten kann. Dem steht vor allem ein grundlegendes Problem neuronaler Netze gegenüber: Nachvollziehbarkeit.

Neuronale Netze verhalten sich in Simulationen wie eine Blackbox, sodass für Menschen kausale Zusammenhänge zwischen Eingabe und Ausgabe nur schwer nachzuvollziehen sind. Im zuvor verwendeten Beispiel mit der Brücke könnte man die Statik der Brücke mithilfe eines neuronalen Netzwerks si- mulieren. Bricht die Brücke in der Simulation jedoch in sich zusammen, wird es schwer, den genauen Grund dafür zu ermitteln und anschließend Verbesserungen des Entwurfs abzuleiten.

Zudem schafft die Nachvollziehbarkeit der Verhaltensmodelle auch Vertrauen. Im Gegensatz zu trainierten neuronalen Netzen lassen sich klassische Gleichungen leichter dokumentieren, verstehen und weitergeben. Daher ist es insbesondere in Zertifizierungsverfahren von Vorteil, dass Simulationsdaten auf konventionellen Verhaltensmodellen beruhen und nur der Modellfehler durch ein neuronales Modell abgeschätzt wird.

Einsatz in der Praxis

Die beschriebene Methode ist in der Lage, auch mit dynamischen Systemen umzugehen, indem beim Training des Modellfehlers nicht nur aktuelle Ein- und Ausgänge, sondern ein Zeitfenster betrachtet wird. Aber es gibt besondere Schaltungen, die mit dieser Methode nicht kompatibel sind: Ist das Verhalten der Schaltung nicht nur vom zeitlichen Verlauf seiner Eingänge, sondern auch von variablen intrinsischen Zuständen abhängig, kann das MLP den Modellfehler nicht korrekt schätzen.

Zudem wird mit der Methode derzeit ein eigenes MLP pro Ausgang des IP-Blocks benötigt. Dies liegt darin begründet, dass das verwendete Werkzeug scikit-learn nur MLPs mit einem Ausgang unterstützt. Das kann jedoch durch die Wahl anderer Netzwerke oder Trainingswerkzeuge gelöst werden.

Nachdem die neu entwickelte Methode ihre generelle Tauglichkeit belegt hat, wird sie am IMMS im Bereich des ASIC-Entwurfs im industriellen Rahmen getestet, um weitere Erfahrungen damit zu sammeln und sie weiterzuentwickeln.

Literatur

[1] Siemen, H.; Grabmann M. und Gläser, G.: Learn from error! ML-based model error estimation for design verification without false-positives. 18th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2022, Konfe- renzband, S. 1-4, DOI: 10.1109/SMACD 55068.2022.9816317.

[2] KI-EDA. IMMS Institut für Mikroelektronik- und Mechatronik-Systeme, Website, https://www.imms.de/referenzen/projekte/d/ki-eda-4075.html.

Der Autor

Henning Siemen

studierte Biosystemtechnik an der Universität Magdeburg und forscht als wissenschaftlicher Mitarbeiter seit 2020 am IMMS. Seine Spezialgebiete sind vor allem mathematische Modellierung und Simulationen. Am IMMS entwickelt er neue Methoden zur KI-basierten Entwurfs- automatisierung und Verifikation.

henning.siemen@imms.de