Smart Mobility / Systemdesign

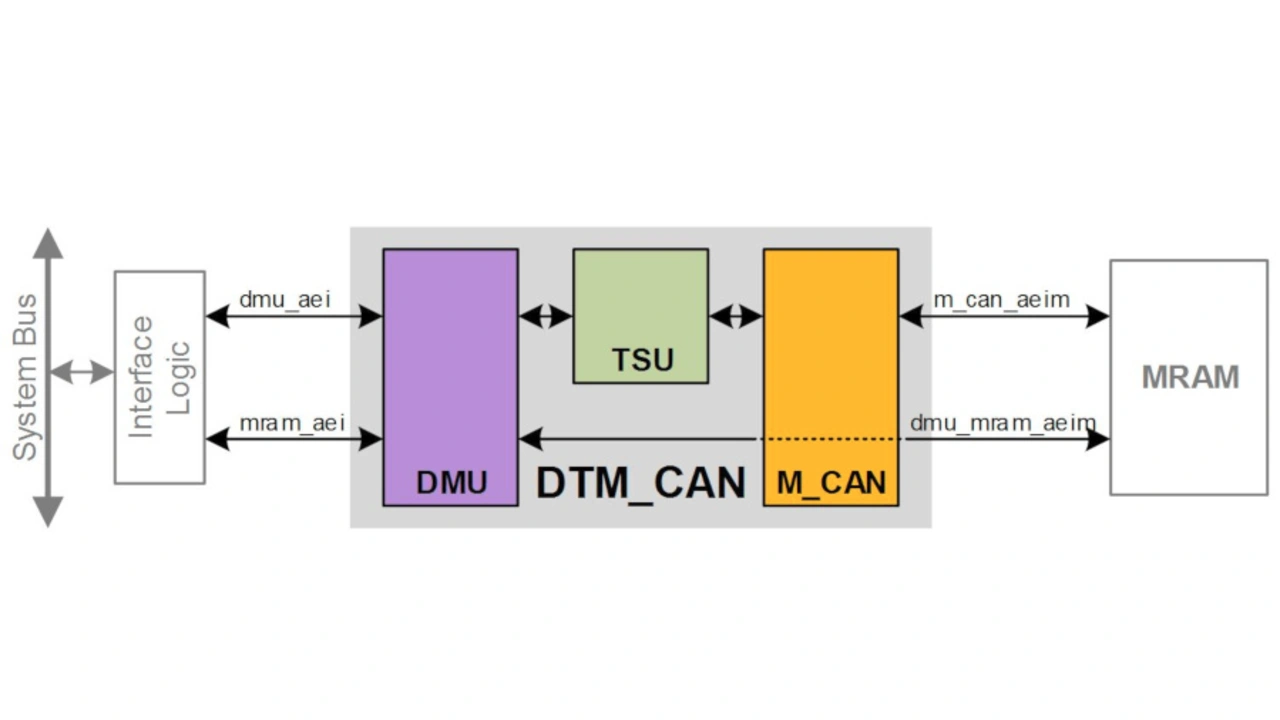

Erweiterung der M_CAN-Controller-IP

Fortsetzung des Artikels von Teil 2

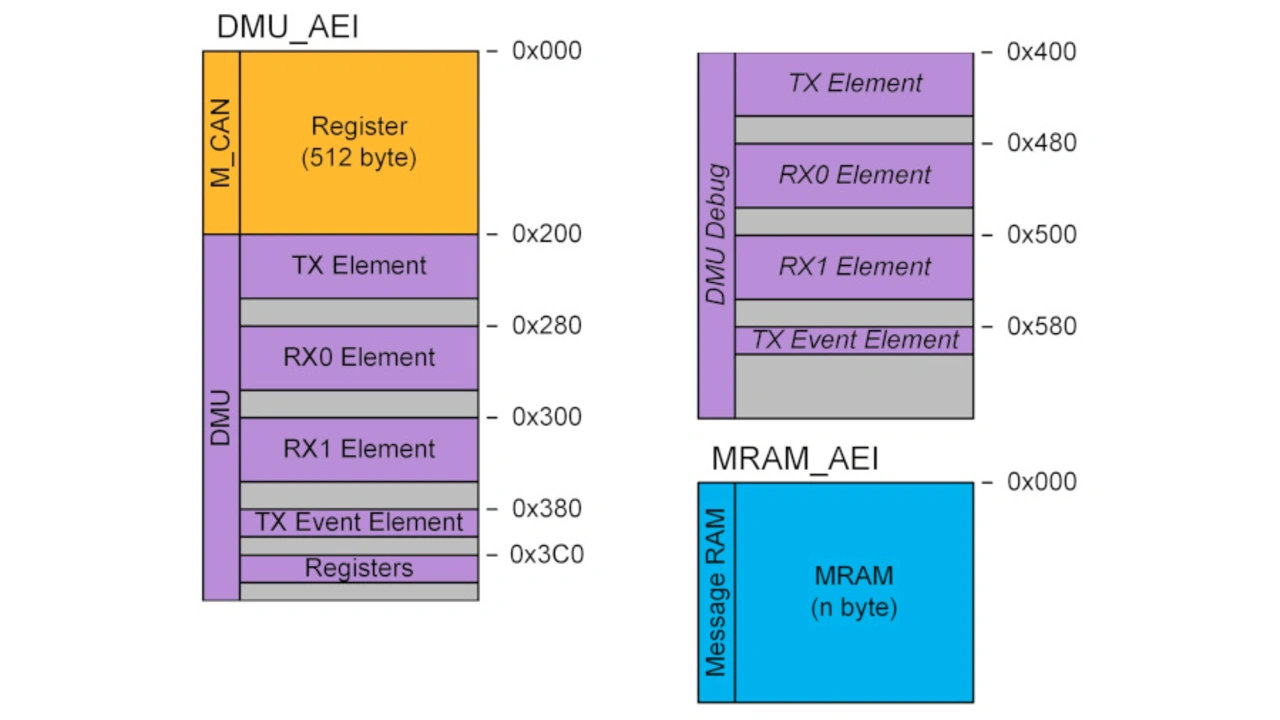

Elemente zur Übertragung

TX-Element

Hier werden die CAN-Botschaftselemente vom DMA-Controller geschrieben, die dem TX-FIFO/queue hinzuzufügen sind. Beim Schreiben des letzten Element-Wortes wird dafür automatisch der TX-Request gesetzt, sodass der M_CAN dieses versendet. Die DMU fordert vom DMA-Controller weitere CAN-Elemente an, solange der TX-FIFO/queue noch nicht gefüllt ist.

RX0/RX1-Elemente

Hier werden die CAN-Botschaftselemente gelesen, die in den Empfangs FIFO 0 bzw. 1 des M_CAN liegen. Mit Lesen des letzten Element-Wortes, teilt die DMU dem M_CAN das erfolgte dequeuing - durch Setzen des zugehörigen acknowledge-Index - mit. Optional kann der Zeitstempel der TSU mitübertragen werden. Die DMU weist den DMA zum Abtransport weiterer CAN-Elemente an, solange der RX-FIFO noch nicht leer ist.

TX-Event-Element

Der Ablauf ist analog zu den RX0/RX1-Elementen, jedoch werden hier die TX-events gelesen, optional mit dem Zeitstempel der TSU.

Jobangebote+ passend zum Thema

DMU-Register

Die DMU erhält die meisten Konfigurationsinformationen aus dem M_CAN, lediglich das Übertragen des HW-Timestamp der TSU kann hier ein- und ausgeschaltet werden. Eine Vielzahl von Statusinformationen geben Feedback darüber, ob die Zugriffe auf die virtuellen Elemente korrekt waren oder etwaiige Probleme auftraten. Dies ist insbesondere beim Debugging der DMA-Routinen hilfreich, sollte aber aus Gründen der funktionalen Sicherheit auch im regulären Betrieb überwacht bleiben.

DMU-debug-section

Zum Debuggen der Software kann hier lesend auf die DMU-Elemente zugegriffen werden. Beim TX-Element wird das zuletzt geschriebene Element gelesen, bei den RX0-, RX1-, TXE-Elementen wird das aktuelle Element gelesen. Diese Zugriffe lösen keine automatischen Abläufe der DMU aus, wie das z.B. das zugehörige Quittieren im M_CAN.

Datenfluss im SoC

Für den Datenfluss innerhalb des SoCs ist folgendes Verfahren empfehlenswert: Es ist ein RAM auszuwählen, auf das der gewünschte CPU-Kern einen möglichst performanten Schreib- und Lesezugriff hat. Der DMA muss ebenfalls einen direkten Zugriff auf dieses RAM haben. Dieses CRAM dient dann zum Austausch der CAN-Botschaften: der DMA-Controller übernimmt die langsamen Transfers der CAN-Botschaften über weite NoC-Teile hinweg. Die Botschaften werden im CRAM möglichst nahe zum CPU-Kern abgelegt, sodass dieser einen nahezu ungebremsten Zugriff darauf hat.

- Erweiterung der M_CAN-Controller-IP

- DMU-Erweiterung

- Elemente zur Übertragung

- Zeitmarke und Synchronisierung

- Fazit und Glossar