Smart Mobility / Systemdesign

Erweiterung der M_CAN-Controller-IP

Zur Unterstützung moderner CAN-Netzwerke hat Bosch den Funktionsumfang des M_CAN mit zwei Hardware-Erweiterungen vergrößert. Das DMU-Erweiterungsmodul entlastet die CPU, indem der Transport von CAN-Botschaften an einen DMA ausgelagert werden kann.

Das TSU-Erweiterungsmodul schafft eine hardware-basierte und AUTOSAR-kompatible Zeitsynchronisation in optimaler Präzision.

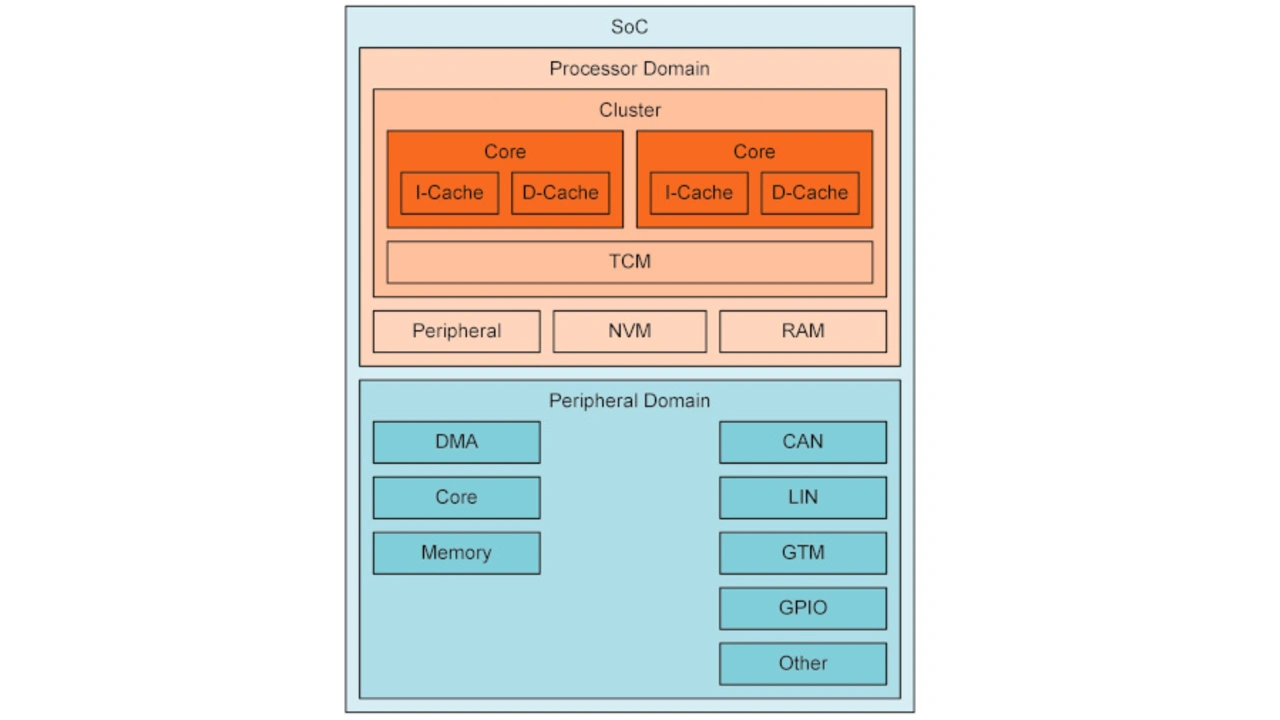

Beim Austausch von CAN-Botschaften zwischen einem CPU-Kern und dem M_CAN sind, insbesondere bei komplexen SoCs, einige Fallstricke zu berücksichtigen: diese werden im Folgenden genauer betrachtet. Bedingt durch die hohe Komplexität moderner SoC-Architekturen, werden die on-chip-Kommunikationspfade in mehrere Domänen unterschiedlicher Performanz unterteilt (Bild 1).

Jobangebote+ passend zum Thema

Die Darstellung zeigt die potenzielle Geschwindigkeit einer Datenübertragung farblich kodiert (rot: schnell; blau: langsam). Darin stellt die Anbindung der CPU-Kerne an die dedizierten Caches die schnellste Domäne, gefolgt von dem TCM innerhalb des Clusters. In der Software-Erstellung ist darauf zu achten, dass diese Speicherdomänen effizient genutzt werden können. Im extremen Gegensatz hierzu stehen die Zugriffe von CPU-Kernen innerhalb der processor domain auf Komponenten der peripheral domain: diese können insbesondere bei Einzelzugriffen um den Faktor 30 langsamer ausfallen.

Ein Beispiel stellt der kontinuierliche Austausch von CAN-Botschaften zwischen CPU-Kern und einem M_CAN. Typischerweise erfordert das folgende Interaktionen:

- bei interrupt durch den M_CAN ist dessen Statusregister zu prüfen,

- gegebenenfalls werden die CAN-Botschaften übertragen,

- gegebenenfalls die Rückmeldung über erfolgreichen Austausch einer Botschaft mit dem M_CAN.

Führten diese Interaktionen in der processor domain die CPU-Kerne aus, so würden diese durch das NoC maßgeblich ausgebremst. Falls vorhanden, können solche Interaktionen auch teilweise über einen CPU-Kern innerhalb der peripheral domain erledigt werden. Dieser Artikel fokussiert jedoch auf einen anderen Lösungsansatz, der keine Rechenressourcen eines CPU-Kerns allokiert.

- Erweiterung der M_CAN-Controller-IP

- DMU-Erweiterung

- Elemente zur Übertragung

- Zeitmarke und Synchronisierung

- Fazit und Glossar