Smart Mobility / Systemdesign

Erweiterung der M_CAN-Controller-IP

Fortsetzung des Artikels von Teil 1

DMU-Erweiterung

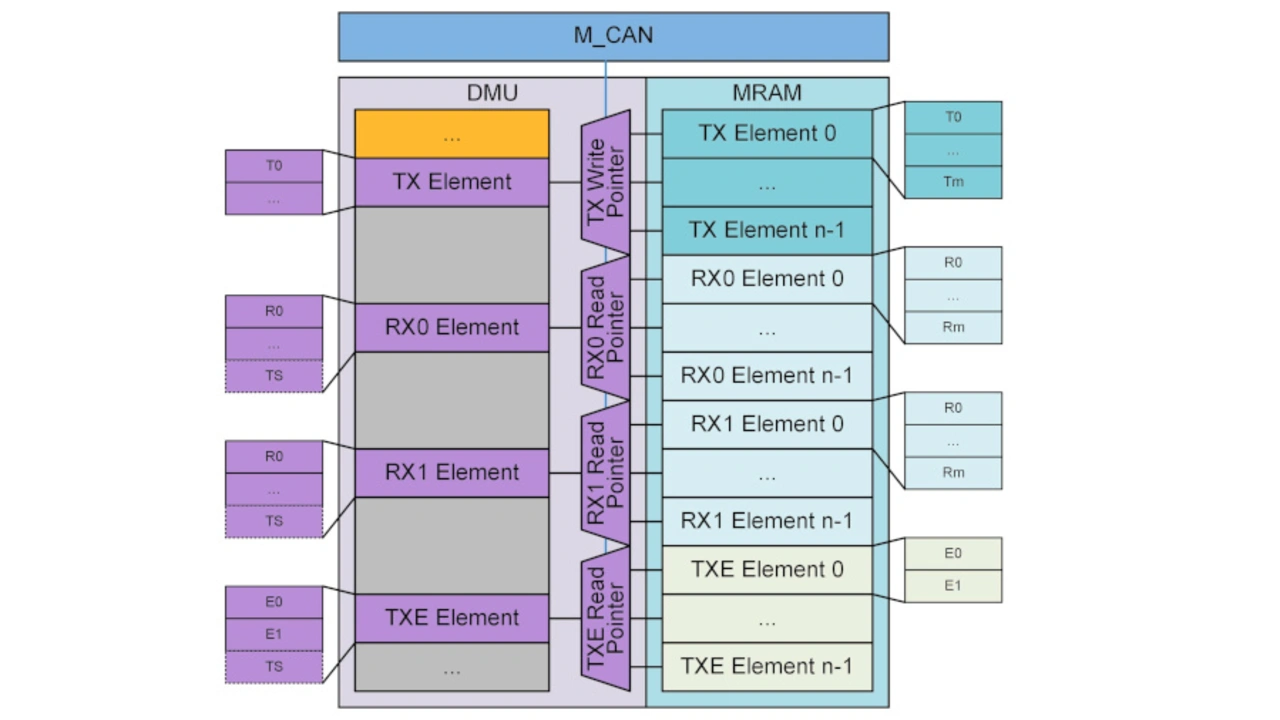

Bosch hat eine sogenannte DMU-Erweiterung für den M_CAN vorgestellt. Damit kann der kontinuierliche Austausch von CAN-Botschaften teilweise oder komplett auf einen DMA-Controller ausgelagert werden. Die Erweiterung basiert auf dem Konzept der Virtualisierung der FIFO-head-Elemente (Bild 2). Der M_CAN hat ein zugeordnetes message-RAM (MRAM), welches u.a. die in FIFOs organisierten CAN-Botschaften enthält (Bild 2, rechts).

Jobangebote+ passend zum Thema

Greift die CPU auf das Speichersegment der aktuellen Botschaft (head element) innerhalb dieser FIFOs zu, so sind bisher zunächst die jeweiligen Zeiger (read/write-pointer) aus dem M_CAN abzufragen. Um dies zu vermeiden, werden die Zugriffe auf feste Adressbereiche virtualisiert. Die DMU leitet diese Zugriffe dynamisch auf die head-Elemente im MRAM um. Innerhalb der DMU steuern die FIFO-Zeiger im M_CAN diese Umleitung somit unsichtbar. Die Ausmaße der reservierten Bereiche entsprechen den jeweils größtmöglichen Nachrichtenelementen, dies sind 18 Wörter für die TX-, RX0- und RX1-Elemente und zwei Wörter für das TX-event-Element (drei Wörter, wenn die Zeitstempel der TSU mitübertragen werden soll).

Der Transfer eines letzten Element-Wortes aktiviert in der DMU einen Prozess, bei dem für TX-Elemente das transmit request - bzw. für die anderen Elemente (RX0, RX1, TXE) das zugehörige FIFO-acknowledge - im M_CAN gesetzt wird. Somit ist allein durch das Schreiben/Lesen der CAN-Botschaften in den DMU-Elementen der enqueueing/dequeueing-Vorgang im M_CAN vollständig und abgeschlossen. Die DMU unterstützt den Botschaften-Transfer vom CRAM zu der TX-FIFO/queue und umgekehrt von den RX-FIFOs / TX-event-FIFO zum CRAM.

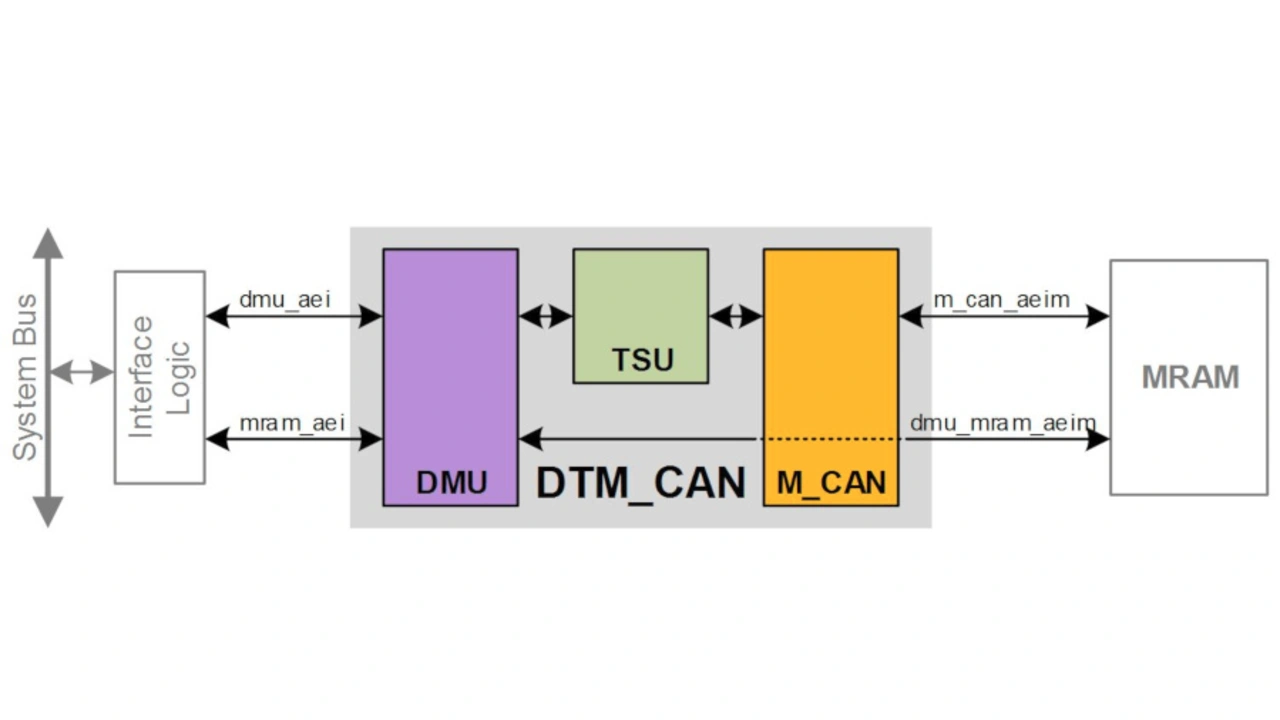

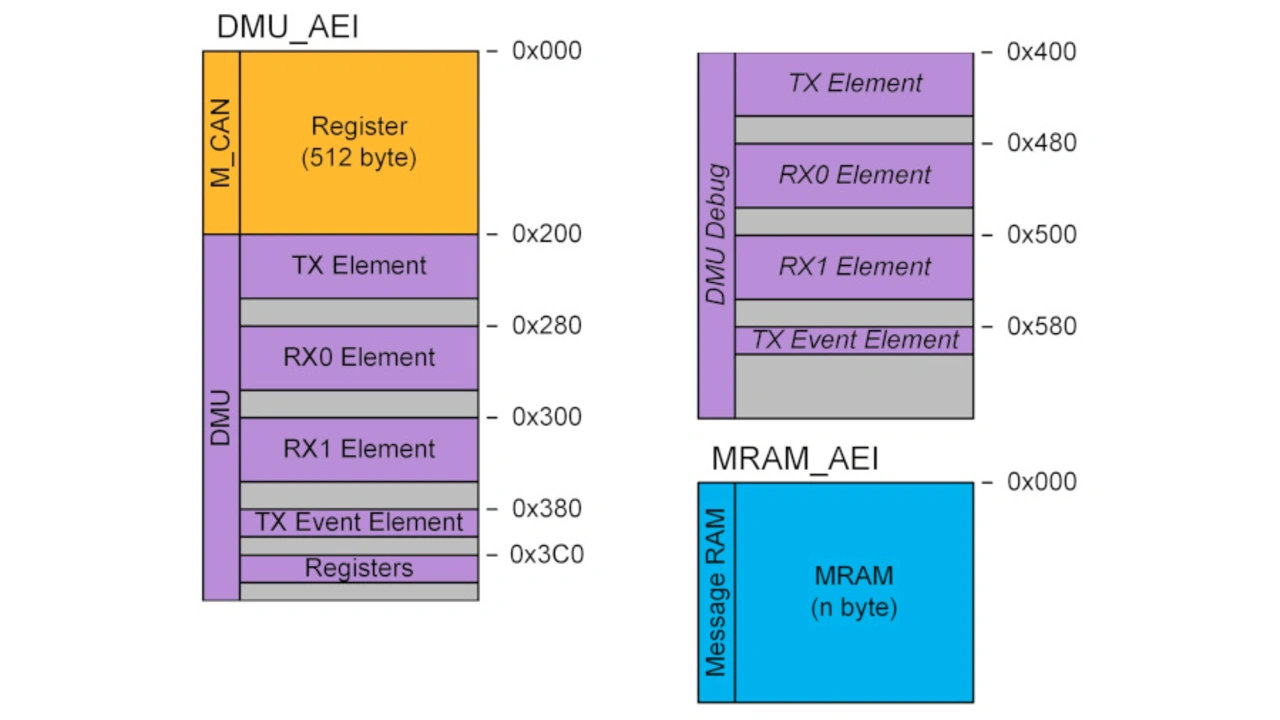

Das Blockdiagramm Bild 3 zeigt den M_CAN mit den DMU- und TSU-Erweiterungen: die Zugriffe der CPU auf den M_CAN werden durch beide Erweiterungsmodule hindurch geleitet. Bild 4 zeigt die gesamte Speicheraufteilung der DMU. Im gelb markierten Speicherbereich ab Adresse 0 sind die Register des M_CAN und der TSU gezeigt. Darauf folgen (lila eingefärbt) die virtuellen Speicherbereiche der aktuellen CAN-Elemente, die der DMA verwaltet.

- Erweiterung der M_CAN-Controller-IP

- DMU-Erweiterung

- Elemente zur Übertragung

- Zeitmarke und Synchronisierung

- Fazit und Glossar