Forschungserfolg bei Siliziumkarbid

AIST entwickelt monolithisch integriertes SiC-Leistungs-IC

Leistungs-MOSFETs haben eine vertikale Struktur, Treiberschaltungen jedoch eine laterale. Daher war es bisher nicht üblich, beides monolithisch zu integrieren. Allerdings könnte dies Hochleistungswandler mit Siliziumkarbid noch besser machen. Japanische Forscher des AIST melden nun einen Erfolg.

Monolithische SiC-Leistungs-ICs können dazu beitragen, die Größe und das Gewicht von Umrichtern zu verringern und die Verluste zu reduzieren. Allerdings es ist schwierig, CMOS-Schaltkreise in Siliziumkarbid (SiC) zu realisieren, die ausreichend hohe Ausgangsströme liefern, um einen Leistungs-MOSFETs zu schalten, und gleichzeitig diese empfindlichen Schaltungsteile vor den hohen Spannungen im MOSFET zu schützen.

Im Rahmen eines Projektes haben Forschende am Advanced Power Electronics Research Centre des japanischen National Institute of Advanced Industrial Science and Technology (AIST) eine Bauelementestruktur entwickelt, die diese Herausforderungen lösen soll. Auf dieser Grundlage bauten sie ein monolithisches SiC-Leistungs-IC, das aus einem vertikalen Leistungs-MOSFET mit einer Spannungsfestigkeit von 1200 V und einer CMOS-Treiberschaltung auf demselben Chip besteht. Diese Technologie könnte den Weg für die Integration weiterer Funktionen wie Sensoren und Logikschaltungen in SiC-Bauelementen ebnen und die Anwendung von Umrichtern erweitern.

Jobangebote+ passend zum Thema

Zwei Forschungsergebnisse kombiniert

Zunächst haben die Forschenden am AIST einen IE-MOSFET (Implantation & Epitaxial MOSFET) und dann einen IE-UMOSFET (Implantation & Epitaxial Trench MOSFET) in Siliziumkarbid entwickelt. Danach entwickelten sie Basistechnologien zu SiC-CMOS für die Treiberschaltungen und charakterisierten die Fertigungsverfahrens. Diese beiden Forschungsergebnisse kombinierten die Forschenden nun, um einen monolithischen SiC-Leistungs-IC zu entwickeln und den Schaltbetrieb zu demonstriert.

Ein IE-MOSFET hat eine planare Struktur, bei der der Kanal und das Gate planar zur Bauteiloberfläche angeordnet sind. Dadurch befindet sich der Kanal in einem Bereich mit einer qualitativ hochwertigen Kristallstruktur, was den Durchlasswiderstand verringert. Demgegenüber besitzt der IE-UMOSFET eine Trench-Struktur, bei dem der Kanal und das Gate an den Seitenwänden eines Grabens (Trench) ausgebildet sind. Dadurch verringert sich der Durchlasswiderstand weiter.

Implementierung des SiC-Leistungs-ICs

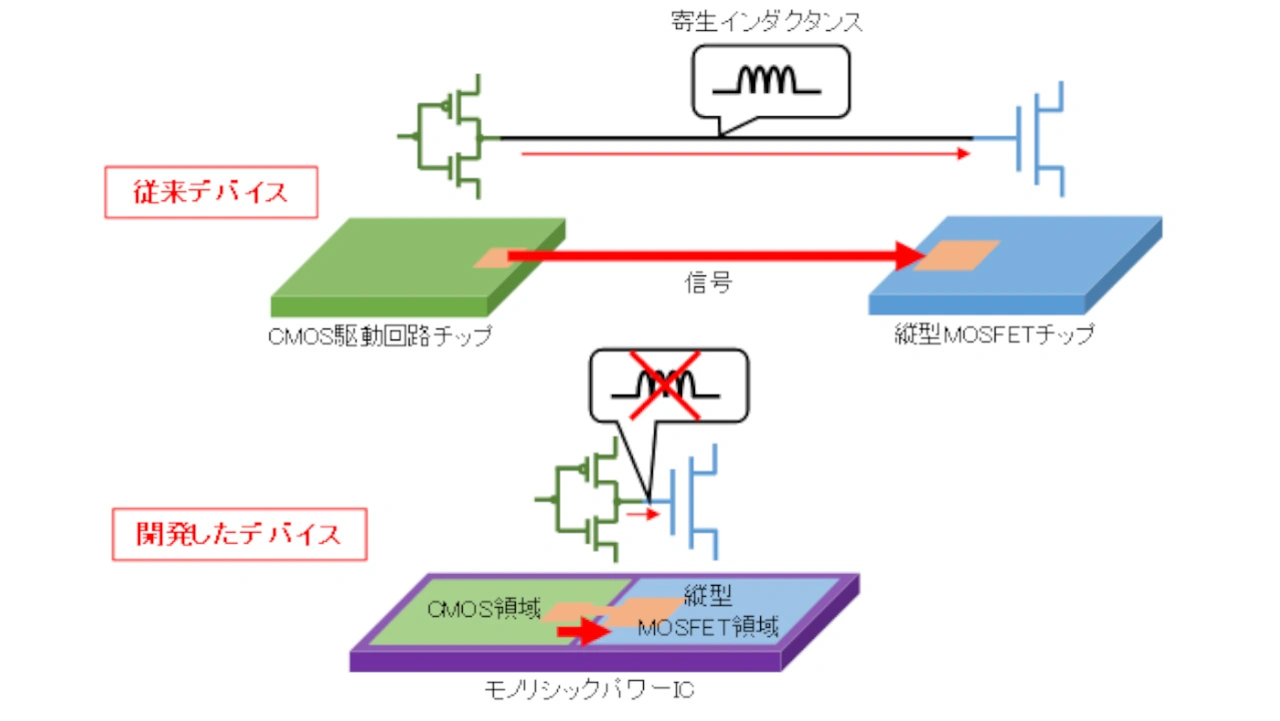

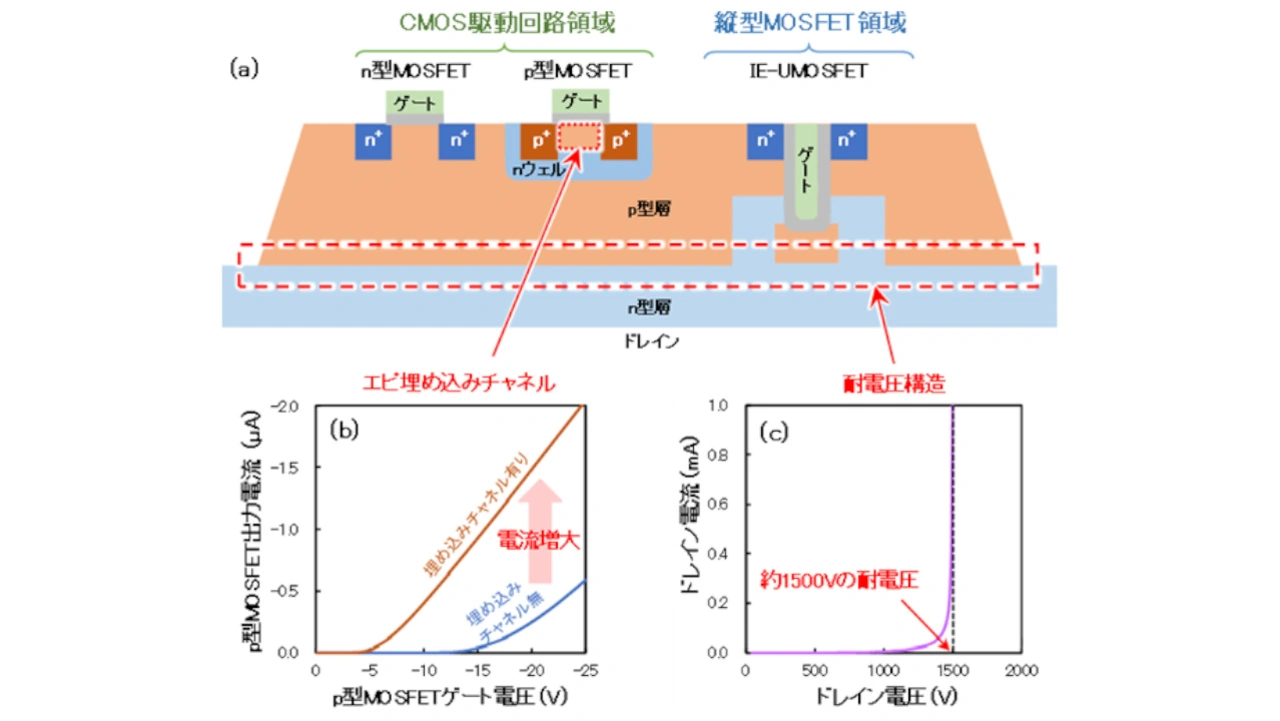

Das konzeptionelle Schema des monolithischen SiC-Leistungs-ICs zeigt Bild 1. Üblicherweise sind der CMOS-Treiber und der vertikale MOSFET auf separaten Chips untergebracht, und sind über Bonddrähte oder Leiterbahnen miteinander verschalten. Die parasitären Induktivitäten der Verdrahtung beeinträchtigen den Schaltvorgang und erhöhen die Verluste. Das monolithische Leistungs-IC minimiert die Länge der Signalverdrahtung und damit Größe und Gewicht von Umrichtern sowie die parasitäre Induktivität.

AIST entwickelt monolithisch integriertes SiC-Leistungs-IC

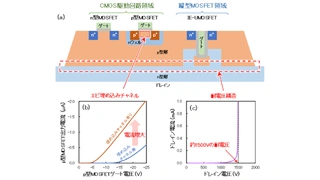

Die Merkmale des monolithisch integrierten SiC-Leistungs-ICs sind in Bild 2 dargestellt. Bei dem vertikalen MOSFET handelt es sich um einen IE-UMOSFET, während die CMOS-Treiberschaltung auf einer gemeinsamen p-leitenden Schicht mit dem IE-MOSFET aufgebaut ist. Dadurch liefert der Treiber sowohl einen höheren Ausgangsstrom und erreicht eine höhere Spannungsfestigkeit.

Bei SiC-CMOS-Schaltungen ist der Ausgangsstrom bei p-leitenden MOSFETs im Allgemeinen wesentlich geringer als der Ausgangsstrom von n-leitenden MOSFETs. Dies verhindert, dass mit SiC-CMOS-Treiberschaltungen einen Leistungs-MOSFET schnell schalten kann. Die Forschenden am AIST haben sich die Eigenschaft zunutze gemacht, dass die p-leitende Schicht von IE-UMOSFETs durch einen epitaktischen Film mit hoher kristalliner Qualität gebildet wird, um einen im Epi eingebetteten Kanal fast ohne Änderungen im Herstellungsprozess zu bilden. Dadurch ist es uns gelungen, den Ausgangsstrom des p-leitenden MOSFETs um den Faktor vier zu erhöhen (Bild 2(b)).

Durch Integration der SiC-CMOS-Schaltung in eine spannungsfeste Struktur, wie sie bei IE-UMOSFETs üblich ist, lässt sich die empfindliche Treiberschaltung von einer Drain-Spannung von 1500 V isolieren, ohne zusätzliche Herstellungsprozesse zu erfordern (Bild 2(c)).

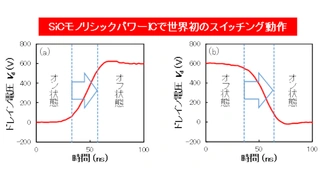

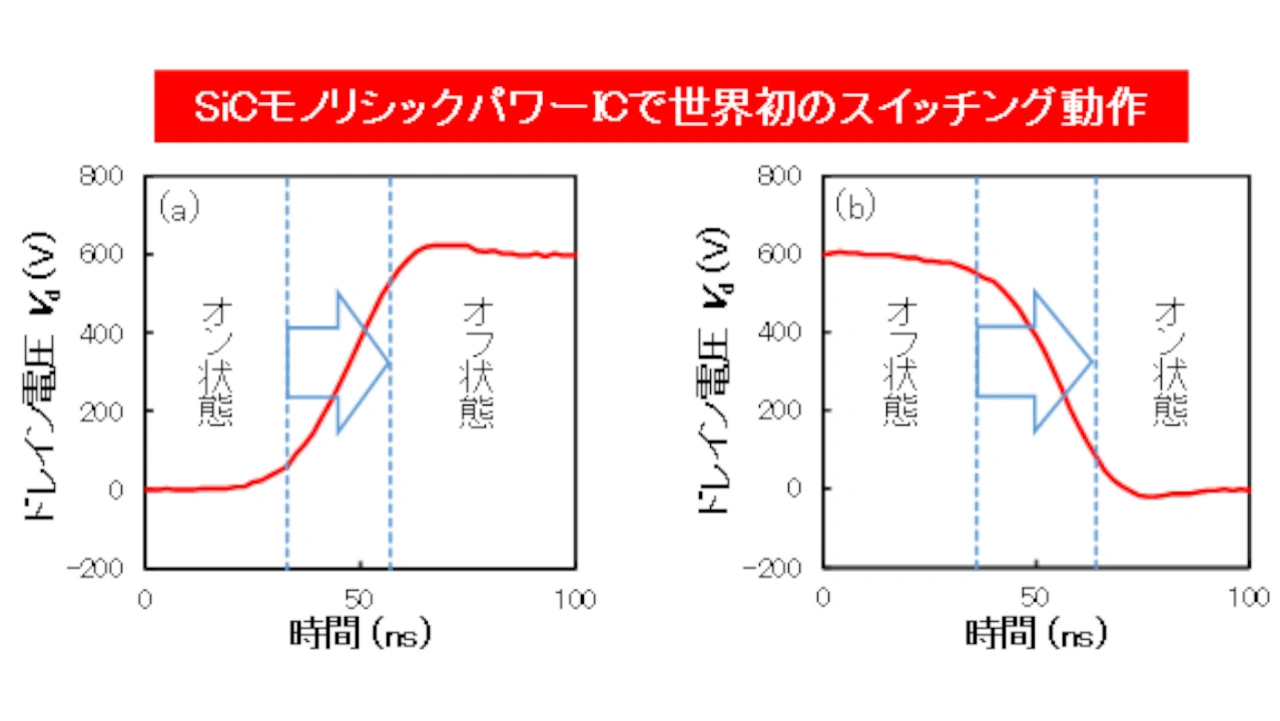

Die Schaltverläufe des monolithischen SiC-Leistungs-ICs sind in Bild 3 dargestellt. Der Schaltvorgang wurde bei einer Drain-Spannung von 600 V und einem Drain-Strom von 10 A durchgeführt.

Ausblick

In Zukunft wollen die Forschenden den Ausgangsstrom der SiC-CMOS-Treiberschaltung weiter erhöhen, damit monolithische SiC-Leistungs-ICs schneller schalten können. Darüber hinaus sollen auch Sensoren und Logikschaltungen integriert werden, um den Komfort zu erhöhen und die Anwendungsmöglichkeiten für Umrichter zu erweitern, indem sie einen höheren Funktionsumfang bieten.