Plus 37 Prozent pro Jahr

Die Advanced-Packaging-Rakete zündet

Der Advanced-Packaging-Markt wird bis 2029 auf 28 Mrd. Dollar wachsen – was einem Plus von nicht weniger als 37 Prozent pro Jahr entspricht.

Foundries, allen voran TSMC, große IDMs wie Intel, führende Speicher-IC-Hersteller wie Micron, Samsung, SK Hynix und YMTC sowie OSATs wie ASE, SPIL, JCET und Amkor sind auf der Jagd, um sich ihre Anteile im Advanced-Packaging-Markt zu sichern.

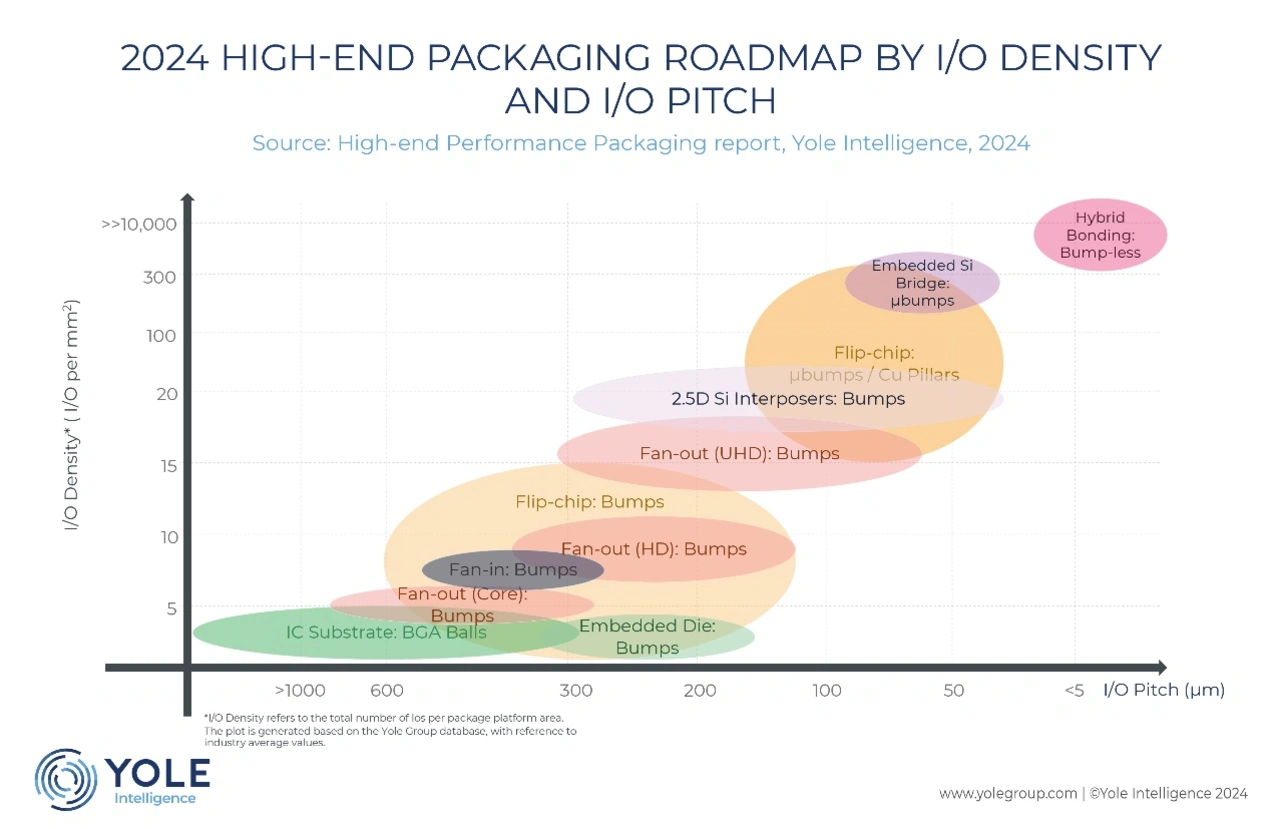

Das Ziel der neuen High-Performance-Packaging-Plattformen – unabhängig von ihrem Typ – besteht laut Yole darin, den Abstand zwischen den Verbindungen zu reduzieren, am besten so weit, dass kaum ein Unterschied zwischen der Performance auf dem Chip und der zwischen den Chips festzustellen ist. Das gelingt unter anderem über Through-Silicon-Vias, Through-Mold-Vias (TMV), Microbumps und Hybrid Bonding.

»Zusätzlich schrumpfen die Durchmesser der Vias genauso wie die Höhe der Wafer. Beides ist eine Voraussetzung, um komplexe monolithische Dies und Chiplets integrieren zu können – und damit die Leistungsaufnahme verringern und die Packungsdichte erhöhen zu können«, sagt Vishal Saroha, Technology & Market Analyst, Semiconductor Equipment der Yole Group.

Jobangebote+ passend zum Thema

Der größte Markt für Chips, die mit Hilfe von Advanced-Packaging-Techniken hergestellt werden, ist nach Ansicht der Analysten von Yole der Sektor Telekom und Infrastruktur, auf den 67 Prozent des Advanced-Packaging-Umsatzes 2023 entfallen sind. Auf Platz zwei liegt der Sektor Mobile und Consumer, der laut der Prognose von Yole in den Jahren zwischen 2023 und 2029 mit durchschnittlich 50 Prozent pro Jahr am schnellsten wachsen wird. Dieses schnelle Wachstum sei von steigender Nachfrage und von höheren ASPs für die Advanced-Packaging-Chips getrieben. Insgesamt verschiebt sich die Wertschöpfung wegen der 2.5D- und 3D-Advanced-Packaging-Plattformen von der Front-End-Fertigung in Richtung Back-End-Fertigung.

Als eine Schlüsseltechnologie sieht Yole das Hybrid Bonding für 3D-SoCs an, denn es ermöglicht kleinere Rasterabstände zwischen den Anschlüssen und SoCs mit größeren Flächen. Das Hybrid Bonding vereinfacht es, die Chiplets partitionierter SoCs zu platzieren und erlaubt die heterogene Integration. Technisch ganz vorne mit dabei ist TSMC, gefolgt von Intel mit Foveros Direct und Samsung mit X-Cube. Außerdem wird Die-to-Wafer-Bonding auf der HBM4E-Ebene einziehen, wenn 16 DRAMs übereinandergestapelt werden.

Der Trend im Advanced Packaging geht dazu, 2.5D- und 3.0-Plattformen in einem einzigen Chips zu kombinieren, was auch als 3.5D-Packaging bezeichnet wird. In künftigen Advanced Packages werden also Chiplets mit Hilfe von 3D-SoC, 2.5-Interposers, Embedded Silicon Bridges und integrierter optischer Komponenten aufgebaut werden.