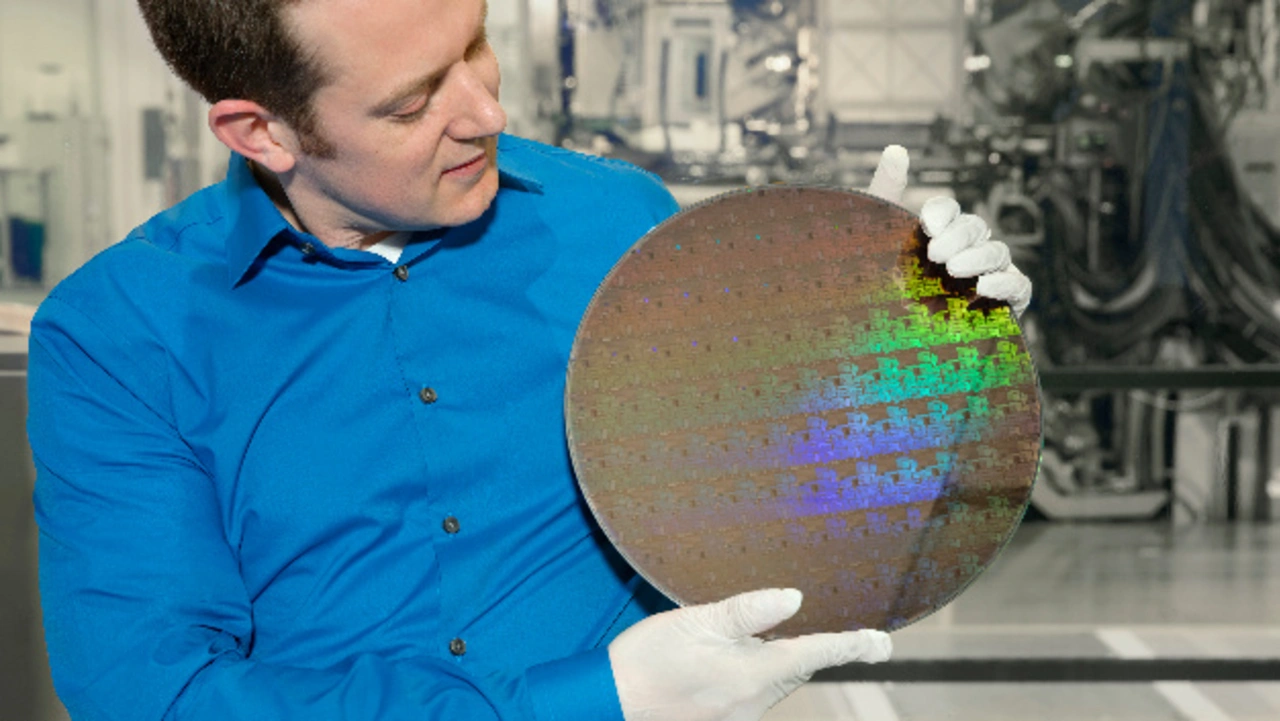

Die 5-nm-IC-Generation

IBM: Nanosheet-Transistoren statt FinFETs

Fortsetzung des Artikels von Teil 1

EUV ermöglicht maßgeschneiderte Transistoren

In der Lithografie setzen die Forscher wie schon für die 7-nm-ICs auf EUV (Extreme Ultraviolett). Dieses Verfahren erlaubt es, die Nanoschichten kontinuierlich auf die jeweils gewünschten Eigenschaften der resultierenden Transistoren in einem einzigen Fertigungsschritt einzustellen – das wäre mit FinFET-Transistoren nicht möglich. Hier definiert die Höhe der Fins den Strom durch den Transistor. Zwar können die FinFETs auch auf 5 nm skaliert werden, aber den Abstand zwischen den Fins zu verringern, führt nicht dazu, dass mehr Strom für fließen kann, um eine höhere Leistungsfähigkeit zu erreichen.

»Bereits 2018 planen wir den 7-nm-Prozess in unserer Fab 8 hochzufahren und entwickeln parallel dazu die Prozesstechnik der nächsten Generation auf der 5-nm-Ebene, um unsere Kunden in die Lage zu versetzen, noch kleinere, schnellere, und kosteneffizientere ICs produzieren zu können«, sagt Gary Patton, CTO und Head of Worldwide R&D von Globalfoundries.

IBM arbeitet bereits seit zehn Jahren an der Entwicklung der Nanosheet-Technik. Die Forschungsarbeiten haben Wissenschaftler der beteiligten Firmen in der von IBM geführten Allianz im NanoTech Complex an den SUNY Polytechnik Institute Colleges of Nanaoscale Science and Engineering in Albany durchgeführt. »Die Partnerschaft von SUNY Poly mit IBM und Empire State Development zeigt, dass die Industrie, Regierungsstellen und die akademischen Forschungseinrichtungen erfolgreich zusammen arbeiten können – zum Nutzuen der ganzen Gesellschaft«, sagt Dr. Bahgat Sammakia, Interim President vom SUNY Polytechnic Institute.

Jobangebote+ passend zum Thema

- IBM: Nanosheet-Transistoren statt FinFETs

- EUV ermöglicht maßgeschneiderte Transistoren