IEDM 2019

Unsere Top 10 der Halbleiter-Trends

Fortsetzung des Artikels von Teil 1

KI, Neuronale Netze und Neuromorphes Computing

Das Thema KI war in verschiedenen Sessions präsent, vor allem mit Konzepten, Recheneinheiten und Speicher näher zusammenzubringen. Ziel ist das Prinzip des In-Memory-Computings. Andere Ansätze verfolgen die Abbildung biologischer Strukturen in Chips mit neuronalen Netzen oder neuromorphem Computing. CEA-Leti und Macronix präsentierten dazu zwei Top-Papers.

6. CEA-Leti mit einem vollständig integrierten Impuls-getriebenen Neuronalem Netz

7. Macronix mit optimiertem Flash-Speicher für tiefe neuronale Netze

CEA-Leti mit vollständig integriertem Impuls-getriebenen Neuronalem Netz

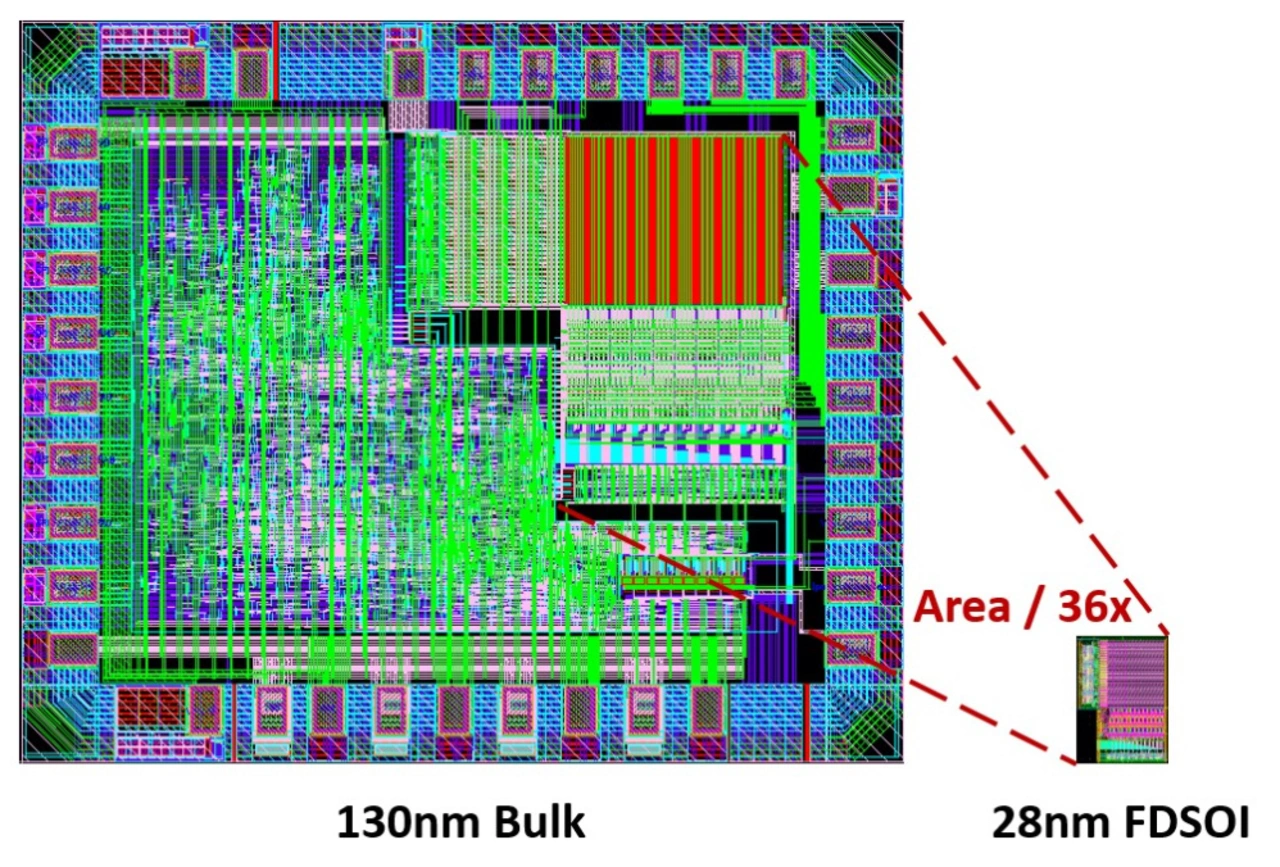

Das französische Mikroelektronik-Forschungsinstitut CEA-Leti berichtete über das erste vollständig integrierte Impuls-getriebene Neuronale Netz (Spiking Neural Network – SNN) auf einem Chip. Spiking Neuronale Netze sind energieeffizient und versuchen, die biologische neuronale Funktionsweise nachzuahmen, indem sie Informationen auf der Basis von »Spikes« oder diskreten Ereignissen, die zu einem Zeitpunkt auftreten, gegenüber kontinuierlichen Werten klassifizieren. CEA-Leti hat einen 130-nm-CMOS-Testchip mit analogen Neuronen und RRAM-basierten Synapsen (Resistive RAM) gebaut, der monolithisch auf CMOS-Bausteinen integriert ist. Der Chip zeigte eine Klassifizierungsgenauigkeit von 84 % auf der MNIST-Datenbank für handgeschriebene Ziffern (die zum Training von Bildverarbeitungssystemen verwendet werden), mit einer 5-fach geringeren Energieaufnahme auf Synapsen- und Neuronenebene (3,6 pJ) im Vergleich zu anderen Chips, die formale Programmiermethoden zur Bildklassifizierung verwenden. Die Forscher schätzen, dass der Umstieg zum 28-nm-Knoten von 130 nm zu einer 10-fachen Energieverringerung und einer 30-fach höheren Dichte führen könnte, und dass die Verwendung von RRAM zum Aufbau von Multi-Level-Speicherzellen im Vergleich zu den Single-Level-Zellen im Testchip die synaptische Dichte um das 4-fache reduzieren kann.

Jobangebote+ passend zum Thema

Macronix mit optimiertem Flash-Speicher für tiefe neuronale Netze

Umfangreiche mathematische MAC-Operationen (Multiply/Accumulate) sind das Herzstück von Deep Learning basierten neuronalen Netzen (DNNs). Es ist jedoch sehr energieintensiv, Daten zwischen Prozessor und Speicher hin- und herzuschaufeln um sie zu verarbeiten, und es werden verschiedene »Compute-in-Memory«-Ansätze (CIM) erforscht, um beides näher zusammenzubringen. Die Forscher des taiwanesischen Flash-Speicher-Spezialisten Macronix erörterten, welche Vorteile ein nichtflüchtiger SLC-3D-NAND-Flash-Speicher (Single-Level-Cell) bezüglich Dichte und Kosten gegenüber RRAM für DNNs mit hoher Dichte (>100 Mbit) aufweist. Sie beschrieben, wie sie ihn für die Verwendung in einem CIM-Beschleuniger für DNNs optimiert haben. Dazu konstruierten sie einen SLC-Single-Gate-Vertikalkanal-64-Gbit-Chip mit 16 Ebenen, der einen ultra-niedrigen Einschalt-Strom (Ion = 2 nA) und Ausschaltstrom-Strom (Ioff << 1 pA) aufweist. Das hohe Ein/Aus-Verhältnis bietet eine so große Bandbreite, dass >10.000 Speicherzellen parallel summiert werden können, was zu einer hohen Energieeffizienz (TOPS/W von ca. 40) bei gleichzeitig hoher Genauigkeit und Fehlertoleranz führt.

»More than Moore« für Kommunikation und Power

Neben der weiterhin fortschreitenden Skalierung nach Moore’s Law gibt es auch Forschungsrichtungen die nach »More than Moore« sich um die Integration von Photonik oder Leistungselektronik kümmern. Hier sind drei interessante Vertreter:

8. STMicroelectronics mit einer 400-Gbit/s-Photonik-Plattform

9. EPFL mit außergewöhnlicher GaN-auf-Si-Leistung

10. CEA-Leti mit hochdichter Dünnschicht-Batterie

STMicroelectronics mit einer 400-Gbit/s-Photonik-Plattform

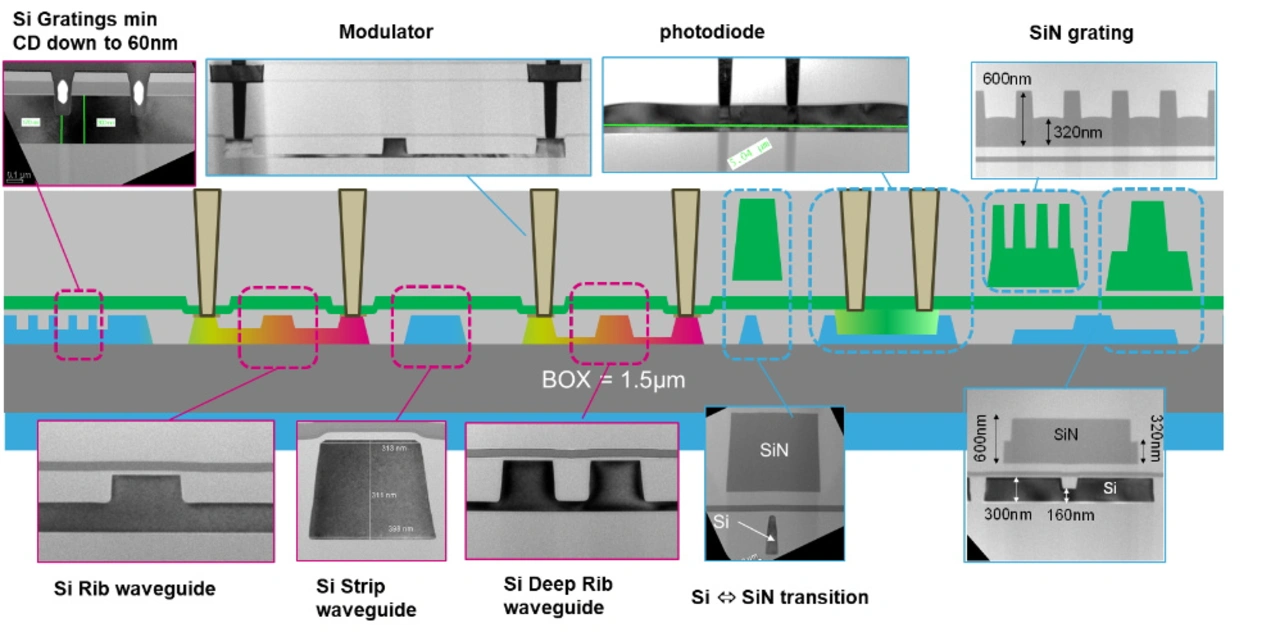

»Daten sind das neue Öl«, heißt es. So explodieren derzeit die Kapazitäten von Rechenzentren. Daten werden innerhalb der Rechenzentren über Glasfaser mit Hilfe von Silizium-Photonen-Schnittstellen (lichtbasiert), die mit Datenraten von 100 Gbits/s arbeiten, weitergeleitet. Aber der Verkehr in Cloud-Rechenzentren wächst um fast 30 % pro Jahr, und es wird bald notwendig sein, diese Datenraten zu steigern. Ein vom französisch-italienischen Halbleiterhersteller STMicroelectronics-geführtes Team hat eine neue Silizium-Photonik-Technologieplattform vorgestellt, die auf 300-mm-SOI-Wafern aufgebaut ist und Chips mit Datenraten von 400 Gbit/s ermöglicht (jeder Baustein hat 4 Kanäle, die jeweils mit 100 Gbit/s arbeiten, also insgesamt 400 Gbit/s). Optische Kopplung und Polarisationsmanagement sind dabei die Schlüsselanforderungen. Die Bausteine umfassen eine 60-GHz-Hochgeschwindigkeits-Fotodiode und einen hocheffizienten Hochgeschwindigkeits-Phasenmodulator. Die Forscher bei ST haben auch Bauelemente mit einer zusätzlichen SiN-Wellenleiterschicht für eine höhere Kopplungseffizienz realisiert, um die sich abzeichnenden Anforderungen an die Datenübertragung zu erfüllen. Außerdem habe die Photonik-Plattform den Wissenschaftlern zufolge das Potenzial, auch die Anforderungen von Anwendungen außerhalb von Rechenzentren zu erfüllen, wie z.B. in der Automobilindustrie.

EPFL mit außergewöhnlicher GaN-auf-Si-Leistung

Laterale GaN-on-Si-Bausteine sind vielversprechend für fortschrittliche Leistungs-ICs, da sie eine hohe Transistorleistung mit niedrigen Kosten kombinieren und physikalisch kleinere Systeme ermöglichen. Obwohl GaN-HEMTs kommerziell erhältlich sind, gibt es immer noch viel Raum, um ihre Leistung bis zum vollen Potenzial von GaN auszuschöpfen. Weitere Leistungssteigerungen erfordern eine deutliche Verbesserung des On-Widerstands bei gleichzeitiger Beibehaltung der hohen Durchbruchspannung. Ein Team unter der Leitung der EPFL (Föderale Polytechnische Hochschule Lausanne) hat neuartige laterale Mehrkanal-AlGaN/GaN-Leistungsbauelemente mit hoher Durchbruchspannung (1230 V) und niedrigem On-Widerstand (2,8 Ωmm) vorgestellt, die zu einer hervorragenden Leistungsdichte von 3,2 GW/cm2 führen. Die Forscher nennen diese Bauelemente MOSHEMTs, und sie haben eine mehrkanalige FinFET-ähnliche Architektur mit schrägen Tri-Gates, deren Struktur modifiziert werden kann, um die Leistung der Bauelemente »abzustimmen«. Der Einschaltwiderstand liegt etwa 5 mal niedriger als es bei dieser Durchbruchspannung bei einkanaligen Transistoren üblich ist. Bislang hat es sich als schwierig gezeigt, mehrere parallele Kanäle mit einer typischen Gate-Architektur zu steuern. Aber die Tri-Gate-Struktur hat sich dabei als effektiv herausgestellt und eignet sich für den Bau von normally-off- und damit ausfallsicherer (fail-safe) Bauelemente.

CEA-Leti mit hochdichter Dünnschicht-Batterie

Die Miniaturisierung der Elektronik hat große Fortschritte gemacht, aber die Miniaturisierung der Stromversorgungen konnte nicht Schritt halten. Obwohl integrierte elektrochemische Kondensatoren eine hohe Leistungsdichte, einen hohen Frequenzgang und neuartige Formate bieten, sind ihre niedrigen Energiedichten für MEMS und autonome Geräte, die lange Ladezeiten benötigen, von begrenztem Wert. Forscher des CEA-Leti berichteten von einer Dünnschichtbatterie mit der bisher höchsten Flächenenergiedichte (890 μAh/cm-2) und einer hoher Leistungsdichte (450 μAh/cm-2). Die Dünnschichtbatterie, die auf Siliziumwafern mit UV-Fotolithografie und Ätzen für die aufeinanderfolgende Abscheidung und Strukturierung jeder Schicht aufgebaut ist, integriert eine 20 μm dicke LiCoO2-Kathode in einer Li-freien Anodenkonfiguration. Sie zeigte ein gutes Zyklenverhalten über 100 Zyklen, und die Tatsache, dass sie in einem Wafer-Level-Prozess aufgebaut wurde, eröffnet die Möglichkeit, diese Batterietechnologie eng mit zukünftigen elektronischen Schaltungen zu integrieren.

- Unsere Top 10 der Halbleiter-Trends

- KI, Neuronale Netze und Neuromorphes Computing