IEDM 2019

»Die Zukunft von Moore’s Law ist besser als jemals zuvor«

Moore’s Law wurde schon mehrmals für tot erklärt. Robert Chau, Senior Fellow bei Intel zweifelt daran und begründet in seiner Keynote auf der IEDM 2019 warum er das so sieht.

Den Auftakt des 65. International Electron Devices Meeting im San Francisco Hilton machte die Keynote von Robert Chau von Intel. Chau von Intel Components Research, Technology Development in Hillsboro, Oregon gab sich bezüglich der Weiterentwicklung der Halbleiterprozesstechnik mehr als zuversichtlich: »Die Zukunft von Moore’s Law ist besser als jemals zuvor«.

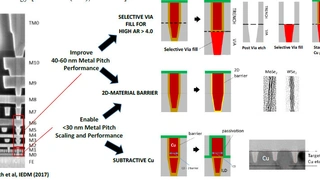

Seit 50 Jahren ist das Moore'sche Gesetz das Grundprinzip für die Halbleiterindustrie. Doch in den letzten Jahren gab es die Sorge, dass Moore‘s Law bald zum Erliegen kommt. Chau beleuchtete in seiner Präsentation Fortschritte in der Prozess- und Gehäusetechnik, die sich am Horizont abzeichnen und die beides ermöglichen werden, sowohl die monolithische als auch die heterogene 3D-System-Integration. Damit lässt sich die Skalierung nach Moore's Law fortschreiben bei gleichzeitiger Verbesserung der Rechenleistung/Watt. Jenseits der EUV-Lithographie gibt es neue Techniken der Strukturierung unter Verwendung von DSA (Direct Self Alignment), neue Verbindungstechniken (Interconnects) mit Subtraktions-Metallätz-Verfahren und 2D-Barrieren, Hochleistungs-Germanium und 2D-Material-Transistoren. Weitere Lösungsansätze sind GaN-Transistoren mit hoher Ladungsträgermobilität und großer Bandlücke, Hybrid-Bonding-Verfahren und omnidirektionale Verbindungsstrukturen. Darüberhinaus ermöglichen viele dieser neuen Technologien neue Lösungsansätze für integrierte Schaltungen wie die monolithische Ko-Integration von GaN-Bauelementen und Si-CMOS auf dem gleichen Wafer für zukünftige 5G- und Stromversorgungen. Durch die Verwendung dieser neuen und spannenden Technologien ganzheitlich und gekoppelt mit Technologie- und Design-Kooptimierung, ist die Zukunft von Moore's Law lyaut Chau besser denn je.

Jobangebote+ passend zum Thema

Transistor-Skalierung mit Nanodrähten und -bändern

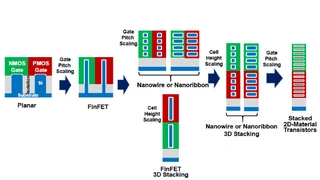

In den letzten zwei Jahrzehnten wurden Transistorskalierungen und Leistungssteigerungen durch Innovartionen ermöglicht, wie Strained-Si, High-K/Metal-Gate, FinFET und sich selbstausrichtende Kontakte. FinFETs verbesserten insbesondere das elektrostatische Verhalten gegenüber Planartransistoren und ermöglichte die weitere Skalierung der Gate-Länge LG. Jedoch für die weitere LG-Skalierung und damit Gate-Pitch-Skalierung über das hinaus, was der FinFET bieten kann, braucht es Gate-All-Around-Transistoren (GAA) wie Nanodrähte (nanowires) und Nanobänder (nanoribbons). Transistoren mit 2D-Kanal-Materialien wie MoS2, WS2 und WSe2 werden ebenfalls in Erwägung gezogen, da sie das beste elektrostatische Verhalten und die beste LG-Skalierbarkeit bieten. Sowohl GAA-Bauelemente als auch 2D-Materialtransistoren benötigen mehrere Kanäle für hohe Treiberströme. Zusätzlich zur Gate-Pitch-Skalierung lassen sich monolithische 3D-Transistoren stapeln, um die Zellenhöhe zu skalieren. Die Kopplung von GAA-Transistoren oder 2D-Material-Transistoren mit monolithischer 3D-Transistor-Stapelung ermöglicht die Skalierung sowohl von Gate-Pitch als auch der Zellenhöhe. Damit existiert ein brauchbarer Pfad für die Skalierung der Transistordichte und zur Fortsetzung von Moore's Law über das nächste Jahrzehnt hinaus.

Prozess- und Packaging-Innovation für Moore's Law.

Monolithische heterogene 3D-Integration

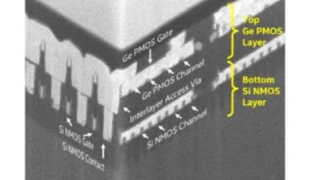

Die Fähigkeit zur monolithischen heterogenen Integration eröffnet viele attraktive technische Optionen wie Ge-PMOS/Si-NMOS für High-Performance-/Low-Power-CMOS und GaN-NMOS/Si-CMOS für energieeffiziente, kompakte Anwendungen wie 5G und Stromversorgungen. Solche Funktionen werden nicht durch direktes Materialwachstum ermöglicht aufgrund der unterschiedlichen Kristallgitter, sondern durch die Weiterentwicklung der Epitaxie und von 3D-Schichtübertragungstechniken. Ein Ge-PMOS-Transistor mit der besten jemals berichteten ION-IOFF-Leistung unter Einsatz von 3D-Layer-Transfertechnologie auf 300-mm-Wafern ist Inhalt eines eigenen Papers auf der IEDM. Darüber hinaus ist die branchenweit erste heterogene 3D-Integration von GaN-NMOS- und Si-PMOS-Transistoren im Enhancement-Modus auf 300-mm-Wafern mit hochohmigem Si(111)-Substrat gelungen, wobei GaN-MOCVD-Epitaxie und 3D-Schichtübertragungsverfahren zum Einsatz kamen.

- »Die Zukunft von Moore’s Law ist besser als jemals zuvor«

- Verbindungsstrukturen, Direkte Selbstanordnung und heterogene 3D-Systemintegration

- Jenseits von CMOS