RISC-V für Deutschland und Europa

Resilienz und technologische Souveränität

Fortsetzung des Artikels von Teil 1

Wo lohnt es sich RISC-V einzusetzen?

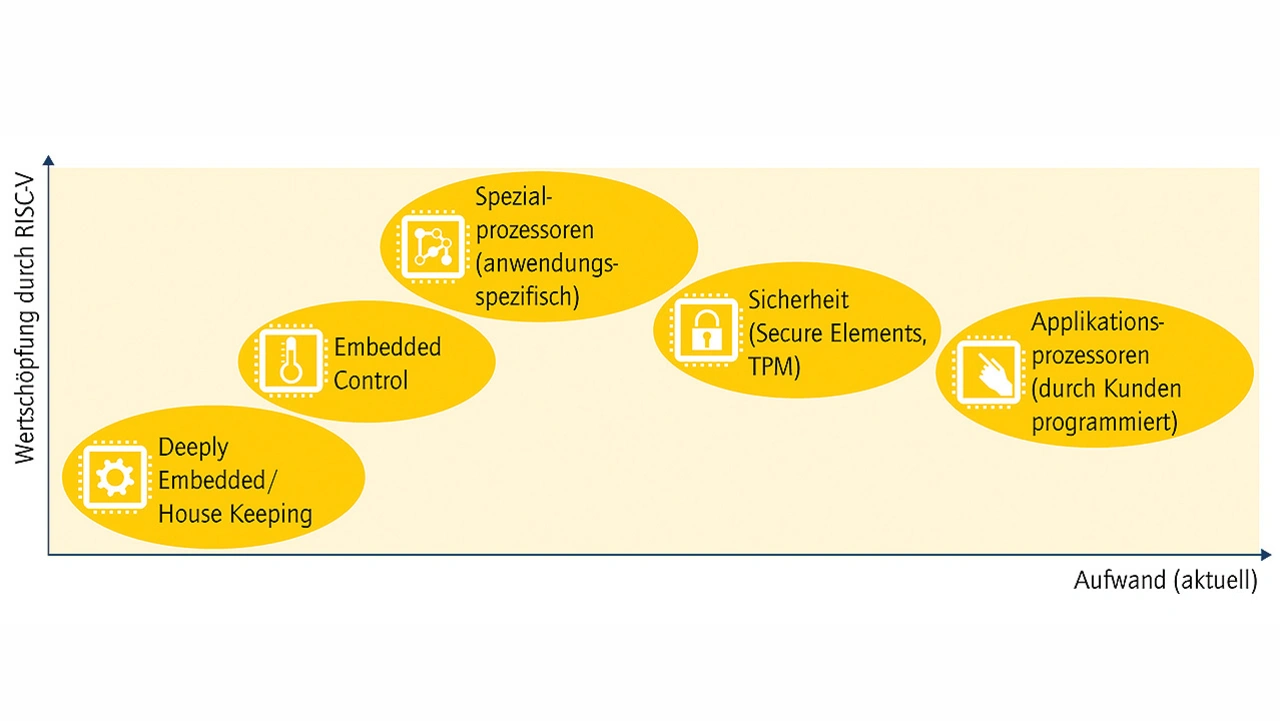

Die Experten von Acatech geben auf Basis der bereits beschriebenen Vor- und Nachteile konkrete Empfehlungen ab, wo ihrer Meinung nach RISC-V gewinnbringend eingesetzt werden kann:

➔ Deeply-Embedded- und Housekeeping-Prozessoren – in diesen Bereichen fallen Aufwand und Anforderungen an das benötigte Ökosystem für Entwicklung und Support vergleichsweise gering aus, was für RISC-V spricht. Bei Safety- oder Security-Hardware muss allerdings bedacht werden, dass nicht nur die Hardware, sondern auch die Software entsprechenden Anforderungen unterliegt, sprich in dem Fall spielt das dazugehörige Ökosystem eine ebenfalls wichtige Rolle. Acatech geht davon aus, dass RISC-V in diesem Produktsegment bereits Einzug gehalten hat, dementsprechend heißt es weiter:

»Unternehmen können sich mit einem Wechsel auf RISC-V-basierte Lösungen von den Randbedingungen proprietärer Lizenzen unabhängig machen.«

➔ Applikationsprozessoren – RISC-V in Applikationsprozessoren einzusetzen, könnte aus Sicht der Experten zu Produkten führen, die weniger komplex und potenziell auch energie- und flächeneffizienter sind, da bei RISC-V derzeit die Abwärtskompatibilität zu älteren RISC-V-Versionen keine Rolle spielt. Insbesondere heterogene Multicore-Architekturen lassen sich einfacher umsetzen, so die Experten. Darüber hinaus weisen sie darauf hin, dass Erweiterungen wie die RISC-V-Vektorerweiterung als technisch besonders elegant umgesetzt bewertet wird. Auch das RISC-V-Konzept zur Trennung verschiedener Zugriffsrechte (Privilege Level) sei im Vergleich zu älteren Architekturen »schlanker und effizienter«, denn die RISC-V-Entwickler haben aus den bereits gemachten Fehlern der älteren Architekturen gelernt.

»RISC-V bietet durch den besonders modularen Aufbau Vorteile für die formale Verifikation und damit für zertifizierbare Ausfall- und Informationssicherheit«, heißt es bei Acatech weiter. Diesen Vorteilen steht allerdings ein großes Problem gegenüber:

➔ Software. Acatech: »Da Applikationsprozessoren sehr große Softwaremengen benötigen, ist ein Umschreiben der Software nicht möglich. Der Schlüssel zu einer effizienten Portierung ist deshalb die RISC-V-Unterstützung von wichtigen Betriebssystemen als Abstraktionsschicht. So hat Google RISC-V zur Tier-1-Plattform für Android erklärt, und die Portierung von Android auf RISC-V macht rasche Fortschritte. Nichtsdestotrotz ist zu erwarten, dass es Jahre dauern wird, bis die von proprietären Befehlssätzen gewohnte Qualität erreicht ist. Ferner ist RISC-V eine offiziell unterstützte Plattform der Linux-Distributionen von Debian und Ubuntu. Für die Entwicklung eines solchen Ökosystems sind allerdings gute Hardwareplattformen essenziell – doch gerade in diesem Bereich sind chinesische Unternehmen in Vorleistung gegangen.«

➔ Spezialisierte Prozessoren – Acatech definiert Spezialprozessoren folgendermaßen: »Die Prozessoren sind für eine bestimmte Klasse von Anwendungen ausgelegt und werden auf diese Anforderungenoptimiert. Im Vergleich zu Applikationsprozessoren sind bei gleicher Fläche im günstigsten Fall Vorteile bei Leistung und Effizienz von einem Faktor 10 bis 100 für besondere Anwendungen erreichbar. Um dies zu ermöglichen, sind typischerweise grundlegend neue Prozessorarchitekturen erforderlich beziehungsweise grundlegende Modifikationen an Standardarchitekturen vorzunehmen. Also optimale Voraussetzungen für RISC-V, was Acatech mit folgendem Hinweis unterstreicht: »Zu diesem Zweck wurden im RISC-V-Befehlssatz eine Gruppe von Befehlen und Konfigurationsoptionen freigelassen, um anwendungsspezifische Instruktionen zu definieren. Diese Instruktionen ergänzen den Standardbefehlssatz, das heißt, eine auf einem Standardbefehlssatz lauffähige Software wird auch auf einem Spezialprozessor ausführbar sein. Entsprechend können die existierenden kommerziellen sowie Open-Source-Softwaretools und -Bibliotheken für die Entwicklung der Software weiterverwendet werden. Die architekturelle Weiterentwicklung ermöglicht effiziente Prozessoren, die auch in vergleichsweise großen, günstig zu fertigenden Strukturbreiten im zweistelligen Nanometerbereich aufgrund der technischen Vorteile konkurrenzfähig gegenüber nicht optimierten Standardprozessoren sind, welche mit den neuesten Fertigungstechnologien (unter 5 nm) gefertigt wurden.«

Auch auf der Tool-Seite sieht es laut den Experten eigentlich ganz gut aus, denn Tools, die Spezialbefehle als direkt in den Programmcode einfügbare Assembler- Instruktionen unterstützen, seien verfügbar. Probleme bereiten aus Sicht von Acatech aber die fehlenden Spezialisten. Sprich Fachpersonal, das einerseits über das Verständnis der Anwendungsdomäne verfügt, aber auch über Expertise in Hinblick auf maschinennahe Programmierung und Hardwarearchitekturen, die gebe es schlichtweg noch nicht. Dennoch gibt es auch in diesem Bereich Beispiele, bei denen Applikationsprozessoren bereits auf Basis von RISC-V umgesetzt wurden, laut Acatech aber vor allem im asiatischen Raum. In diesem Zusammenhang werden beispielsweise Shanghai Saifang Technology (StarFive) sowie T-Head (Teil von Alibaba) genannt.

➔ Embedded Control – in diesem Fall verweisen die Experten auf den Vorteil, dass mit RISC-V applikationsspezifische Lösungen dank wegfallender Architekturlizenzgebühren selbst bei kleineren Stückzahlen unterhalb von 100.000 Stück pro Jahr möglich sind. Das böte eine Möglichkeit zur Differenzierung bzw. in manchen Fällen überhaupt erst die Möglichkeit, eine Anwendung technisch zu realisieren. Darüber hinaus erhöhe die weitgehende Kompatibilität von RISC-V-basierten Prozessoren und FPGAs die Versorgungssicherheit und senke gleichzeitig die Kosten für Änderungen an bestehenden Systemen.

Dennoch wird jetzt nicht jedes Unternehmen auf RISC-V wechseln, denn für viele Mess- und Steuerungsanwendungen gibt es etablierte Standardprodukte mit umfangreicher Softwareunterstützung und einer etablierten Entwickler-Community. Und genau das fehlt, wenn es um RISC-V geht. Hinzu kommt noch, dass laut Acatech auch auf der Seite der Endkunden eine gewisse Skepsis gegenüber domänenspezifischen Prozessoren zu spüren ist. Und: »Zudem bleiben Neuentwicklungen von Mikrochips teuer und risikoreich, gerade in Bezug auf die Integration von analogen Funktionen für Sensoren und Kommunikationsschnittstellen«, so Acatech weiter. Diese Hürde könne aber durch den Zugang zu verfügbaren RISC-V-Tools mit gesicherter Qualität gesenkt werden. Als ein Beispiel für eine entsprechende Umsetzung verweist Acatech auf den Embedded-Control-Prozessor für die Motorsteuerung von Renesas hin. Und weiter: »Derartige Lösungen bieten hinsichtlich Energieeffizienz, Leistungsfähigkeit und Stückkosten Vorteile gegenüber Standardprodukten. Besondere Bedeutung gewinnt in diesem Segment zunehmend die Integration von KI-Fähigkeit in Endgeräten in Form von Embedded AI.«

➔ Secure Elements – Vertrauensanker als separater Chip oder in einem SoC implementiert, sind rein theoretisch einfach mit RISC-V umzusetzen, da ihre Komplexität gering ist. Problematisch ist allerdings, dass sie eine spezielle Implementierung benötigt, sodass die Hardware zum Beispiel gegen Seitenkanal- und Fehlerattacken gehärtet ist. Acatech weist außerdem darauf hin, dass grundsätzlich Risiken bezüglich versteckter Hardwaretrojaner sowie mögliche Hintertüren bestehen, wenn die Chips extern gefertigt werden. Die Experten erklären aber weiter, dass es aufgrund der Transparenz dank des offenen Quellcodes möglich ist, ein Design vollständig zu überprüfen. »Bei Verwendung von offenem Quellcode ist es mit vertretbarem Aufwand möglich, daraus eigene Designs zu erstellen und neue Funktionen, wie beispielsweise neue Kryptografie-Algorithmen, leicht zu integrieren.« Aber aus der Sicht der Experten müssten für eine weitere Verbreitung von RISC-V in Secure Elements hochwertige Open-Source-Designs zur Verfügung stehen, »für die auch Hardwareimplementierungen bezüglich Sicherheit evaluiert wurden, und langfristig kontinuierlich verbessert werden«. Außerdem stünden keine Open-Source-IPs für die analogen Schaltungen in Secure Elements zur Verfügung, einschließlich ihrer Technologieparameter aus der Fertigung. RISC-V wird natürlich aber trotzdem auch für Secure Elements genutzt. So verweist Acatech auf verschiedene Open-Source-Ansätze (z. B. OpenTitan von Google) oder laufende Projekte von Hensoldt Cyber, die selbstentwickelte RISC-V-Chips im Bereich der Sicherheit erforschen und vorantreiben. Actech weiter: »In SoCs integrierbare Secure Elements werden beispielsweise von der französischen Firma Tiempo Secure und von dem amerikanischen Unternehmen Rambus angeboten.«

Jobangebote+ passend zum Thema

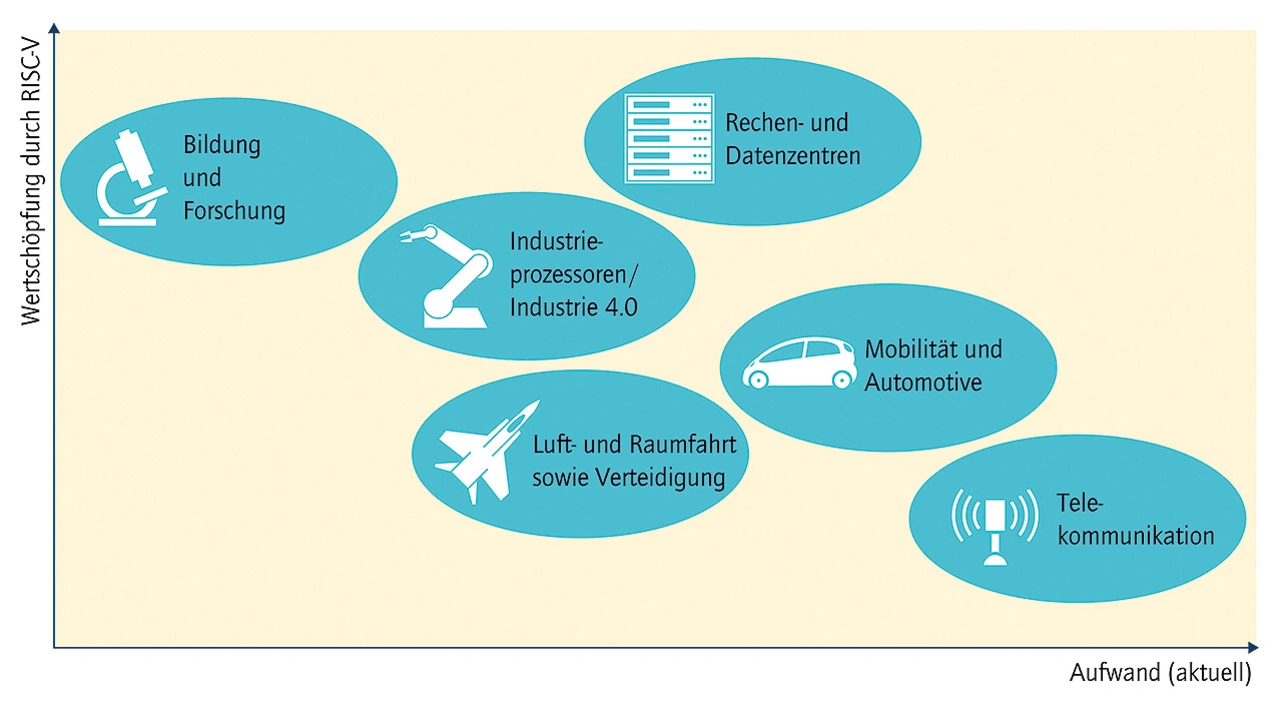

Anwendungsfelder für RISC-V

Die Einsatzmöglichkeiten sind ausgesprochen vielfältig:

Bildung und Forschung

Die Forschung im Bereich von Prozessoren und SoCs in Europa ging in den vergangenen zwei Jahrzehnten zurück, als Indikator verweist Acatech auf den Rückgang an Veröffentlichungen, die aus Kooperationen zwischen Universitäten und Unternehmen resultieren. RISC-V kann hier die Trendwende ermöglichen, plus die Chance, Studenten mit technischem und für die Industrie relevanten Know-how auszustatten. Darüber hinaus bestünde die Möglichkeit, dass mit RISC-V Universitäten und Unternehmen ihre eigenen Chips fertigen und testen können. Außerdem ließe sich mit RISC-V in der akademischen Forschung ein vollständiges Ökosystem ohne großen Aufwand aufbauen. Um einen Prozessorkern auf Basis von RISC-V zu entwickeln, kann eine breite Palette von unterstützenden Tools und Software genutzt werden. Dies umfasst Compiler, Betriebssysteme und weitere Entwicklungsumgebungen, die speziell für RISC-V konzipiert wurden.

Telekommunikation

Laut Acatech findet in der Telekommunikation ein Wechsel von einem Hardware- in einen Software-zentrierten Ansatz statt, wobei auf der Hardwareseite derzeit die beiden großen proprietären Befehlssatzarchitekturen dominieren. »Dies stellt eine potenzielle Bedrohung für die technologische Souveränität dar«, so die klare Aussage von Acatech. Die Experten sind überzeugt, dass RISC-V an dieser Stelle seine Vorteile zumindest theoretisch ausspielen kann, einschließlich Erweiterbarkeit des Befehlssatzes sowie niedrigere Entwicklungs- und Stückkosten. Aber als Schwierigkeit beim Umstieg dürften sich die großen Softwarepakete erweisen, die in den vergangenen zwanzig Jahren für die proprietären Architekturen geschrieben wurden. Acatech weiter: »Da Telekommunikationsprodukte zunehmend CISA/ENISA32 und anderen Überlegungen zur Cybersicherheit unterliegen, wird die Hürde für Änderungen (Softwaremigrationskosten) in dieser Code-Basis immer höher, zumal die Leistungsvorteile des Übergangs zu RISC-V von der Branche (noch) nicht angenommen wurden.«

Rechen- und Datenzentren

Einerseits weisen die Experten in diesem Zusammenhang darauf hin, dass sich mit RISC-V maßgeschneiderte Prozessoren für Rechenzentren realisieren lassen. Andererseits verfüge RISC-V auch über das Potenzial, dass rund um eine solche Architektur ein großes Ökosystem entwickelt werden kann, was in der Summe dazu führe, die Vielfalt und Wettbewerbsfähigkeit in diesem Bereich zu steigern. Allerdings fehle auf der Softwareseite noch das entsprechende Ökosystem, sodass derzeit die Vorteile dieser Architektur noch nicht voll ausgeschöpft werden können.

Automotive

Die Experten von Acatech konstatieren, dass im Automotive-Segment eine zunehmende Konsolidierung auf Arm stattfindet, was eine potenzielle Gefahr für die technologische Souveränität darstelle, »insbesondere für Exporte nach und die Produktion in China«. RISC-V könne dem entgegenwirken. Dank der Erweiterbarkeit des Befehlssatzes böte RISC-V außerdem großes Innovationspotenzial und die »Option für den globalen Export ohne Handelsrestriktionen sicherzustellen«. Allerdings gebe es im Automotive-Bereich das sogenannte Henne-Ei-Problem: »Ein ausreichendes Angebot auf Grundlage von RISC-V wird erst dann existieren, wenn die Nachfrage groß genug ist. Diese wird sich aber nicht entwickeln, wenn für die aktuelle Nachfrage noch kein zufriedenstellendes Angebot zur Verfügung steht.«

Luft- und Raumfahrt sowie Verteidigung

Das existierende RISC-V-Ökosystem stellt aus der Sicht von Acatech einen guten Ausgangspunkt für Neuentwicklungen von Aerospace-Komponenten dar. Aufgrund hoher Anforderungen bei Sicherheit und Zertifizierbarkeit seien Standardkomponenten häufig unzureichend. Durch die Stärkung der Designkompetenz und der freien Verfügbarkeit von RISC-V könnten eigene Chipentwicklungen für Aerospace-Komponenten realisiert werden, wobei die Experten selbst darauf hinweisen, dass die Flugzeughersteller derzeit noch nicht entschieden haben, ob sie überhaupt Eigenentwicklung vorantreiben wollen oder lieber auf Zulieferprodukte setzen. Für Weltraumanwendungen wiederum könnten die hohen Anforderungen bezüglich Sicherheit sowie Sonderanforderungen dank der Erweiterbarkeit von RISC-V erfüllt werden. Acatech: »Mit dem Einsatz von RISC-V würden Randbedingungen eines proprietären Befehlssatzes wegfallen, und die technologische Souveränität der beteiligten Unternehmen könnte gestärkt werden.«

Industrieprozessoren und Industrie 4.0

In diesem Anwendungssegment werden häufig Standardkomponenten eingesetzt, außer es handelt sich um sicherheitskritische Anwendungen, dort besteht aus Sicht der Acatech-Experten »ein großer Bedarf an differenzierter Elektronik, die auf Eigenentwicklungen mit anwendungsspezifischen Erweiterungen basiert. Für all diese Komponenten sind stabile Lieferketten notwendig. Zusätzlich bedeutet der Einsatz von Komponenten, die proprietäre lizenzierte Funk- tionselemente enthalten, dass Handelsbeschränkungen auch für die Produkte gelten, in denen diese Komponenten eingesetzt werden.« RISC-V böte zwar keine Leistungsvorteile im Vergleich zu den Komponenten, die auf proprietären Befehlssatzarchitekturen basieren, aber der Verzicht auf proprietäre Befehlssätze mache Unternehmen von den Einschränkungen unabhängig, die mit der Nutzung solcher Befehlssätze einhergehen.

Unternehmen könnten anwendungsspezifische Erweiterungen eigenständig entwickeln und integrieren. Acatech weiter: Dieser Aspekt ist insbesondere in Bezug auf Komponenten mit geringer Komplexität, zum Beispiel für eine echtzeitfähige Deeply-Embedded-Anwendung interessant, da die Aufwände für die Unternehmen sowie die geforderte Expertise überschaubar sind und so die ökonomischen Vorteile realisiert werden können. Plus dem bereits bekannten Vorteil: »Von den drei möglichen Hebeln, um Handelsbeschränkungen durchzusetzen – Blockieren von Design-IP, Chipentwicklungstools und Fertigungsprozess –, wäre die Verfügbarkeit von Design-IP erfolgreich adressiert.« Voraussetzung dafür sei allerdings, dass ein stabiles und effizien- tes Ökosystem für RISC-V aufgebaut und aufrechterhalten wird, einschließlich der Verfügbarkeit von Know-how, Design-IPs, spezialisierte Design- und Verifikations-Tools sowie die notwendige Dokumentation für Zertifizierungen nach relevanten Standards für funktionale und IT-Sicherheit.

Nach Unterlagen von Acatech

- Resilienz und technologische Souveränität

- Wo lohnt es sich RISC-V einzusetzen?