Adaptive Computing

Autonom mithilfe von KI im Edge

Fortsetzung des Artikels von Teil 1

KI im Edge beschleunigen

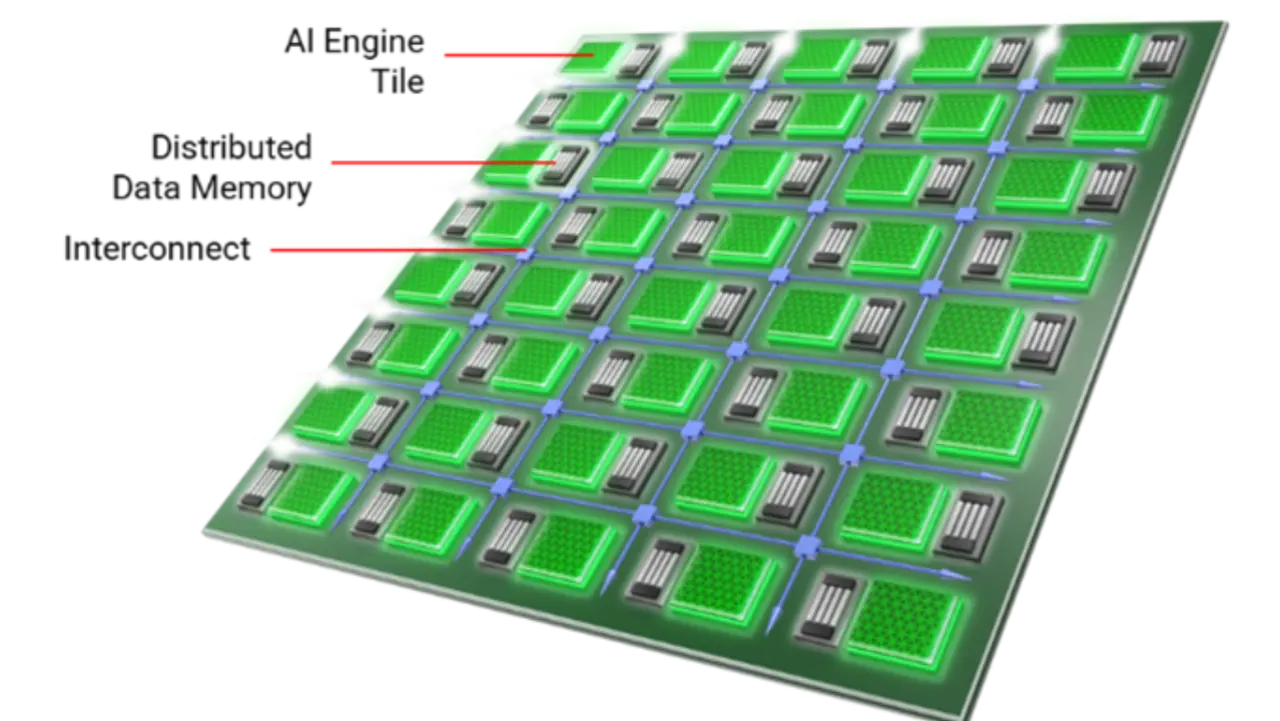

Eine der wichtigsten Weiterentwicklungen von Versal ist das AI-Engine-Array, in dem Hunderte von Vektorprozessoren (VPUs) zusammengefasst sind.

Jede VPU verfügt über RAM, das unmittelbar in Nachbarschaft liegt und einen Zugriff mit geringer Latenz über eine Schnittstelle mit großer Bandbreite ermöglicht. Angrenzende VPUs können diesen Arbeitsspeicher gemeinsam nutzen, wodurch eine Cache-freie Hierarchie entsteht, die flexibel zugewiesen werden kann. Ein Interconnect mit einer Bandbreite von 10 TB/s verbindet die VPUs. Das Array von Vektorprozessoren, zusammen mit dem verteilten Speicher und der flexiblen Verbindung ergeben zusammen eine Software-programmierbare Architektur, die von der Hardware-Seite her anpassbar ist und gleichzeitig eine hohe Bandbreite und Parallelität bei geringem Stromverbrauch und geringer Latenzzeit bietet. Der Signalverarbeitungsdurchsatz ist in Hinblick auf die Beschleunigung von Cloud-KI, Bildverarbeitung und drahtlose Signalverarbeitung im Vergleich zu GPUs um bis zu zehnmal höher.

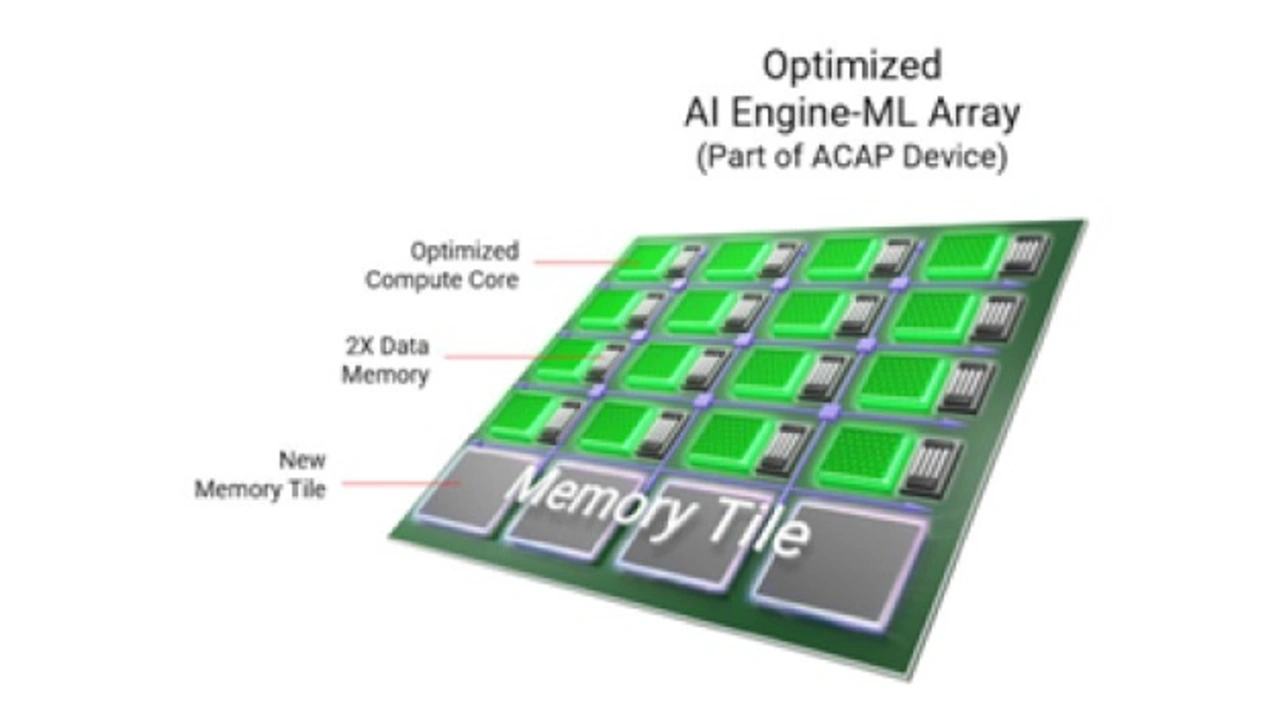

Mit den adaptiven Versal AI Edge-Plattformen wurde diese Architektur weiter optimiert, um die speziellen Anforderungen intelligenter Edge-Geräte zu erfüllen. Insbesondere die AI Engine-ML (AIE-ML) stellt eine für maschinelles Lernen optimierte Variante der AI-Engine dar.

Im Vergleich zur regulären »Versal AI Engine« unterstützt die »AI Engine-ML« von Haus aus eine schnellere und effizientere Handhabung der INT4-Integer-Quantisierung und BFLOAT16-16-Bit-Gleitkommaberechnungen, die in Machine-Learning-Anwendungen üblich sind. Außerdem wurde die INT8-Leistung durch zusätzliche Multiplikatoren im Kern verdoppelt. Darüber hinaus wurde der eng gekoppelte Speicher verdoppelt und bis zu 38 MB zusätzlicher Speicher für das gesamte AI-Engine-Array mit hoher Zugriffsgeschwindigkeit hinzugefügt, so dass sich die Rechenleistung für maschinelles Lernen um das Vierfache erhöht und die Latenz halbiert wird.

Die AIE-ML kann sowohl heterogene Arbeitslasten als auch ML-Anwendungen bewältigen, während die ursprüngliche 32-Bit-Verarbeitung der bestehenden AI-Engines arithmetische Berechnungen mit Datenformaten wie INT32 und FP32 beschleunigt. Das sorgt für eine ausgewogene Performance bei verschiedenen Arbeitslasten wie Beamforming in Ultraschallanwendungen und die Verarbeitung von LiDAR/Radar-Daten.

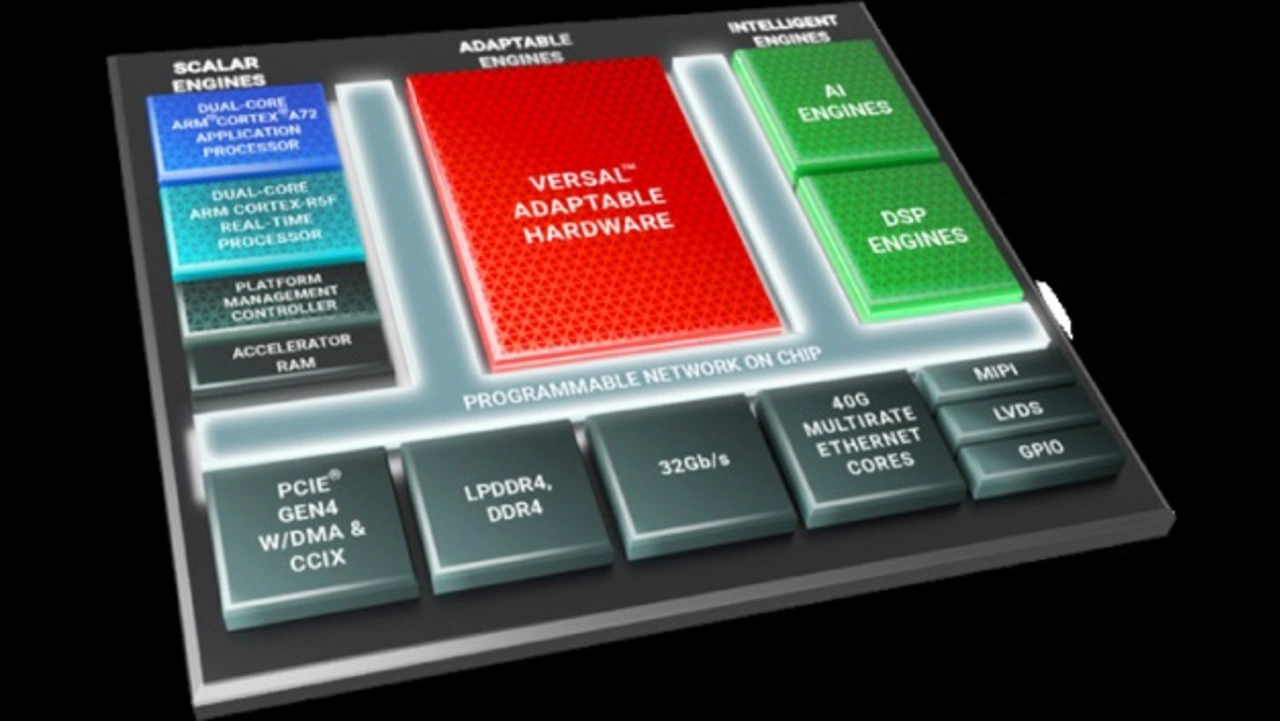

Interaktionen mit dem Speicher sind typischerweise der Engpass in Prozessorsystemen dar. Die neue Edge-orientierte Plattform adressiert dieses Problem, und fügt Beschleunigungs-RAM, ein 4-MB-großer Block mit Hochleistungsschnittstelle hinzu, auf den alle Verarbeitungsmodule auf dem Chip zugreifen können. Darin können die KI-Engines kritische Rechendaten aus neuronalen Netzen beim Inferenzieren abspeichern, was die Leistungsaufnahme und die Latenzzeit reduzieren. Somit können diese Echtzeitprozessoren sicherheitskritischen Code auf dem Chip belassen, was neben einer geringeren Latenzzeit auch dazu beiträgt, einen sichereren Betrieb zu gewährleisten.

Entwickler, ob erfahrene FPGA-Designer oder Datenwissenschaftler mit wenig Erfahrung im Hardware-Design, können diese Bausteine mit ihren bevorzugten Tools, Sprachen wie C oder Python und KI-Frameworks wie Caffe, TensorFlow und Pytorch nutzen. Es gibt eine breite Palette von KI- und Bildverarbeitungsbibliotheken für die Versal Adaptable Engines oder die Intelligent Engines, Unterstützung für ROS und ROS2 (Robot Operating System) sowie einen Support für sicherheitskritische Designs mit RTOSes, wie QNX, VxWorks und Xen, die funktionale Sicherheitsstandards wie ISO 26262 (Automobilindustrie), IEC 61508 (Industrie) und DO-254 (Verteidigung) erfüllen. Das Design zur Erfüllung von IEC 62443 IT-Sicherheitsstandards wird ebenfalls unterstützt.

Mit ihrer Architektur ist die Familie außerdem skalierbar und kann Anwendungen von Edge-Sensoren und Endpunkten bis hin zu CPU-Beschleunigern adressieren. Die Bausteine skalieren von acht KI-Engines, die weniger als 10 W Gesamtleistung benötigen, bis zu über 300 KI-Engines, die einen INT4-Durchsatz von mehr als 400 TOPS liefern; dazu kommen noch die adaptierbaren Engines und DSP-Engines.

- Autonom mithilfe von KI im Edge

- KI im Edge beschleunigen

- Beschleunigung der gesamten Anwendung