Verbindungsqualität von PCIe Gen 3 und 4

Margin-Tests effizienter gestalten

Fortsetzung des Artikels von Teil 1

Verifizierung der Link-Initialisierung

Bei den in diesem Zusammenhang verwendeten Prüfgeräten handelt es sich in der Regel um Bitfehlerraten-Tester (BERTs) und Oszilloskope. Diese Geräte werden ständig weiterentwickelt, um die Leistungsanforderungen jeder neuen Generation des PCIe-Standards zu erfüllen, und sind je nach Erfahrung des Benutzers oft relativ anspruchsvoll zu bedienen.

Die Verifizierungs- und Validierungskosten beziehen sich nicht nur auf die Anschaffungskosten der Hardware, sondern auch auf das Vollzeitäquivalent der Expertenressourcen, die für diese Tätigkeit eingesetzt werden. Ein Software-Assistent kann bei jeder Prüfung durch einen Testaufbau führen, um den ordnungsgemäßen elektrischen Anschluss an das zu prüfende Gerät zu gewährleisten, aber das gesamte Verfahren der Verwendung eines BERT und eines Oszilloskops mit Tastköpfen erfordert immer noch einen Experten, der den gesamten Prozess überwacht.

Jobangebote+ passend zum Thema

Verifizierung der Link-Initialisierung als Beispiel

Betrachten wir als Beispiel die sogenannte Link-Initialisierung, einen Kontrollprozess der physischen Schicht, der für die Initialisierung der physischen Schicht eines Geräts und die Anwendung einiger Einstellungen auf die Verbindung unerlässlich ist. Im Normalbetrieb läuft dieser Vorgang automatisch ab, aber wenn Sie an einer tiefgreifenden Designvalidierung interessiert sind, benötigen Sie Software, die spezifische Daten kodiert, damit die Benutzer potenzielle Probleme, die bei den Signalen während der Zustandsübergänge auftreten, diagnostizieren und überwachen können.

BERTs werden in der Regel für ein präzise gesteuertes Link-Training und eine Anpassung verwendet und decken die drei wichtigsten Testbereiche in diesem Wettbewerb ab: Konformität, Margin-Test und Fehlersuche. Außerdem werden Echtzeit-Oszilloskope benötigt, die eine hochentwickelte Anwendungssoftware erfordern, um komplexe Testverfahren auf der Empfängerseite zu automatisieren und gleichzeitig mit dem BERT zu kommunizieren, um Daten über die Einrichtungsparameter auszutauschen.

Ein Margin-Test erfordert auch, dass eine feste Liste von Schritten nacheinander auf jeder Lane des PCIe-Steckplatzes wiederholt wird, einschließlich der Einstellung der Triggerspannungszeit. Ein solch langwieriges und komplexes Verfahren, an dem verschiedene hochentwickelte Instrumente beteiligt sind, kann zu menschlichen Fehlern führen und die Effizienz des gesamten Überprüfungsprozesses beeinträchtigen.

Anstatt nach einem Ersatz für BERT/Scope-Systeme oder sogar für bereits verfügbare und weit verbreitete On-Chip-Lane-Margining-Tools zu suchen, wählte Tektronix bei der Kundenunterstützung einen anderen Ansatz. Der TMT4 Margin Tester basiert auf einem Intel-Stratix-10-FPGA und bietet branchenweit einzigartige Funktionen für die Bewertung des Link-Zustands in PCIe-Gen-3- und Gen-4-Geräten.

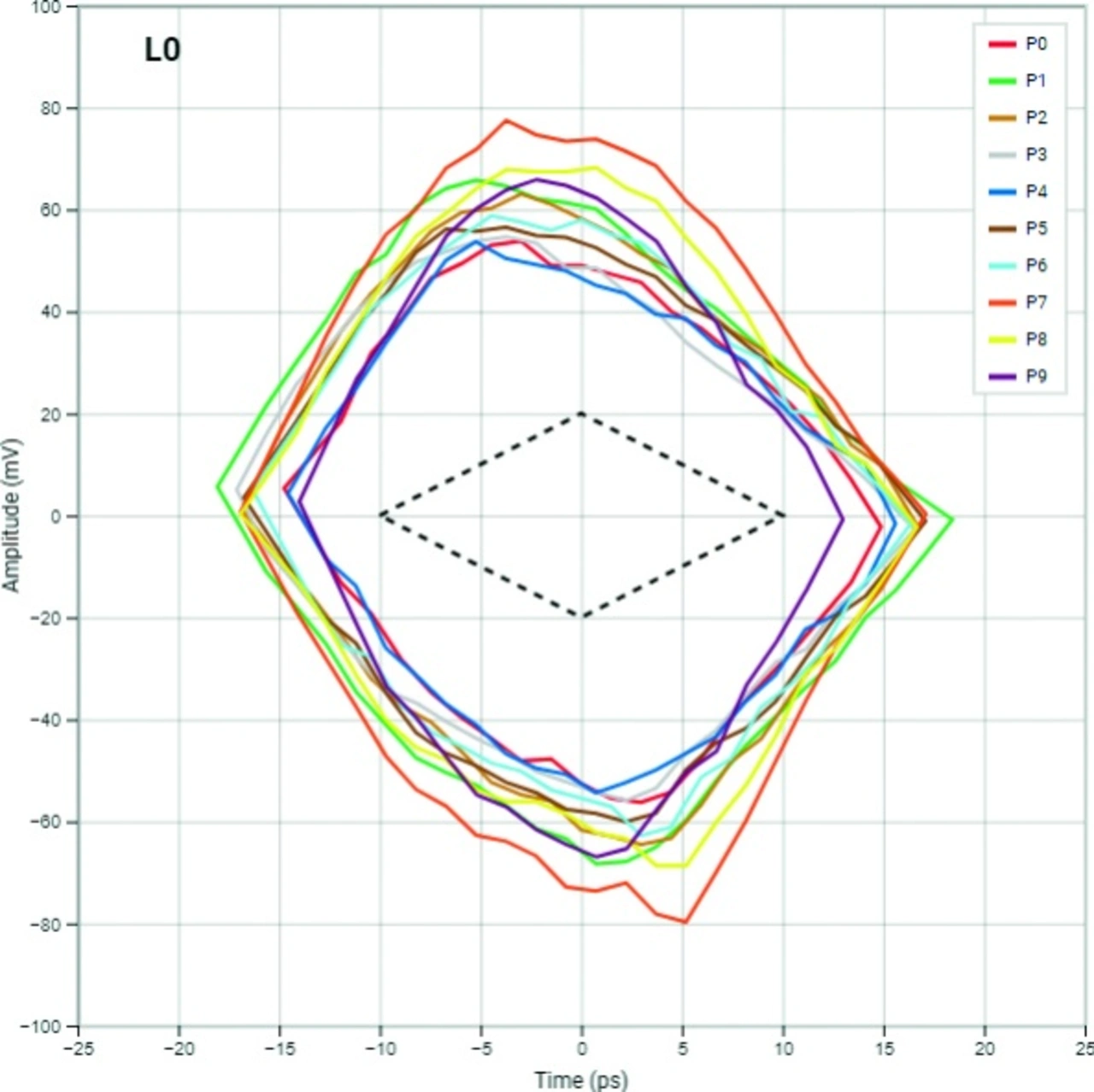

Der TMT4 Margin Tester lässt sich an die meisten gängigen PCIe-Formfaktoren wie CEM, M.2, U.2 und U.3 anschließen und ermöglicht so die Verbindung mit der Mehrzahl der heute verfügbaren PCIe-Geräte. Neben der Anzeige von Augendiagrammen bietet der Margin Tester einen Einblick in den Ausgleich, den seine Empfänger verwendet haben, um die Höhe und Breite des erzeugten Auges zu maximieren.

Es gibt zwei wichtige Daten, die das System für den Sendertest bereitstellt: Augendiagramme für jede Spur-Preset-Kombination, die am Empfänger des Margin-Testers gemessen werden. Die zugehörigen Empfänger-Trainingswerte des Margin-Testers werden verwendet, um das angezeigte Auge zu vergrößern.

Auf der Empfangsseite ist es möglich, eine funktionale Bewertung des Empfängerpfads des Prüflings vorzunehmen; es kann konkret ermittelt werden, wie weit die vom Margin-Tester übertragene Signalamplitude innerhalb eines erwarteten Betriebsbereichs verringert werden kann, bevor Fehler zurückgegeben werden.

So bewährt sich der neue TMT4 Margin Tester in dieser Applikation als zusätzliches Instrument, das sich speziell auf das Margining von Sende- und Empfangslanes konzentriert und es den Anwendern ermöglicht, den Zustand von PCIe Gen 3- und Gen 4-Geräten in nur wenigen Minuten zu erfassen.

- Margin-Tests effizienter gestalten

- Verifizierung der Link-Initialisierung