Dynamische Leistungsmodul-Vermessung

Das muss der Tastkopf können

Für eine aussagekräftige Bestimmung müssen Wide-Bandgap-Leistungsmodule (WBG) dynamisch charakterisiert werden – sowohl Low-Side als auch High-Side. Das bringt neue Herausforderungen für die Tastköpfe mit sich.

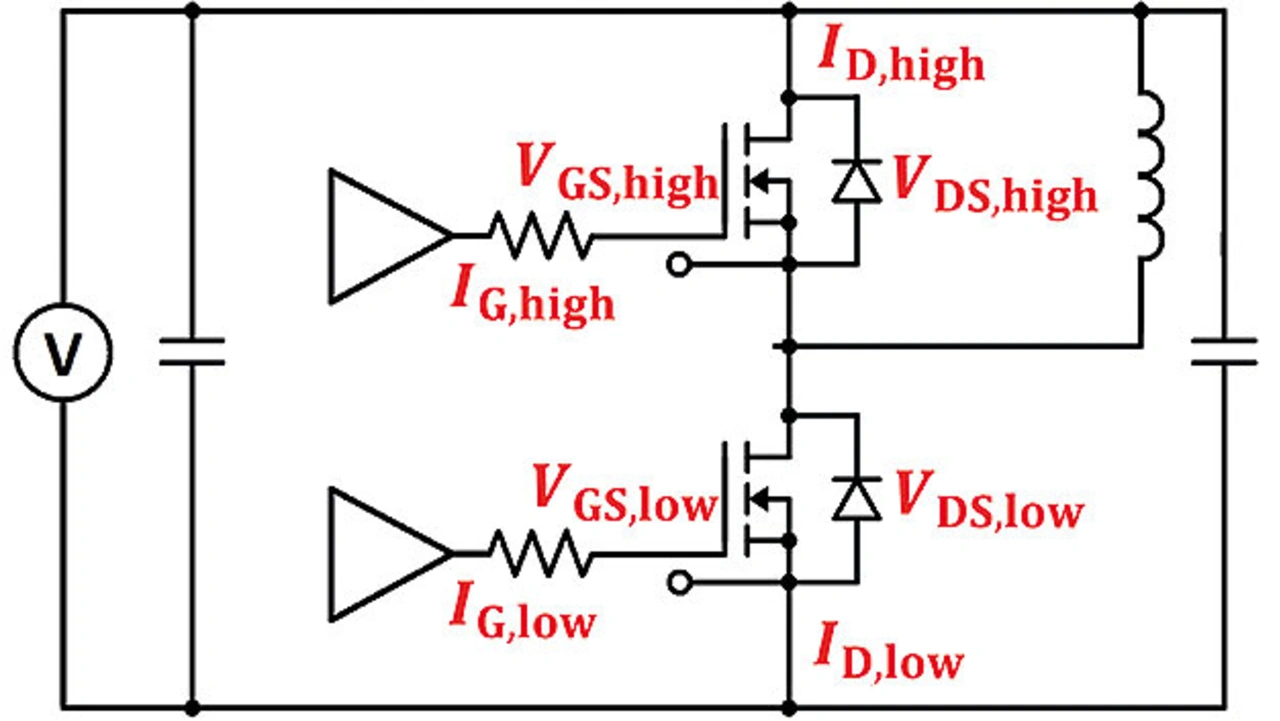

Zur Messung der dynamischen Eigenschaften von Leistungstransistoren oder Dioden wird ein dynamischer Analysator für Leistungsbauelemente, z. B. ein Doppelpulstest-System, verwendet. In einem solchen System müssen VDS, VGS, ID und IG, wie in Bild 1 dargestellt, mit einem Oszilloskop gemessen werden. Bei diskreten Bauelementen lasen sich die Messanforderungen vereinfachen, indem der Prüfling auf der Low-Side der Halbbrücke platziert wird. Dies führt zu relativ niedrigen CM-Signalen (Common Mode). ID kann direkt mit einem Shunt mit hoher Bandbreite gemessen werden.

Jobangebote+ passend zum Thema

Im Gegensatz zu diskreten Bauelementen enthalten Leistungsmodule in der Regel mindestens eine Halbbrücke. Sie ist nicht symmetrisch aufgebaut, was zu einem unterschiedlichen dynamischen Verhalten der Low-Side und der High-Side führt. Dies macht es erforderlich, VDS, VGS (und ID, IG) dynamisch für Low- und High-Side zu messen.

Es ist möglich, anstelle des Source-Potenzials des Low-Side-Transistors das Massepotenzial am Schaltknoten anzulegen, sodass die Anforderungen für die High-Side-Messung denen für die Low-Side-Messung entsprechen. Es ist jedoch vorteilhaft, beide Stufen gleichzeitig zu messen. Diese alternative Methode wird daher in diesem Artikel nicht behandelt.

Die Messung von High-Side-Signalen ist schwieriger als die von Low-Side-Signalen. Im nächsten Abschnitt werden die Anforderungen miteinander verglichen.

Anforderungen an die Tastköpfe

Die Anforderungen beziehen sich auf ein 1,7-kV-SiC-Modul, das bei maximal 80 % der Nennspannung (1,36 kV) mit Prüfströmen bis zu 1000 A geprüft wird.

Bandbreite (Bandwidth, BW)

Die Bandbreitenanforderungen an die Tastköpfe in Bezug auf die Übergangszeiten und das Ringing wurden bereits an anderer Stelle betrachtet. Ein Transistor mit einer Übergangszeit von 8 ns benötigt eine Bandbreite von 90 MHz. Für Ringing-Messungen mit einer typischen Schleifeninduktivität von 30 nH und einer Ausgangskapazität von 60 pF beträgt die erforderliche Bandbreite 120 MHz. Die erforderliche Bandbreite schließt Rogowski-Spulen und Pearson-Tastköpfe für Strommessungen aus.

Isolation

Die Isolationsanforderungen für Low- Side-Messungen sind nicht sehr streng. Der Shunt liegt normalerweise auf Massepotenzial. Daher treten bei der Messung eines 4-Pin-Transistors während der Schaltvorgänge Spannungsspitzen zwischen den Kelvin-Sense- und Source-Pins auf. VDS und VGS werden in Bezug auf den Kelvin-Sense gemessen, was eine gewisse Isolierung erfordert. Die Spannungsspitzen liegen typischerweise im Bereich von 10 V bis 50 V und können auf der Grundlage der Source-Induktivität LS und der Stromanstiegsgeschwindigkeit di/dt berechnet werden:

V = LS x di/dt

Die Isolationsanforderungen für High-Side-Messungen sind viel strenger. Während des Tests können sich die High-Side-Signale in der Nähe des Massepotenzials befinden, aber auch in der Nähe der Versorgungsspannung. In diesem Beispiel beträgt die Isolationsanforderung daher mindestens 1,36 kV. Hinsichtlich des Ringings ist eine Marge von 30 % angemessen. Daraus ergibt sich eine Isolationsanforderung von 1,8 kV für alle High-Side-Messungen. Höhere Werte sind für höhere Prüfspannungen erforderlich.

Gleichtaktbereich

Die CM-Anforderungen sind ähnlich wie die Isolationsanforderungen. Für Low-Side-Signale, mit Ausnahme von ID, liegt der CM-Transient typischerweise im Bereich von 10 V bis 50 V. High-Side-Signale lassen sich in Bezug auf den CM-Bereich in zwei Gruppen unterteilen. Die erste Gruppe besteht aus VDS und ID. Für diese Signale sind die Anforderungen nicht hoch, da diese Signale mit Bezug auf das Drain-Potenzial des High-Side-Transistors gemessen werden können. Ein gut designtes System hat eine große Bulk-Kapazität, wodurch die Versorgungsspannung sehr stabil ist. Kleine Änderungen, wie 5 % der Versorgungsspannung (68 V in diesem Beispiel), treten während des Pulses sehr langsam auf (z. B. innerhalb von 50 µs).

Die zweite Gruppe von High-Side- Signalen sind die Gate-Signale. Diese Signale sind auf den Kelvin-Sense- oder Source-Pin des High-Side-Transistors bezogen. Diese Pins befinden sich am Schaltknoten, sodass die Spannungsänderung ungefähr der Versorgungsspannung entspricht. Die Änderung ist während der Übergangszeit sehr schnell, zum Beispiel 1,36 kV innerhalb von 10 ns, was eine große Herausforderung für die Messqualität darstellt.

Gleichtaktunterdrückung

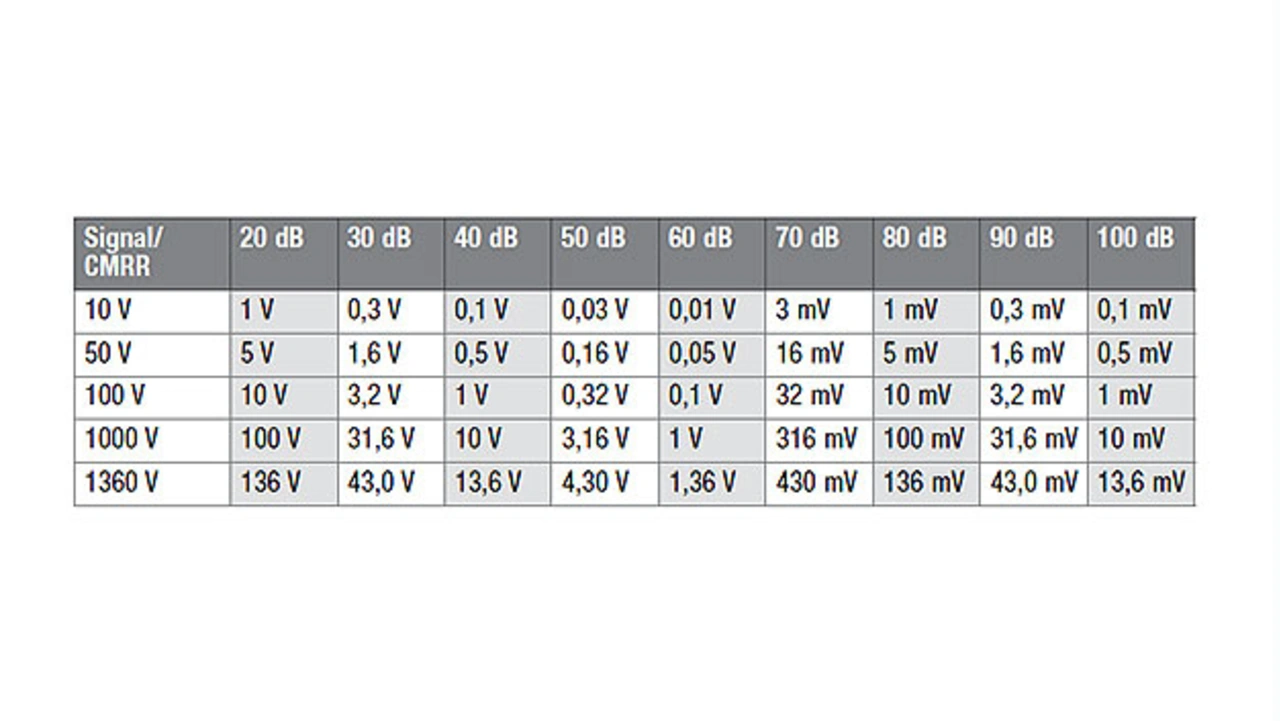

Bei einer Spannungsmessung sollte die Differenzspannung gemessen werden. Das CM-Signal führt jedoch ebenfalls zu einem störenden Messsignal. Die unerwünschten Spannungen aufgrund von CM-Signalen können sehr einfach für verschiedene Gleichtaktunterdrückungen (Common Mode Rejection Ratio, CMRR) berechnet werden, siehe Tabelle 1.

Es ist wichtig zu beachten, dass die CMRR von Tastköpfen stark von der Frequenz abhängt. Im Allgemeinen nimmt die CMRR mit der Frequenz ab. Die CMRR des Tastkopfs muss über den Frequenzbereich, in dem das CM eingeführt wird, hoch genug sein.

Wie bereits erwähnt, sind die CM- Spannungen der Low-Side-Signale klein (z. B. 50 V) und treten nur bei Schaltübergängen auf. Bei der Low-Side-ID-Messung mit Shunt wird kein CM eingebracht. Bei den anderen Signalen ist der durch CM gemessene Einfluss im Idealfall kleiner als die effektive Auflösung des Messsystems. Für Gate-Signale beträgt ein typischer Messbereich 40 V und bei einem Zielwert von 10 Bit würde die Auflösung 39 mV betragen. Die Tabelle zeigt, dass etwa 60 dB ausreichend sind. Bei VDS ist das gemessene Signal und damit der Bereich viel größer, z. B. 1,8 kV, was zu einer Auflösung von 1,76 V führt. Ein CMRR von 30 dB ist ausreichend. Bei beiden Low-Side-Signalen hat das CM-Signal hochfrequente Komponenten, sodass ein hoher CMRR über ein breites Frequenzspektrum erforderlich ist.

Bei High-Side-Signalen ist die Situation wiederum komplizierter. Für die erste Gruppe von Signalen, die auf das Drain-Potenzial bezogen werden können, ist das CM-Signal klein. Ein CMRR von 40 dB ist für VDS ausreichend. ID führt in der Regel nur zu sehr kleinen Spannungen, die mit dem Oszilloskop gemessen werden, etwa 500 mV bis 5 V. Daher sind die CMRR-Anforderungen strenger. Die Verwendung der gleichen effektiven Anzahl von Bits (Effective Number of Bits, ENOB) wie zuvor führt zu einer CMRR-Anforderung von 100 dB. Zu beachten ist, dass sowohl für VDS als auch für ID die CMRR-Anforderung nur für niedrigere Frequenzen wie 1 MHz gilt.

Die High-Side-Gate-Signale sind im Allgemeinen am schwierigsten zu messen, was die CMRR betrifft. In diesem Fall ist das CM die Versorgungsspannung mit hochfrequenten Komponenten und der Messbereich beträgt typischerweise nur 40 V. Daraus ergibt sich eine Auflösung von 36,5 mV und daher sind >90 dB ideal für einen breiten Frequenzbereich. Höhere CMRR-Werte als die genannten führen nicht zu einer höheren Messgenauigkeit.

Rauschen

Das Rauschverhalten ist der Schwachpunkt der meisten kommerziellen Tastköpfe mit hohem CMRR-Wert. Im Allgemeinen gilt: je geringer das Rauschen, desto besser. Dies gilt insbesondere für ID-Messungen, da die gemessene Spannung sehr klein ist. Der Shunt-Wert sollte so klein wie möglich gewählt werden, um den Einfluss der Schaltung zu minimieren, aber es gibt eine untere Grenze aufgrund des Rauschens. Einstellige mV-Effektivwerte sind gut. Für VDS ist Rauschen kein Problem, da übliche Hochspannungs-Differenzialtastköpfe verwendet werden können und die Rauschanforderungen gering sind. Gate-Signale liegen typischerweise dazwischen, mit einem typischen Messbereich von 40 V.

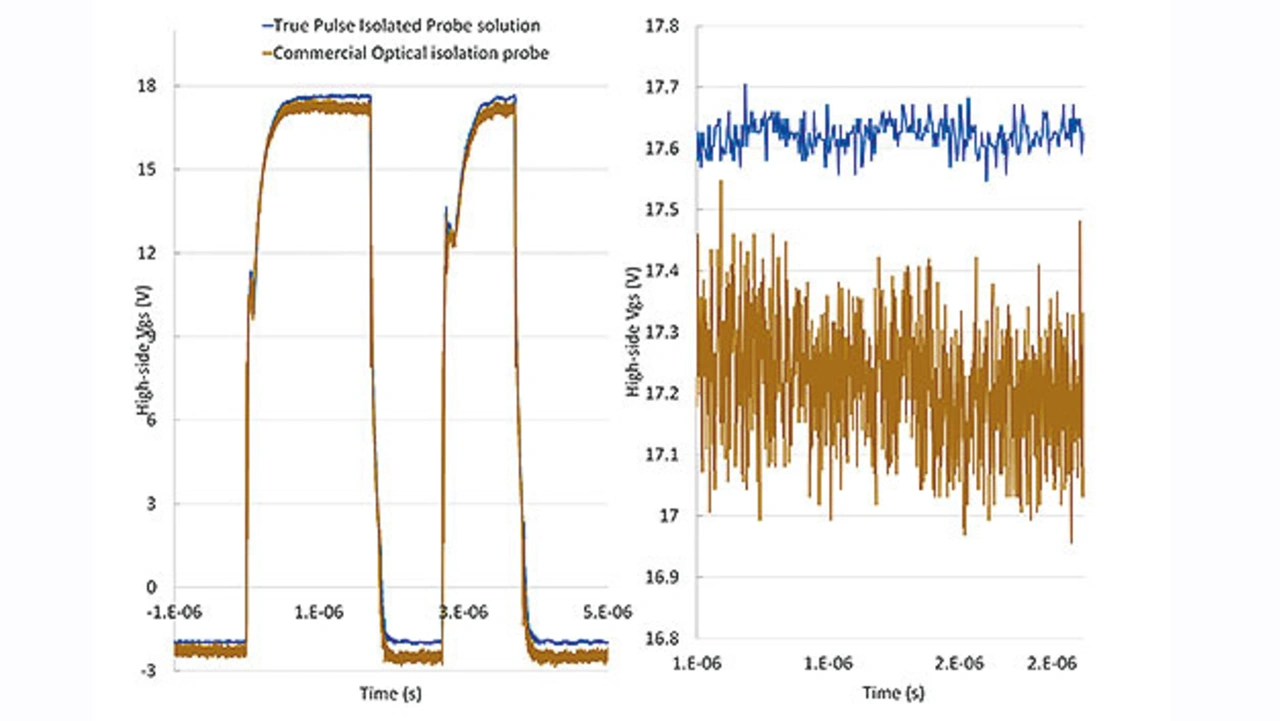

Ein wichtiger Parameter ist die 10-%-Gate-Spannungszeit, und bei 20 V VGS muss man in der Lage sein, 2 V sehr genau zu messen. Das Rauschen muss viel kleiner sein als die gemessene Spannung, <30 mVrms ist also ideal. Handelsübliche Tastköpfe mit hohem CMRR bringen für einen solchen Bereich ein Rauschen von etwa 200 mVrms mit sich, was das richtige Timing erschwert. Bild 2 zeigt den Vergleich des Rauschverhaltens zwischen einem handelsüblichen Tastkopf mit hohem CMRR-Wert und der rauscharmen High-CMRR-Lösung.

- Das muss der Tastkopf können

- Tastkopf-Belastung