Verbindungsqualität von PCIe Gen 3 und 4

Margin-Tests effizienter gestalten

Digitalschaltungen und -schnittstellen verhalten sich bei den immer höher getakteten Leitungen höchst analog. Neue Messverfahren und -geräte müssen her, um die Qualität der Schnittstellen in neuen Designs wie auch in Redesigns sicherzustellen. Hier setzt Tektronix mit seinem neuen Margin Tester an.

Von Andrea Vinci, Technical Marketing Manager EMEA bei Tektronix

Unterhaltungs- und Infotainment-Systeme in heutigen Fahrzeugen erfordern Funktionen, die nur mit neuen Hochgeschwindigkeits-Grafikkarten und ultraschneller Speicherintegration möglich sind. Unsere gesamte digitale soziale Interaktion wird aufgezeichnet und bereitgestellt durch große Computer-Racks, die Daten schnell von leistungsstarken Speicherlaufwerken abrufen und über Subsysteme zur Verarbeitung weiterleiten müssen.

Ständig werden zahlreiche Bilder aufgenommen und in hoher Auflösung gespeichert, die dann in verschiedenen Zusammenhängen an KI-Server weitergeleitet werden; hochentwickelte Algorithmen verarbeiten die Daten schnell und liefern hervorragende Ergebnisse.

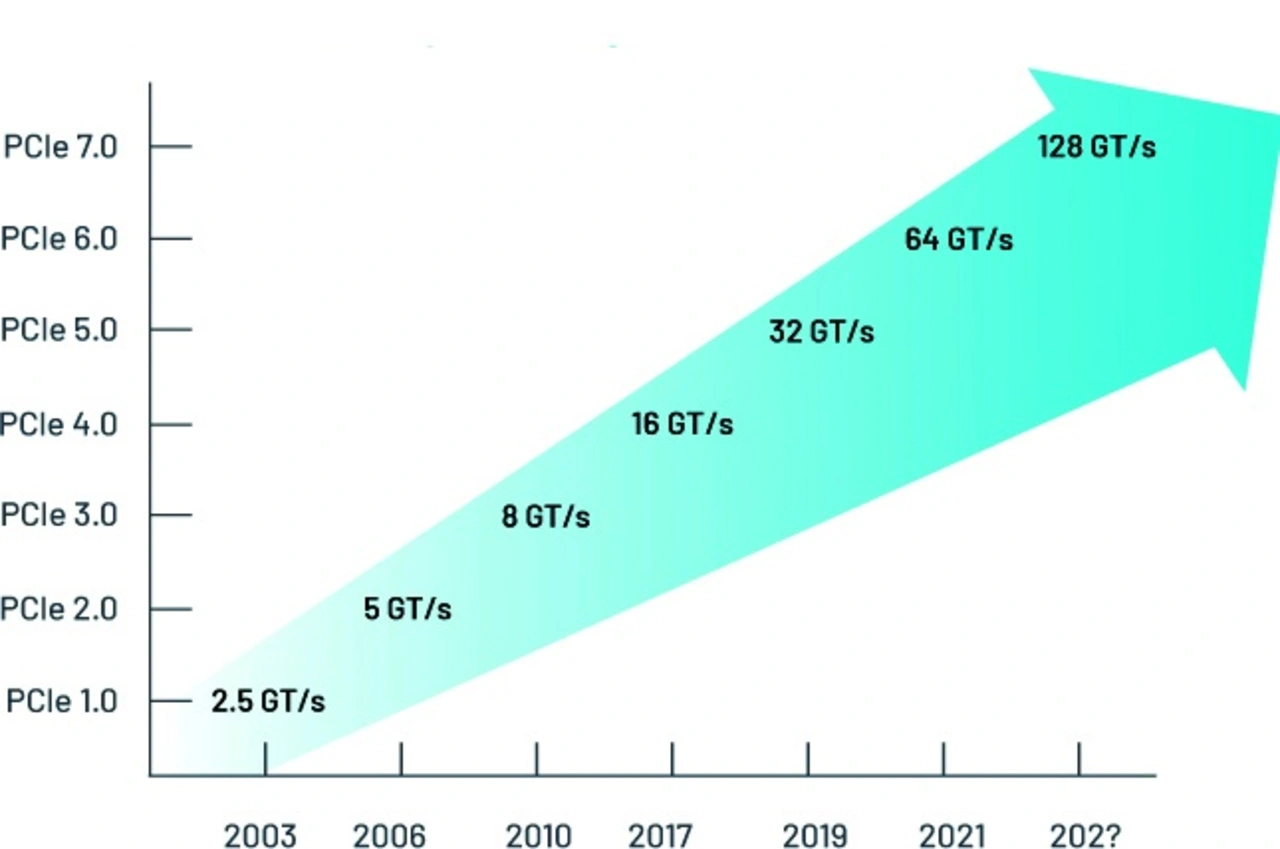

Ein typischer KI-Server unterscheidet sich nicht von anderen hochentwickelten Computersystemen: Er besteht aus einer Hauptplatine und mehreren anderen hochentwickelten Komponenten wie Grafikkarten, Festplatten und einer großen Anzahl von Switches, die miteinander verbunden sind. Die Standardverbindung für all diese Geräte basiert auf dem PCI-Express-Standard (PCIe). Der PCI-SIG-Standard hat Jahr für Jahr das ehrgeizige Ziel verfolgt, die Datenraten mit jeder neuen Generation des PCIe-Standards zu verdoppeln, seit die erste Generation im Jahr 2003 veröffentlicht wurde.

Herausforderungen digitaler Schaltungen

Der Umgang mit höheren Datenübertragungsraten führt jedoch dazu, dass die Entwicklung elektronischer Systeme eine schrittweise Weiterentwicklung erfordert, die viel Geschick und Geduld verlangt. Komplexe, miteinander verbundene Systeme von Hauptplatinen und Add-in-Karten müssen sorgfältig in kleinere Teilschaltungen zerlegt werden, die jeweils das Ziel einer späteren Verbesserungsphase werden, selbst nachdem das vollständige Design fertiggestellt ist.

PCIe Gen4 hat die vorherige Generation in verschiedenen Marktkontexten abgelöst, da der Bedarf an zusätzlicher Bandbreite gestiegen ist. Um dem gerecht zu werden, aktualisieren die Entwickler ständig ihre bewährten Methoden für das Design, tauschen gegenseitig Vorschläge und Richtlinien für das Routing von Leiterbahnen aus, minimieren den Crosstalk oder lösen EMI-Probleme, die durch falsch platzierte Vias verursacht werden.

Diese Entwickler sind oft Wegbereiter, und ihr stetiger Zwiespalt besteht darin, herauszufinden, wo und welche potenziellen Beeinträchtigungen von Signalen auftreten können und wie viele Kompromisse toleriert werden können. Ein einfacher Austausch eines Steckers gegen eine kostengünstigere Option, eine geringfügige Änderung der Pinbelegung aufgrund einer mechanischen Anforderung in letzter Minute oder einer Einschränkung in der Lieferkette, ein Firmware- oder Hardware-Upgrade oder eine Änderung des Produktionsprozesses können zum schlimmsten Alptraum werden, da der Aufwand für die Bewältigung dieser Probleme zu zusätzlicher Zeit für ein Redesign der Leiterplatte führt.

Jobangebote+ passend zum Thema

Die Anwendung eines BIOS-Updates auf einer Hauptplatine kann die Kommunikation mit NVMx-SSDs mit voller Geschwindigkeit freischalten; dies kann jedoch zu einer Änderung auf der elektrischen physischen Ebene führen. Während einer Firmware-Aktualisierung kann sich die Konfigurierung von Schaltern und Timern, die mit der Hauptplatine verbunden sind und mit der CPU kommunizieren, ändern; die Durchführung eines »Lane-Margin-Tests« nach Änderung dieser Bedingungen kann zu anderen Testergebnissen führen.

Verbesserungen der Jitter-Grenzwerte können jederzeit eintreten, und eine genaue Modellierung innerhalb komplexer Simulationswerkzeuge ist der Schlüssel zur Durchführung einer virtuellen Validierung, bevor die tatsächlichen Auswirkungen auf der physischen Schicht (PHY) des Siliziums festgestellt werden. Die Simulation ist jedoch nicht immer repräsentativ für die reale Implementierung, sodass Tests auf der physischen Ebene dennoch durchgeführt werden müssen.

Energiesparende Gen3- und Gen4-Konfigurationen werden häufig umgestaltet, um potenziell stromsparende Konfigurationen anzuwenden. Auch bei geringen Anpassungen der Stromversorgungsschaltungen sollte gewährleistet sein, dass die Einschaltphase schnell genug ist, um den Anforderungen an die Verbindungsaufbauzeit zu erfüllen, da schon eine Erhöhung um einige Millisekunden zu einem neuen zu überprüfenden Szenario führen kann.

In diesen Szenarien ist eine erneute Validierung des Designs jedoch möglicherweise nicht kosteneffizient: Tatsächlich würde eine geringfügige Designänderung an einem unkritischen, kostengünstigen Produkt, das in IoT-/Konsumentenanwendungen verkauft wird und noch immer PCIe-Gen3-Konnektivität verwendet, eine Zeitinvestition im Validierungstestlabor nicht rechtfertigen.

Die Unternehmen des Halbleiterdesigns haben komplexe Entscheidungswege zu beschreiten, um anhand von Erfahrungswerten eine Entscheidung über die Durchführung eines neuen Verifikations- und Validierungstestzyklus für eine Designänderung zu treffen. Diese Kriterien ergeben sich aus einer Risiko- und Kostenanalyse.

- Margin-Tests effizienter gestalten

- Verifizierung der Link-Initialisierung