ISSCC 2020

Chip-Innovation treibt KI-Revolution

Fortsetzung des Artikels von Teil 1

Spezielle Hardware für maschinelles Lernen

In den Jahren 2011 und 2012 baute ein kleines Team von Forschern und Systemingenieuren bei Google ein frühes, verteiltes System namens »DistBelief« auf, um ein paralleles, verteiltes Training von sehr großen neuronalen Netzen zu ermöglichen, wobei eine Kombination aus modell- und datenparallelem Training und asynchronen Aktualisierungen der Parameter des Modells durch viele verschiedene rechnergestützte Replikate verwendet wurde. Dies ermöglichte es, sehr viel größere neuronale Netze auf wesentlich größeren Datensätzen zu trainieren, und Mitte 2012 konnte das Team wir unter Verwendung von DistBelief als zugrundeliegendem Framework eine dramatisch bessere Genauigkeit für Spracherkennung und Bildklassifikationsmodelle feststellen. Der Einsatz dieser Modelle in anspruchsvollen Umgebungen von Systemen mit Hunderten von Millionen von Nutzern war jedoch eine weitere Frage, da die rechnerischen Anforderungen sehr hoch waren. Ein Teil der Hüllkurvenberechnung zeigte, dass für den Einsatz des tiefen neuronalen Netzwerksystems, das signifikante Verbesserungen der Wortfehlerrate für unser Hauptspracherkennungssystem mit CPU-basierten Rechengeräten aufwies, die Verdoppelung der Anzahl der Computer in den Google-Rechenzentren erforderlich wäre (mit einigen groben, aber plausiblen Annahmen über eine deutlich erhöhte Nutzung aufgrund von mehr Genauigkeit). Selbst wenn dies wirtschaftlich vernünftig wäre, würde es immer noch erhebliche Zeit benötigen, da erst die Infrastruktur dafür gebaut werden müsste. Diese Denkanstöße brachten das Team zum Grübeln über den Bau spezialisierter Hardware für neuronale Netze, zunächst für die Inferenz und später Systeme sowohl für Training als auch für Inferenz.

Warum spezialisierte Hardware für Deep-Learning-Modelle

Modelle für Deep Learning haben laut Dean drei Eigenschaften, die sie von vielen anderen Arten von allgemeineren Berechnungen unterscheiden. Erstens sind sie sehr tolerant gegenüber Berechnungen mit reduzierter Genauigkeit. Zweitens sind die von den meisten Modellen durchgeführten Berechnungen einfach unterschiedliche Zusammensetzungen einer relativ kleinen Handvoll von Operationen wie Matrix-Multiplikationen, Vektoroperationen, Anwendung von Faltungs-Kernels und linearer Algebra. Drittens sind viele der Mechanismen, die in den letzten 40 Jahren entwickelt wurden, um vielfältige Programme mit hoher Leistung auf modernen CPUs laufen zu lassen, wie z.B. Sprungvorhersagen, spekulative Ausführung, Hyperthreading-fähige Rechenkerne, tiefe Cache-Speicherhierarchien, und TLB-Subsysteme (Translation Look-aside Buffer) für maschinelle Lernberechnungen unnötig. Man kann also Rechen-Hardware bauen, die auf dichte lineare Algebra mit geringer Genauigkeit und nicht viel mehr spezialisiert ist, aber dennoch auf der Ebene der Spezifizierung von Programmen als unterschiedliche Zusammensetzungen von meist linearen algebraähnlichen Operationen programmierbar ist. Diese gemeinsamen Eigenschaften sind der Entwicklung spezialisierter digitaler Signalprozessoren (DSPs) für Telekommunikationsanwendungen ab den 1980er Jahren nicht unähnlich. Ein wesentlicher Unterschied ist jedoch die breite Anwendbarkeit von Deep Learning auf riesige Wolken von Rechenproblemen in unterschiedlichsten Gebieten und Arbeitsfeldern. Diese Hardware lässt sich trotz der geringen Anzahl an unterstützten Operationen für eine breite Vielfalt wichtiger Berechnungeneinsetzen, statt der eher eng bemessenen Fähigkeiten von DSPs. Auf der Grundlage unseres Gedankenexperiments über die dramatisch gestiegenen Rechenanforderungen von tiefen neuronalen Netzen (DNNs) für einige typischer hochvolumiger Inferenzanwendungen wie Spracherkennung und Bildklassifikation, fiel bei Google die Entscheidung, eine Reihe von Beschleunigern zu entwickeln, die als »Tensor Processing Units« (TPU) bezeichnet werden und sowohl Deep-Learning-Inferenz (Schlussfolgerung) und -Training beschleunigen sollen. Das erste derartige System, genannt TPUv1 (2017), war ein Ein-Chip-Design, das auf die Inferenzbeschleunigung abzielte.

Für die Inferenz haben sich (nachdem ein Modell trainiert wurde und das bereits trainierte Modell auf Basis neuer Eingaben Vorhersagen zu treffen hat) 8-bit-Integer-Berechnungen bei vielen wichtigen Modelle als ausreichend herausgestellt, wobei in der Forschungsgemeinschaft weiter daran gearbeitet wird, diese Grenze mit Ansätzen wie Gewichtungen mit noch geringerer Genauigkeit und Techniken zur Einsparung von Gewichtungen und/oder Aktivierungen weiter zu verschieben. Das Herzstück des TPUv1 ist eine 65.536 8-bit-MAC-Matrix-Multiplikationseinheit, die einen Spitzendurchsatz von 92 TeraOps/Sekunde (TOPS) bietet. Die TPUv1 ist im Durchschnitt etwa 15 bis 30 mal schneller als eine aktuelle GPU oder CPU, bezüglich TOPS/Watt etwa 30 bis 80 mal besser, und war damit in der Lage, neuronale Netze in der Produktion so auszuführen, dass diese etwa 95 % des damaligen Bedarfs an neuronalen Netz-Inferenzen in Google-Rechenzentren mit erheblichen Kosten- und Leistungsvorteilen erfüllten.

Inferenz-Funktionen spielen auch auf mobilen Geräten mit niedriger Leistungsaufnahme in vielen Anwendungen des maschinellen Lernens eine unglaublich wichtige Rolle. Die Möglichkeit, Modelle des maschinellen Lernens auf dem Gerät auszuführen, wo die Geräte selbst oft die Quelle der Rohdateneingaben in Form von Sprache oder Bildern sind, kann erhebliche Vorteile hinsichtlich der Latenzzeit und der Privatsphäre bringen. Die gleichen Konstruktionsprinzipien wie bei der TPUv1 (ein einfaches Design, das auf lineare Algebra mit niedriger Genauigkeit bei hoher Leistung/Watt abzielt) lassen sich auch in Umgebungen mit wesentlich geringerem Energiebudget wie bei Mobiltelefonen anwenden. Googles Edge TPU ist ein Beispiel für ein solches System, das 4 TOps in einem 2-W-Leistungsbudget bietet (https://cloud.google.com/edge-tpu/). Die geräteinterne Berechnung ist entscheidend in vielen interessanten Anwendungsfällen des Deep Learning, in der Bild- und Sprachverarbeitung sowie anderen Arten von Modellen, die direkt Sensorsignale verarbeiten können und ohne Netzanbindung auskommen müssen. Ein typisches Beispiel sind Landwirtschaftsanwendungen, wie die Identifizierung von Krankheiten in Pflanzen.

Mit der weit verbreiteten Einführung des maschinellen Lernens und seiner wachsenden Bedeutung als einer Schlüssel-Rechenart, findet nun gleichsam eine kambrische Explosion mit neuen und interessanten Beschleunigerarchitekturen für das maschinelle Lernen statt. Dort sind mehr als 20 Venture-unterstützte Startup-Unternehmen sowie eine Vielzahl großer, etablierter Unternehmen unterwegs, die verschiedene neue Chips und Systeme für maschinelles Lernen herstellen. Einige Start-ups, wie z.B. Cerebras (www.cerebras.net), Graphcore (www.graphcore.ai) , und Nervana (von Intel übernommen) (www.intel.ai/nervana-nnp) konzentrieren sich auf eine Vielzahl von Designs für das ML-Training. Andere, wie z.B. als Alibaba (www.alibabacloud.com/blog/alibaba-unveils-ai-chip-to-enhancecloud- computing-power_595409) entwerfen Chips, die auf Inferenz ausgerichtet sind.

Einige der Entwürfe verzichten auf DRAM oder HBM mit größerer Speicherkapazität und konzentrieren sich auf sehr leistungsstarke Designs von Modellen, die klein genug sind, dass ihr gesamter Satz von Parametern und Zwischenwerten in das SRAM passen. Andere konzentrieren sich auf Designs die DRAM oder HBM umfassen, die sie für größere Modelle geeignet machen. Einige Firmen, wie Cerebras, erforschen die vollständige Integration im Wafer-Maßstab. Andere, wie zum Beispiel Googles Edge TPUs setzen auf Chips mit sehr geringer Leistungsaufnahme für Inferenz-Funktionen in Umgebungen wie Mobiltelefonen und verteilter Sensorik.

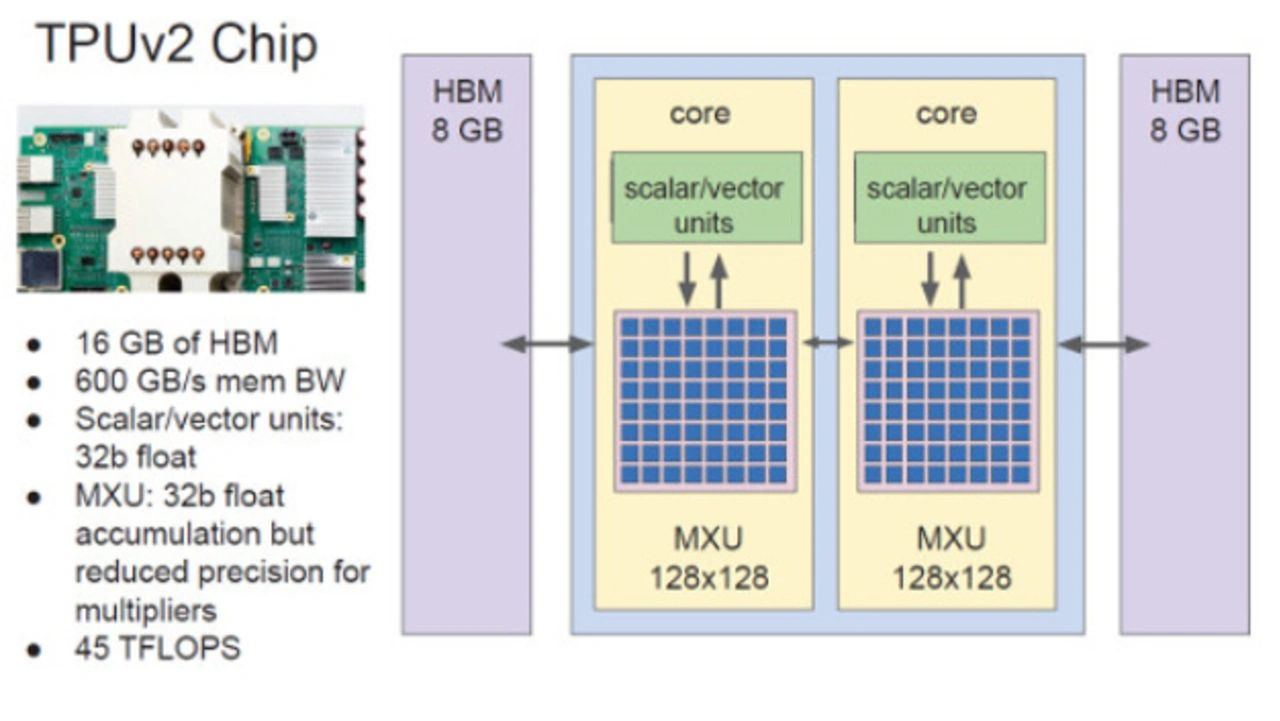

Die Entwicklung maßgeschneiderter Hardware für maschinelles Lernen für das Training (und nicht nur Inferenz) ist ein komplexeres Unterfangen als Single-Chip-Inferenzbeschleuniger. Der Grund dafür ist, dass Ein-Chip-Systeme für das Training nicht in der Lage sind, viele Probleme, in angemessenen Zeiträumen (z.B. Stunden oder Tage) zu lösen, statt Wochen oder Monaten. Denn ein Ein-Chip-System kann keine ausreichende Rechenleistung liefern. Darüber hinaus möchte man für größere Datensätze größere Modelle trainieren. Selbst wenn ein einziger Chip genug Rechenleistung für ein gegebenen Problem liefern könnte, um es in einer angemessenen Zeit zu lösen, dann führt das nur dazu, dass wir meistens noch größere Probleme lösen wollen (und dabei sind wir auf den Einsatz von mehreren Chips in einem parallelen oder verteilten System ohnehin angewiesen). Deshalb geht es beim Entwurf von Trainingssystemen in Wirklichkeit um den Entwurf größerer, ganzheitlicher Computersysteme. Dies erfordert ein Nachdenken über den Entwurf individueller Beschleuniger-Chips und Hochleistungs-Verbindungen für eng gekoppelte ML-Supercomputer. Googles TPUs der zweiten und dritten Generation, TPUv2 und TPUv3 (https://cloud.google.com/tpu/), sind so konzipiert, dass sie sowohl das Training als auch das Ziehen von Schlussfolgerungen (Inferenz) unterstützen. Die Basiskonfiguration besteht aus jeweils vier Chips, die so konzipiert wurden, dass sie zu größeren Konfigurationen, den sogenannten »Pods«, zusammengeschaltet werden können. Bild 4 zeigt die Blockschaltung eines einzelnen Google TPUv2-Chips mit zwei Kernen, wobei die Hauptrechenkapazität in jedem Kern durch eine große Matrix-Multiplikationseinheit (MXU) dargestellt ist, die die Ergebnisse der Multiplikation eines Paares von 128×128-Matrizen in jedem Zyklus liefern kann. Jeder Chip verfügt über 16 GB (TPUv2) oder 32 GB (TPUv3) HBM (High-Bandwidth Memory). Bild 5 zeigt Googles TPUv3 Pod mit 1024 Beschleuniger-Chips, bestehend aus acht Racks von Chips und zugehörigen Servern, wobei die Chips in einem ringförmigen 32×32 Mesh angeordnet sind, die eine Spitzenleistung des Systems von mehr als 100 Petaflop/s erlaubt.

Jobangebote+ passend zum Thema

Numerische Formate niedriger Genauigkeit für ML

Die TPUv2 und die TPUv3 (Bild 6) verwenden ein benutzerdefiniertes Gleitkomma-Format namens »bfloat16«, das vom IEEE Halbpräzisions-16-bit-Format abweicht. Bei Google wollte man ein Format, das für maschinelles Lernen nützlicher ist und auch kostengünstigere Multiplikatorschaltungen ermöglicht. bfloat16 wurde ursprünglich entwickelt als verlustbehaftete Kompressionstechnik zur Reduzierung der Bandbreitenanforderungen während der Netzwerkkommunikation von Gewichten und Aktivierungen des maschinellen Lernens im »DistBelief«-System. Das Gleitkomma-Format war das Arbeitspferd in den ML-Prozessoren TPUv2 und TPUv3 seit 2015. Im Dezember 2018 kündigte Intel Pläne an, das bfloat16-Format in zukünftigen Generationen von Intel-Prozessoren zu unterstützen.

Es stellte sich heraus, dass die in den Deep-Learning-Modellen des maschinellen Lernens verwendeten Berechnungen sich mehr für den Dynamikbereich als für die Genauigkeit interessieren. Außerdem ist der Aufwand (APC – Area Power Cost) für Multiplizierschaltungen für ein Gleitkomma-Format mit M Mantissenbits ein Feld von (M +1) × (M +1) von Volladdierern (die für die Multiplikation der Mantissenanteile der beiden Eingangszahlen benötigt werden). Die Formate IEEE fp32, IEEE fp16 und bfloat16 benötigen jeweils 576 Volladdierer, 121 Volladdierer und 64 Volladdierer. Da die Multiplizierer für das bfloat16-Format so viel weniger Schaltungsaufwand erfordern, ist es möglich, mehr Multiplizierer auf die gleiche Chipfläche zu bringen und mit dem gleichen Leistungsbudget auszukommen, was bedeutet, dass ML-Beschleuniger, die dieses Format verwenden, auf mehr Flops/Sek und Flops/Watt kommen, wobei alle anderen Parameter gleich bleiben. Darstellungen mit geringerer Präzision verringern auch die Bandbreite und die Energie, die für das Verschieben von Daten zum und vom Speicher oder für das Senden von Daten über Verbindungsstrukturen erforderlich sind, was zu weiteren Effizienzsteigerungen führt.

Die Herausforderung von Unsicherheit auf einem schnell fortschreitenden Gebiet

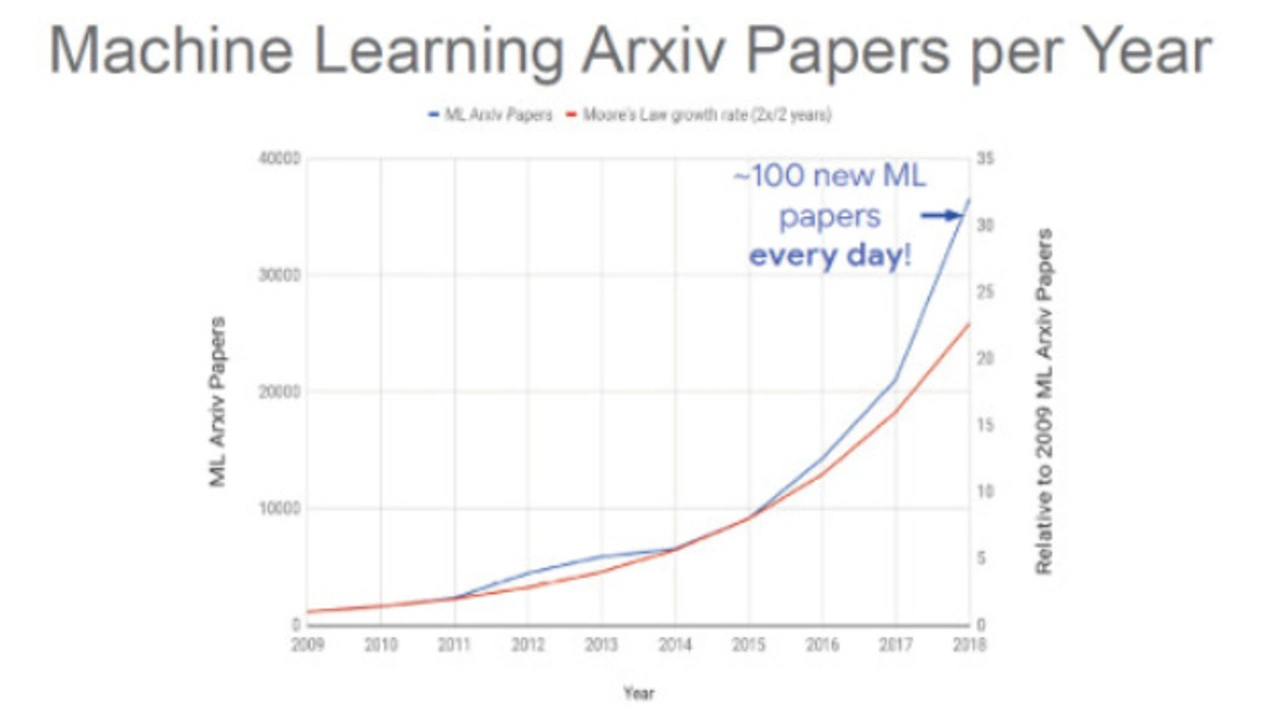

Eine Herausforderung für die Entwicklung von ML-Beschleunigers ist, dass sich das Forschungsgebiet des maschinellen Lernens (ML) extrem schnell entwickelt (wie das Wachstum und die absolute Anzahl der jährlich veröffentlichten Forschungsarbeiten in Bild 3 zeigt). Chip-Design-Projekte, die heute begonnen werden, benötigen oft 18 bis 24 Monate, um das Design fertigzustellen, die Halbleiterchips herzustellen, sie zurückzuholen und in einer Produktionsumgebung des Rechenzentrums zu installieren. Damit diese Teile wirtschaftlich rentabel sind, müssen sie in der Regel eine Lebensdauer von mindestens drei Jahren haben. Die Herausforderung für Computerarchitekten, die ML-Hardware bauen, besteht also darin, vorherzusagen, wo sich das maschinelle Lernen im Zeitrahmen von 2 bis 5 Jahren hin entwickeln wird. Googles Erfahrung ist, dass das Zusammenbringen von Computerarchitekten, übergeordneten Softwaresystemherstellern und Forschern auf dem Gebiet des maschinellen Lernens, um gemeinsam entwurfsbezogene Themen zu erörtern, wie z.B. »Was könnte in der Hardware in diesem Zeitrahmen möglich sein?« und »Welche interessanten Forschungstrends zeichnen sich ab und welche Auswirkungen hätten sie auf die ML-Hardware?« einen nützlichen Weg dorthin darstellen.

- Chip-Innovation treibt KI-Revolution

- Spezielle Hardware für maschinelles Lernen

- Maschinelles Lernen für den Schaltungsentwurf und in der Halbleiterfertigung

- Gesucht: Das universell einsetzbare ML-System der Zukunft