Leistungs-MOSFETs im Linearbetrieb

Sicherer Arbeitsbereich ausgeweitet

Im Linearbetrieb werden Leistungs-MOSFETs thermisch stark belastet. Neue Komponenten besitzen durch eine für solche Betriebsarten optimierte Transistorzelle, die spezielle Aufbau- und Verbindungstechnik sowie das angepasste Gehäuse einen größeren sicheren Arbeitsbereich.

Im linearen Bereich arbeiten Leistungs-MOSFETs meist als spannungsgesteuerte Widerstände. Darunter fallen Sicherheitstrennschalter für Batterien und Stromverteiler, Einschaltstrombegrenzer, elektronische Leitungsschutzschalter, linear betriebene Motorregler oder Lastschalter sowie Hot-Swap-Applikationen. Grund dafür sind ihre Vorteile in Bezug auf die elektromagnetischen Interferenzen (EMI) und die Gesamtsystemkosten.

Allerdings sehen sich diese Bauelemente mit hohen Drain-Strömen, Drain-Source-Spannungen und Leistungen konfrontiert. Abgesehen davon müssen die Bauelemente nicht nur einige technologische Anforderungen zur Steigerung der Robustheit erfüllen, sondern auch hinsichtlich des Wärmemanagements gewisse Restriktionen einhalten, damit ein thermisches Durchgehen ausgeschlossen werden kann.

STMicroelectronics (ST) hat mit dem STH200N10WF7-2 einen neuen Leistungs-MOSFET mit 100 V Nennspannung vorgestellt, der auf der STripFET-F7-Technologie beruht und ein Gehäuse der Bauform H²PAK besitzt. Die Entwickler haben die STripFET-F7-Technologie in Bezug auf die Gate-Source-Spannung UGS optimiert abgestimmt. Dies verhindert, dass auf dem Chip lokale Hot-Spots mit hoher Stromdichte entstehen, und die Schwellenspannung UGS(th) sowie die Transkonduktanz Gfs lassen sich so einstellen, dass sich der Chip weniger erwärmt. Dank dieser Maßnahmen ist der MOSFET in einem weiteren Bereich von Betriebsbedingungen thermisch stabil, sodass der sichere Arbeitsbereich (Safe Operating Area, SOA) entsprechend größer wird.

Jobangebote+ passend zum Thema

Robustes Verhalten im Linearbetrieb

Robustes Verhalten im Linearbetrieb . Bilder 1-4

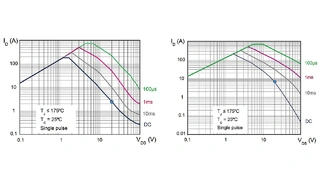

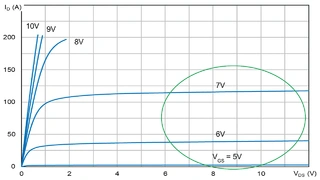

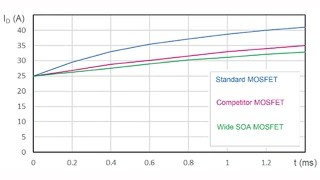

Während ein Standard-Trench-MOSFET bei 20 V bei einer Impulsdauer von 10 ms einen Strom von 2,5 A leiten kann, lässt der neue Wide-SOA-Baustein STH200N10WF7-2 unter gleichen Bedingungen bis zu 6,5 A zu (Bild 1). Dies ist das Ergebnis einer Technologieoptimierung, bei der selbst bei hohen Werten der Drain-Source-Spannung UDS die Stromkennlinien nahezu flach verlaufen (Bild 2) und sich die Strombegrenzung über die Zeit selbstständig ausgleicht (Bild 3) [1].

Wegen der design- und optimierungsbedingten Abstriche ist die Stromverstärkung beim STH200N10WF7-2 bei niedrigeren Gate-Source-Spannungen UGS geringer, um den Stromanstieg zu begrenzen und einem thermischen Durchgehen im linearen Betrieb vorzubeugen. Dagegen ist die Stromverstärkung bei größeren Werten von UGS höher, um den Einschaltwiderstand RDS(on) im Schaltbetrieb zu verringern (Bild 4). Dank dieser Eigenschaft lässt sich der Wide-SOA-Baustein im PWM-Modus (Pulse Width Modulation) betreiben, nachdem er nach dem Einschalten im linearen Modus den Einschaltstrom begrenzt hat.

Performance-Werte im Linearbetrieb

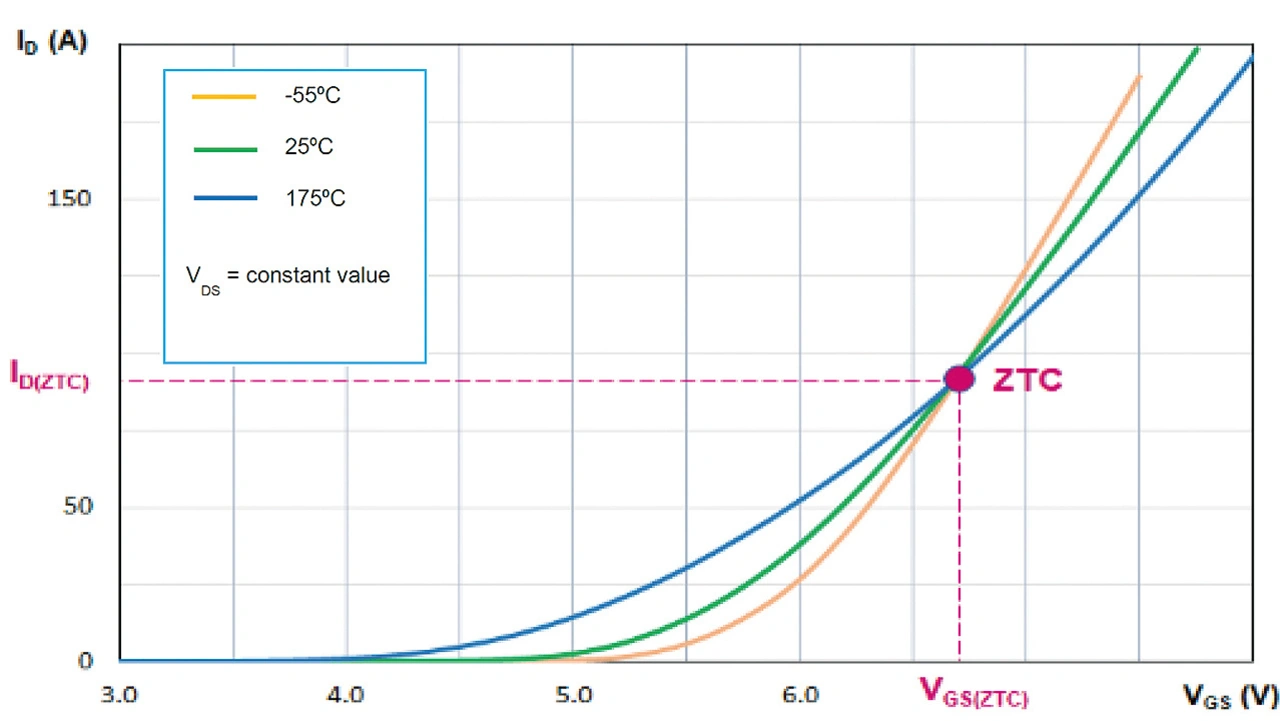

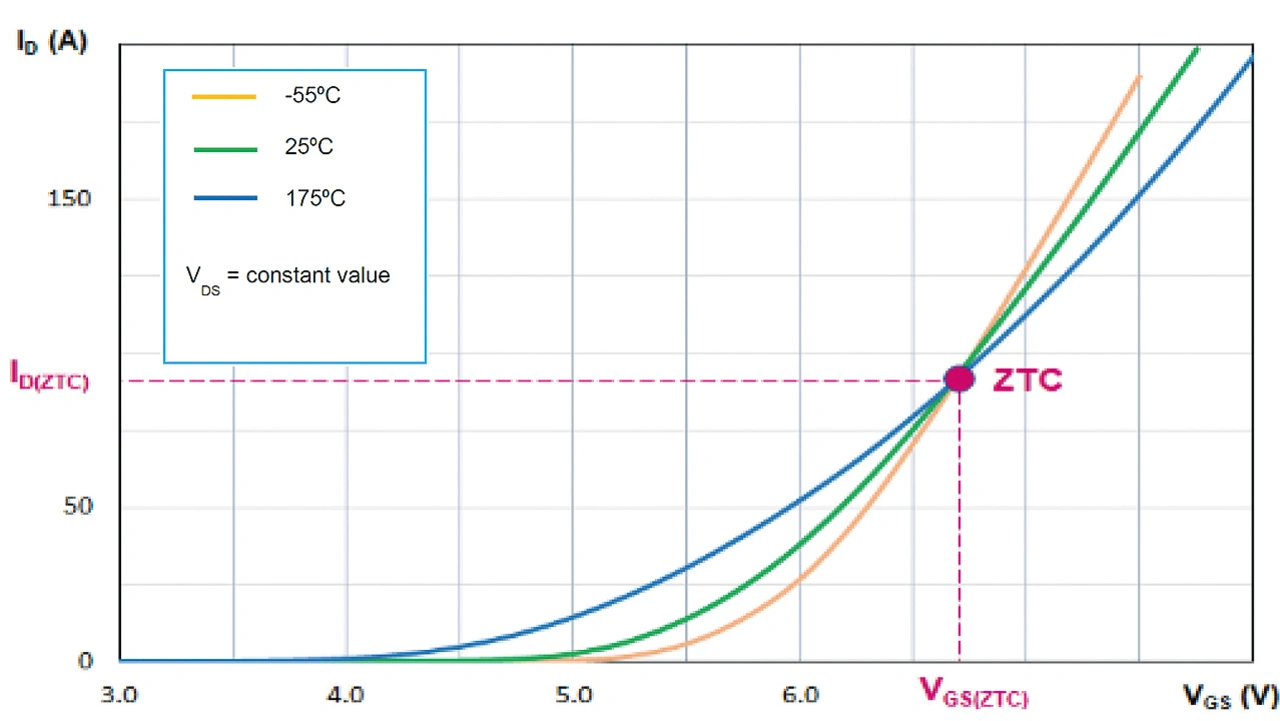

Die wichtigste Kennzahl, an der sich die Leistungsfähigkeit im linearen Betrieb ablesen lässt, ist der Temperaturkoeffizient (TC) des Drain-Stroms ID. Dieser Koeffizient kennzeichnet die Fähigkeit des Bausteins, seinen Strom bei hohen Temperaturen und Spannungen eigenständig auszugleichen. Es handelt sich hierbei um einen technologieabhängigen Parameter, der mit der Übertragungskennlinie des MOSFETs und ihrer Temperaturabhängigkeit zusammenhängt (Bild 5). Der Schnittpunkt der drei Übertragungskennlinien heißt ZTC (Zero Temperature Coefficient):

- Bei UGS = UGS(ZTC) bleibt der Strom über die Temperatur stabil.

- Bei UGS > UGS(ZTC) hat der Drain-Strom mit steigender Temperatur fallende Tendenz, was ihn thermisch stabil macht.

Umgekehrt gilt bei UGS < UGS(ZTC), dass der Strom wegen der geringeren Schwellenspannung, deren Temperaturkoeffizient negatives Vorzeichen hat, mit zunehmender Erwärmung des Bauelements immer weiter zunimmt. Dies bewirkt, dass der Baustein thermisch durchgeht und der Die zerstört wird, sofern keine geeigneten Gegenmaßnahmen getroffen werden [1].

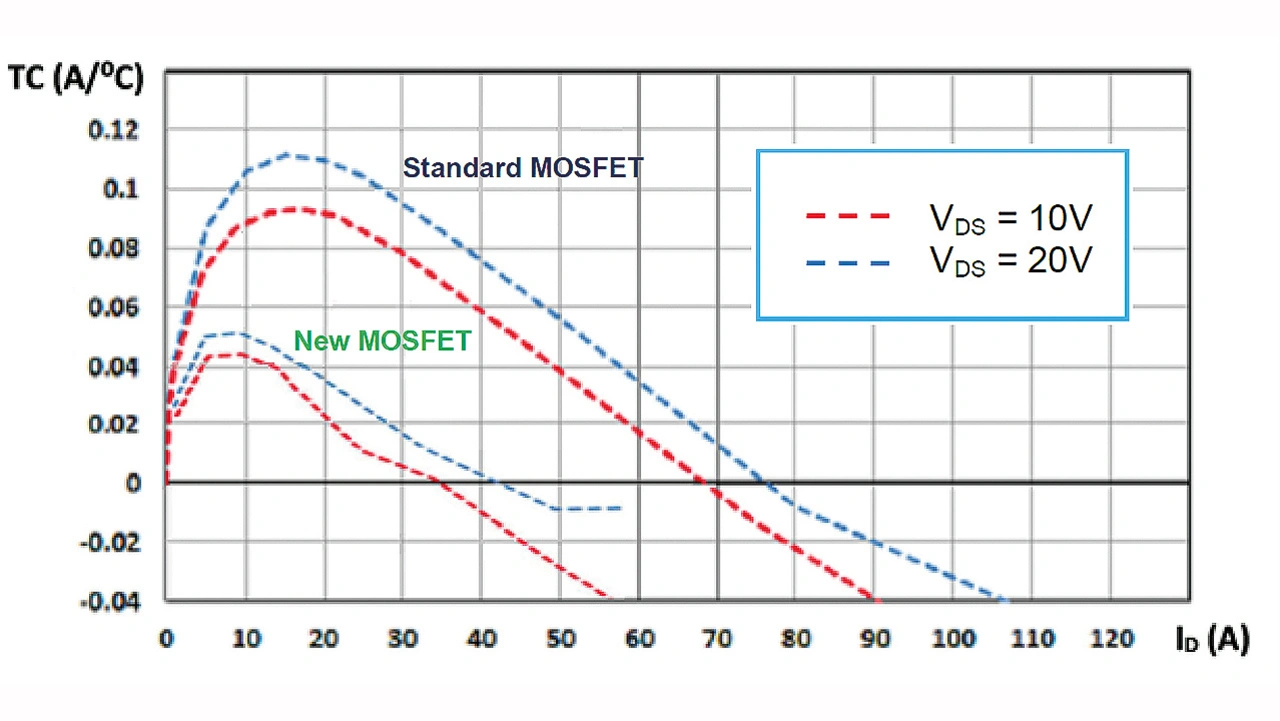

Ein Vergleich der Temperaturkoeffizienten eines herkömmlichen STripFET-F7-MOSFETs und des neuen Wide-SOA-Bausteins STH200N10WF7-2 ist in Bild 6 zu sehen. Ist der TC null oder hat er negatives Vorzeichen, nimmt der Drain-Strom mit steigender Temperatur ab, sodass der Baustein thermisch stabil ist. Allerdings lässt sich der Baustein auch bei positivem TC betreiben, ohne auszufallen. Ob das möglich ist, hängt von der Wärmekapazität des gesamten Chips und damit der Fähigkeit ab, die pro Flächeneinheit anfallende Wärme abzuleiten. Wenn die über die Zeit erzeugte Wärme vollständig vom Baustein selbst aufgenommen werden kann, befindet sich der Leistungs- MOSFET folglich in einem sicheren Arbeitsbereich [2].

Der Bereich mit niedrigen Werten von ID und hohen Werten von UDS ist im linearen Betrieb die unsicherste Zone der SOA, denn in der Region mit niedrigen ID-Werten weisen Leistungs-MOSFETs in der Regel den höchsten positiven TC auf. Nimmt hier die Drain-Source-Spannung zu, steigen sowohl die Leistung als auch die Wärmeentwicklung signifikant an [2]. Bei gegebener TC-Kurve wird der betreffende Baustein dann bei hohen Werten von UDS potenziell instabiler. Die Bedingung für thermische Instabilität lässt sich wie folgt ausdrücken:

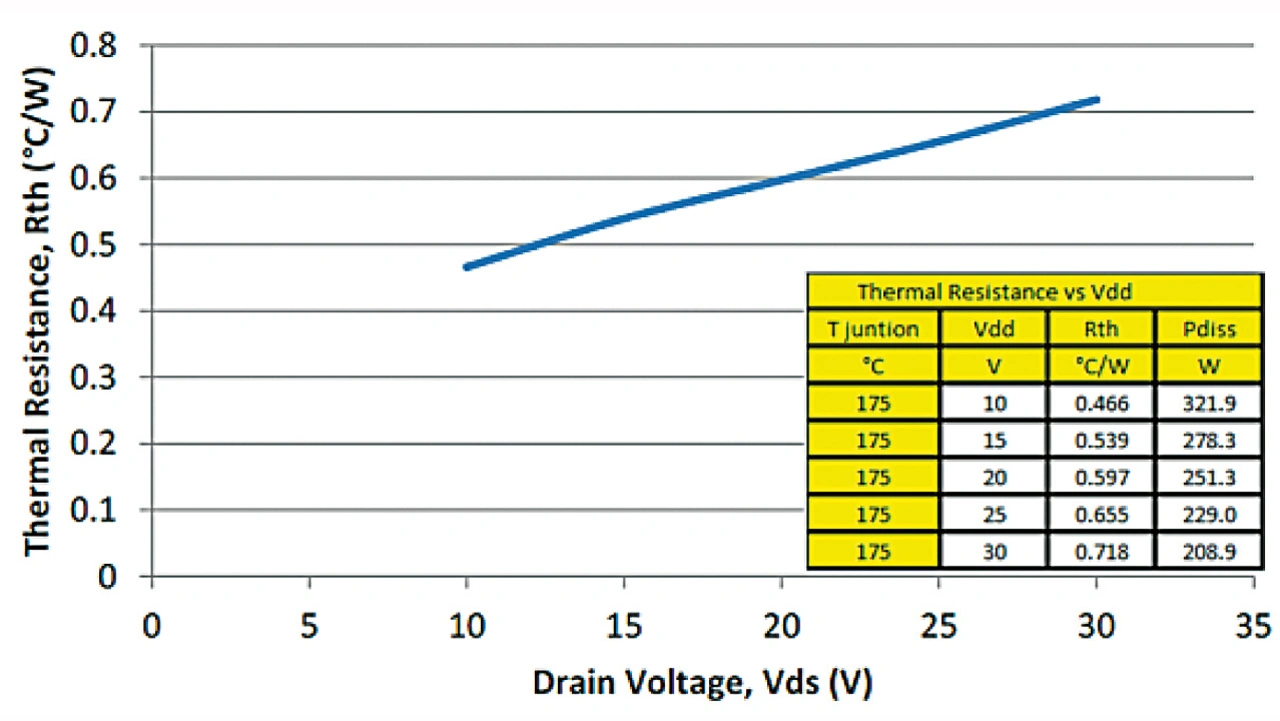

Darin steht TC für den Temperaturkoeffizienten und Rth für den Wärmewiderstand. Wie sich die Temperatur auf dem Chip bei verschiedenen Werten von UDS verteilt, ist in Bild 7 zu sehen. Mit zunehmender Drain-Source-Spannung verteilt sich die Temperatur auf dem Chip inhomogener, wobei sich die Wärme auf eine sehr kleine Fläche konzentriert. Durch diese lokal begrenzte Erwärmung sinkt die Gate-Source-Schwellenspannung UGS(th) in diesen Chipbereichen, was zusammen mit dem Anstieg des Drain-Stroms noch mehr Wärme generiert und der Wert von UGS(th) weiter sinkt.

Im Ergebnis geht der Baustein thermisch durch und fällt anschließend aus. Bei einer Zunahme von UDS lässt die Konzentration des Stroms auf einen kleinen Bereich und die daraus resultierende Verkleinerung der aktiven Fläche den Wärmewiderstand ansteigen, was wiederum die elektrische Leistung reduziert, die der Baustein sicher verarbeiten kann (Bild 8).

Der thermische Widerstand Rth des Halbleitergehäuses ist ein Maß für die Fähigkeit des Materials, Wärme von der Sperrschicht (bzw. dem Chip) an die Umgebung oder die Leiterplatte abzuleiten. Je geringer der Wärmewiderstand ist, umso schneller und besser erfolgt die Wärmeabfuhr.

Bei Leistungs-MOSFETs für niedrige Sperrspannungen ist der Wärmewiderstand von mehreren Faktoren abhängig. Eine Rolle spielen individuelle Merkmale des jeweiligen Bausteins, wie etwa die Gehäusebauart sowie die Fläche und Dicke des Chips. Abgesehen davon können sich aber auch Unstimmigkeiten im Die-Attach-Prozess (Hohlräume, Voids) dramatisch auf den thermischen Widerstand auswirken und dazu führen, dass die Temperatur in kleinen Bereichen des Chips zunimmt.

Ungleichmäßigkeiten bei den Fertigungsprozessen des Halbleiters können ebenfalls dazu führen, dass eng umgrenzte Hotspots entstehen und damit letztendlich dazu führen, dass ein Baustein ausfällt.

Ein weiterer Risikofaktor ist schließlich auch der Temperaturanstieg. Tatsächlich ist es so, dass der thermische Widerstand von Silizium mit der Temperatur steigt, wodurch die Verlustwärme zu weit von der Sperrschicht entfernten Bereichen schlechter abgeleitet werden können.

Ungleichmäßigkeiten im Die-Attach-Prozess können also zusammen mit hohen Temperaturen zu hohen Werten für Rth in sehr kleinen Zonen des Chips führen und damit die Voraussetzungen dafür schaffen, dass der Baustein thermisch durchgeht und ausfällt [3].

- Sicherer Arbeitsbereich ausgeweitet

- Experimentelle Verifikation