IEDM 2020

Die Highlights der Halbleiterforschung 2020 – Teil 1

Fortsetzung des Artikels von Teil 1

Innovationen in CMOS-Technologien, Speichern und Quanten-Computing.

Neue Wege in der CMOS-Technologie

Gestapelte NMOS-auf-PMOS-Nanoribbons:

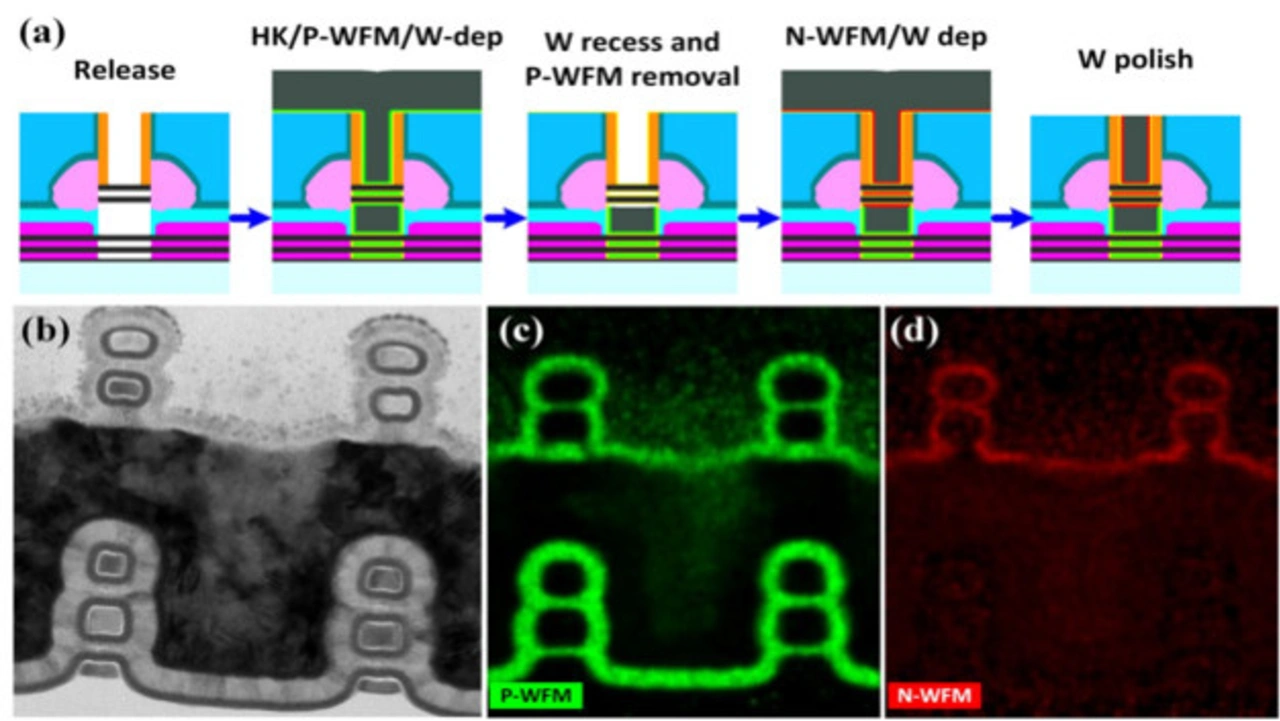

Von planaren MOSFETs über FinFETs bis hin zu Gate-All-Around- (GAA) oder Nanoribbon-Bauelementen haben neuartige Transistorarchitekturen eine entscheidende Rolle dabei gespielt, die vom Moore'schen Gesetz vorhergesagte Leistung zu erreichen. Intel-Forscher werden beschreiben, was der nächste Schritt in dieser Entwicklung sein könnte: NMOS-on-PMOS-Transistoren, die aus mehreren selbstausgerichteten, gestapelten Nanobändern (Nanoribbons) aufgebaut sind. Diese Architektur verwendet einen vertikal gestapelten Dual-Source/Drain-Epitaxieprozess und einen Dual-Metall-Gate-Fertigungsprozess, der es ermöglicht, verschiedene leitfähige Arten von Nanobändern zu bauen, so dass Schwellenspannungsanpassungen sowohl für die oberen als auch für die unteren Nanobänder vorgenommen werden können. Der Ansatz kombiniert eine exzellente Elektrostatik (Unterschwellensteigung von <75 mV/dec) und DIBL (Drain Induced Barrier Lowering) von <30mV/V (für Gates 230 nm) mit einem Weg zu einer signifikanten Reduzierung der Zellgröße aufgrund der selbstausgerichteten Stapelung. Mit diesen Bauelementen wurde ein funktionsfähiger CMOS-Inverter mit ausgewogenen Spannungsübertragungseigenschaften aufgebaut (Paper 20.6).

Nachweis der Machbarkeit von 3D-Designs:

3D-ICs haben das Potenzial, die Leistung gemäß dem Mooreschen Gesetz weiter zu steigern, aber das Erreichen einer geringeren Latenzzeit und Leistungsaufnahme, einer verbesserten Bandbreite und Kosteneffizienz bleibt eine Herausforderung. Das liegt daran, dass es schwierig ist, 3D-IC-Designs zu testen, sobald sie produziert sind. Eine bessere Verknüpfung von Design- und Testfunktionen mit der Prozesstechnologie ist erforderlich, um die Leistung von 3D-ICs zu verbessern. Forscher von Arm und Globalfoundries beschrieben ein 3D-IC-Testvehikel, das die Vorteile dieses Ansatzes demonstriert. Er basiert auf einer hochdichten, Face-to-Face-Wafer-Bonding-Technologie mit 3D-Verbindungen im Abstand von 5,76 µm und 12-nm-FinFETs. Sein cache-kohärentes Interconnect-Mesh (um synchronisierte Operationen in jeder Schicht zu ermöglichen) arbeitete mit bis zu 2,4 GHz, mit einer 10-fach geringeren Bandbreitendichte (3,4 TB/s/mm2) und einem geringeren Energieaufwand (0,02 pJ/Bit) im Vergleich zu modernsten 2,5D/3D-Bumpbond-Technologien. Die Forscher betonen, dass dies ein wichtiger Schritt ist, um die Realisierbarkeit von 3D-Designs für hochleistungsfähige, energieeffiziente ICs der nächsten Generation zu beweisen (Paper 15.1).

CMOS-kompatible Graphene-Verbindungen:

Mit fortschreitender Skalierung leiden herkömmliche Dual-Damascene-Interconnect-Technologien unter höherem Widerstand und Selbsterhitzung sowie verminderter Zuverlässigkeit. Graphen-Interconnects sind gute Kandidaten für Verbindungen in zukünftigen Technologieknoten. Ein Team unter der Leitung der UCSB (University of California in Santa Barbara) hat ein CMOS-kompatibles Festphasen-Wachstumsverfahren beschrieben, mit dem sie großflächige Multi-Level-Graphen-Interconnects auf dielektrischen (Si02) und metallischen (Cu) Substraten herstellen. Die Verbindungen sind BEOL-kompatibel (Back-end of Line) und enthalten randkontaktierende Metall-Vias (im Gegensatz zu Top-Kontakten) in einer dotierten MLG/Co-Via-Mehrebenenstruktur. Die Forscher führten Skalierungsanalysen durch, die zeigten, dass ein Anstieg des Gesamtwiderstands der Vias in der Struktur durch einen geringeren Leitungswiderstand und geringere parasitäre Effekte mehr als kompensiert wird, was zu einer 1,5-fachen Verbesserung der Gesamtleistung der Schaltung im Vergleich zum Dual-Damascene-Prozess führt (Paper 31.1).

Jobangebote+ passend zum Thema

Neue Speicher-Technologien

Hochdichte 28-nm-FDSOI Embedded PCM-Speicher für Automotive:

In heutigen Fahrzeugen werden zahlreiche Mikrocontroller zur Überwachung und Steuerung von Fahrerassistenzsystemen (ADAS), des Antriebsstrangs, Infotainment- und Komfortsystemen und weiteren Funktionen eingesetzt. Diese SoCs (System on Chips) müssen eine hohe Leistung, eine geringe Stromaufnahme und ein hohes Maß an Zuverlässigkeit bieten. Da der Software-Code, mit dem automobile Systeme betrieben werden, immer größer wird, wächst auch der Bedarf an mehr Code-Speicher in hochdichten nichtflüchtigen Embedded-Speichern (eNVM). Auf der IEDM stellte ein STMicroelectronics/CEALeti-Team eine ultra-dichte (Zellgröße = 0,019 µm2) eingebettete Phase-Change-Memory-Technologie (PCM) für Automotive-SoCs vor, die den strengen AEC-Q100-Grade-0-Standard für Zuverlässigkeit im Automobilbereich erfüllt. Sie nutzt ein 28-nm-FDSOI-Substrat (Fully Depleted Silicon-on-Insulator), eine neuartige SSTI-Isolierung (Super-Shallow Trench Isolation) für die Bit-Leitung (die kein Ätzen und Füllen des Grabens erfordert), Triple-Gate-Oxide-Transistoren für hohe Spannungen (5 V) und einen kompakten BJT-Selektor (Bipolar Junction Transistor) (Paper 24.2).

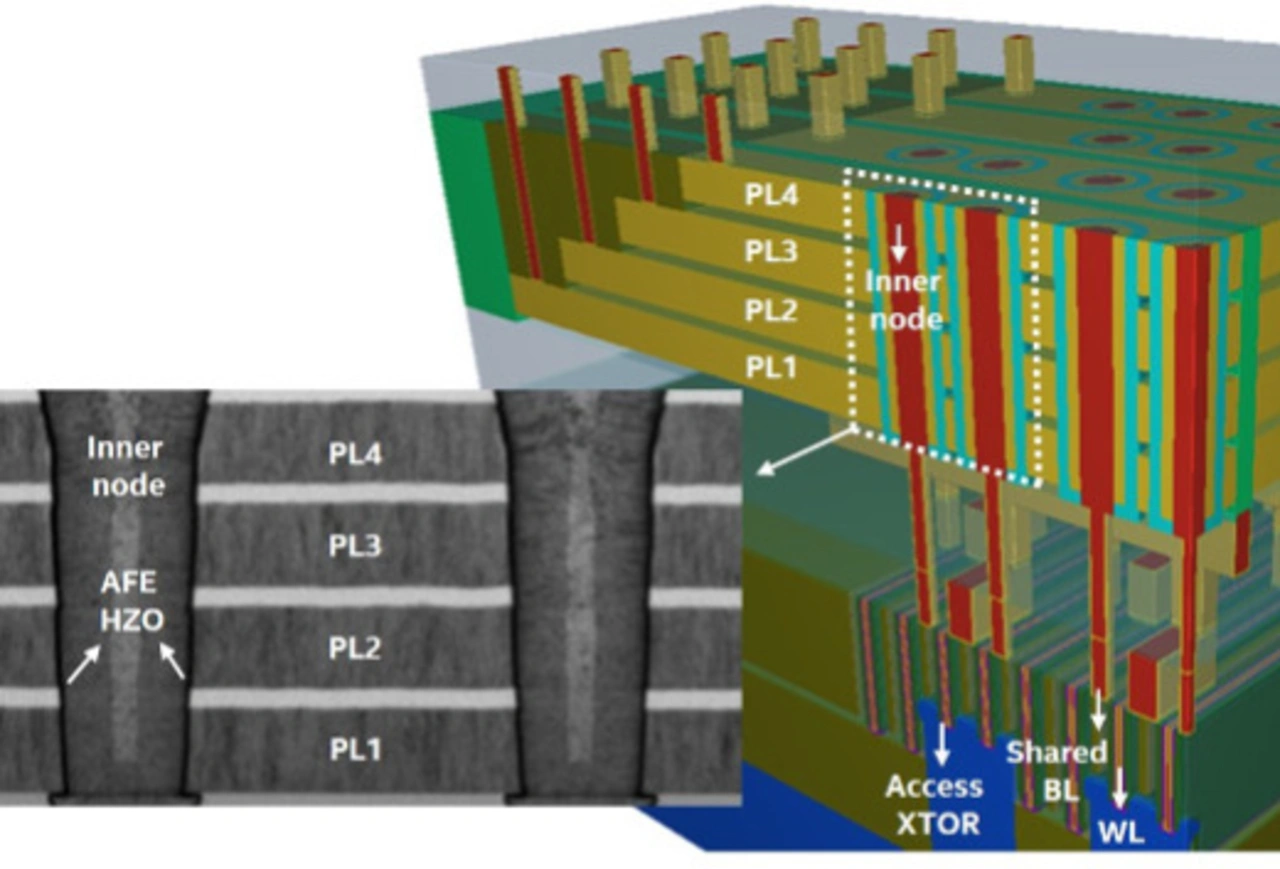

3D Embedded DRAM mit gestapelten antiferroelektrischen HZO-Kondensatoren:

Intel-Forscher stellten ihre Arbeit vor, bei der sie das antiferroelektrische (AFE) Material Hafnium-Zirkonium-Oxid (HfZr02) verwenden, um einen 3D-Kondensator mit tiefem Graben für den möglichen Einsatz in eingebetteten DRAM-Speichern herzustellen. Er zeigte eine Lebensdauer von 10 bis 12 Zyklen selbst bei hohen Temperaturen und eine Betriebsspannung von 1,8 V. Die Forscher verwendeten diese AFE-Kondensatoren in einer neuartigen Speicherarchitektur für ultrahohe Bitdichten: ein vertikaler Stapel, der auf einem Zugriffstransistor mit mehreren parallel geschalteten AFE-Kondensatoren basiert. Jeder Kondensator repräsentiert ein einzelnes Speicherbit. Durch das vertikale Stapeln von vier AFE-Kondensatoren konnte eine signifikante Erhöhung der Dichte erreicht werden, ohne dass die Fläche vergrößert wurde (Paper 28.1).

Eine neue Kraft in ferroelektrischen Tunnel-Junction-Speichern:

Ferroelektrische Tunnelübergänge (FTJs) sind vielversprechende Kandidaten für nichtflüchtige Speicher (NVMs), wie z.B. Ultra-Low-Power-Datenspeicher und neuromorphes Computing. Sie verfügen über eine ultradünne ferroelektrische Barriereschicht, die zwischen zwei Elektroden liegt. Die Modulation des Barrierewiderstands oder der »Höhe« durch die Steuerung der Polarisation verhindert oder ermöglicht das Quantentunneln von Elektronen durch die Barriere und ermöglicht so die Speicherung oder den Abruf von Daten. Die Suche nach einem optimalen Barrierematerial war bisher jedoch eine Herausforderung.

Auf der IEDM diskutierte ein Team unter der Leitung der University of Florida seine Arbeit, bei der es einen ferroelektrischen Tunnelübergang simulierte und baute, indem es dünne Schichten (ca. 4 nm) eines Van-der-Waals-Materials (CulnP2S6 – CIPS) auf einer Graphenschicht vertikal stapelte, um atomare Heteroübergänge an der CIPS-Graphen-Grenzfläche zu erzeugen. Die Heteroübergänge sind zwischen einem Si02-Substrat und einem Top-Metall (Gold) Kontakt eingebettet. (Van-der-Waals-Kräfte sind schwache Anziehungs-/Abstoßungskräfte zwischen Atomen, Molekülen und Oberflächen.) Simulationen der Leistung dieser Heteroübergänge, die durch Laborexperimente verifiziert wurden, zeigten ein rekordverdächtiges Tunnel-Elektrowiderstands-Verhältnis von -6 x 107, was den Weg zu einer möglichen neuen NVM-Speicherbausteinstruktur mit einem exponentiell höheren ON/OFF-Verhältnis als bei bestehenden Bausteinen und Lese-Latenz von 1 ns aufzeigt (Paper 4.1).

Quanten-Computing

Quantencomputer nutzen die Prinzipien der Quantenmechanik, um Daten auf eine neuartige Weise zu verarbeiten. Während heutige Computer Bits aus den Ziffern 0 und 1 manipulieren, verarbeiten Quantencomputer Quantenbits (Qubits), die 0, 1 oder beides gleichzeitig darstellen, dank ihrer Fähigkeit, sich im Quantenzustand der "Superposition" zu befinden. Ein Computer mit vielen Qubits könnte eine immense Anzahl von Berechnungen parallel ausführen, was zu einer unglaublich schnellen, energieeffizienten Leistung führt. Allerdings sind Qubits instabil, mit kurzen "Kohärenzzeiten" (d.h. wie lange sie in einem Quantenzustand bleiben können). Es gibt bereits einige Quantencomputer, aber sie verwenden nur wenige Qubits, sind fehleranfällig und instabil und arbeiten bei kryogenen Temperaturen.

Qubits beginnen, vom Labor in die Fabrik zu kommen:

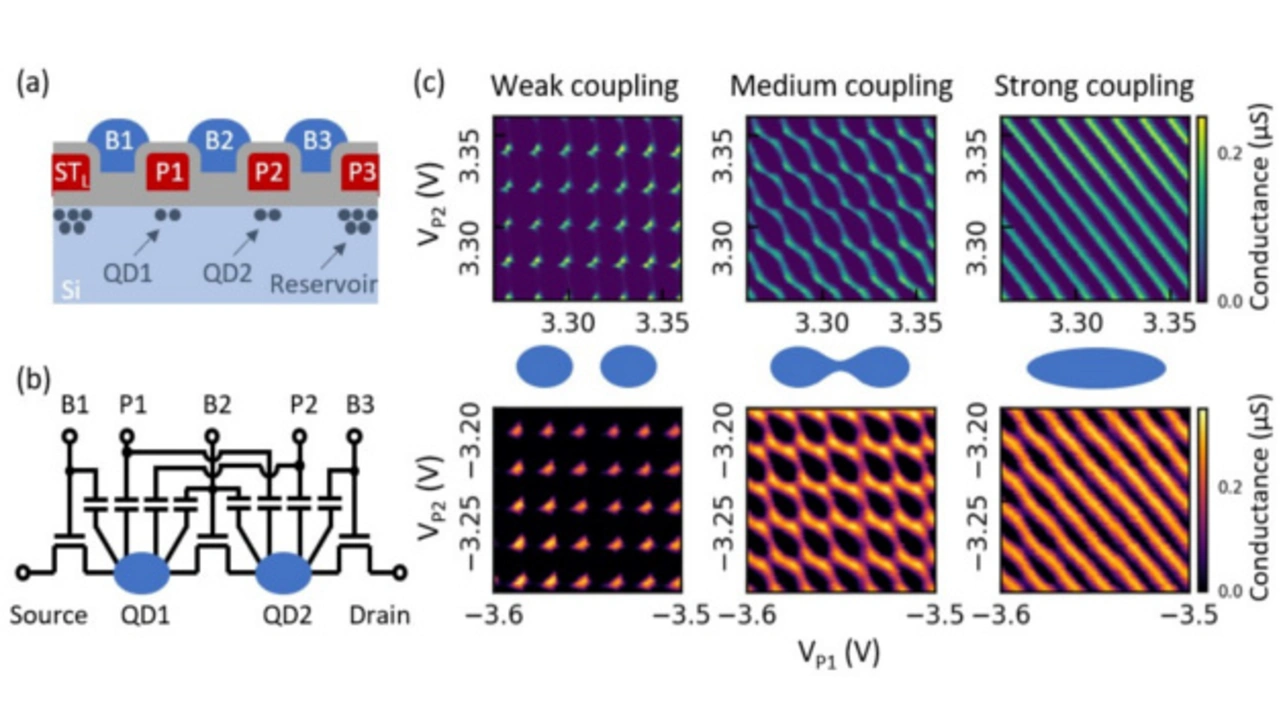

Qubits werden oft aus Quantenpunkten hergestellt, Partikel von wenigen Nanometern Größe, die aus Halbleitern bestehen. Quantenpunkt-Qubit-Systeme auf Siliziumbasis sind für den potenziellen Einsatz in großen Quantenprozessoren attraktiv, weil sie relativ lange Kohärenzzeiten und einen hochgradig zuverlässigen Betrieb in Laborumgebungen gezeigt haben und weil die Siliziumtechnologie im Vergleich zu anderen Materialsystemen weit verbreitet und kostengünstig ist. Aber die kryogenen Materialeigenschaften und andere Aspekte des Qubit-Designs sind immer noch nicht gut verstanden, und es wird eine Design-Plattform benötigt, die flexibel genug ist, um sie für Untersuchungen der Eigenschaften von Silizium-Qubits einzusetzen.

Imec-Forscher beschrieben eine erste derartige Plattform, die auf der industrieüblichen 300-mm-Silizium-Wafer-Fertigungstechnologie anstelle von speziellen Laborprozessen basiert. Sie nutzt sowohl optische als auch Elektronenstrahl-Lithographie zur Herstellung von Silizium-Spin-Qubits und ermöglicht spontane Layout-Änderungen für Bauelemente mit ohmschen Implantationen vom n- oder p-Typ, Abständen <100 nm und einheitlichen kritischen Abmessungen bis hinunter zu 30 nm. Die Forscher sagen, dass sie mit der Designplattform eine nahezu 100%ige Ausbeute für Qubits mit 30 nm Abständen erreichen konnten. Sie planen, die Plattform zu nutzen, um weitere Materialien und Strukturen in Qubits einzubauen und die kryogenen Charakterisierungen zu verbessern (Paper 38.3).

- Die Highlights der Halbleiterforschung 2020 – Teil 1

- Innovationen in CMOS-Technologien, Speichern und Quanten-Computing.