Wide-Bandgap-Leistungshalbleiter

SiC und GaN richtig ansteuern

Fortsetzung des Artikels von Teil 1

Gate-Treiber für SiC-MOSFETs

Einer der Gründe dafür, dass die Entwicklungsingenieure schließlich spezielle Gate-Treiber für SiC-MOSFET wählen, ist die Tatsache, dass jeder MOSFET-Hersteller zur Ansteuerung seiner Produkte eine andere Gate-Source-Spannung empfiehlt. Einige Hersteller raten den Anwendern, ihre SiC-MOSFETs mit einer negativen Spannung auszuschalten. So soll gewährleistet werden, dass das Bauteil vollständig sperrt und Bauteile mit niedriger Gate-Source-Schwellenspannung nicht unbeabsichtigt wiedereinschalten (Parasitic Turn-on). Bei anderen ist zum Sperren des Bauteils keine negative Spannung erforderlich, da deren Gate-Source-Schwellenspannung höher ist.

Bei der Bewertung eines Treibers sagt das Datenblatt viel dazu aus, wie ein SiC-MOSFET damit funktionieren wird. Die wichtigsten Parameter dabei sind:

- die Übertragungseigenschaften (ID = f(UGS)) bei verschiedenen Temperaturen

- die Ausgangseigenschaften (ID = f(UDS)) bei verschiedenen Werten der Gate-Source-Spannung UGS

- der Durchlasswiderstand (RDS(on) = f(ID)) bei verschiedenen Werten der Gate-Source-Spannung UGS.

Tatsächlich beeinflusst die Gate-Source-Spannung UGS den Einschaltwiderstand RDS(on) stark. Manchmal sind die Durchlassverluste bei einem SiC-MOSFET mit einem laut Datenblatt geringeren Einschaltwiderstand einfach deshalb höher, weil er nicht mit der empfohlenen Gate-Source-Spannung angesteuert wird.

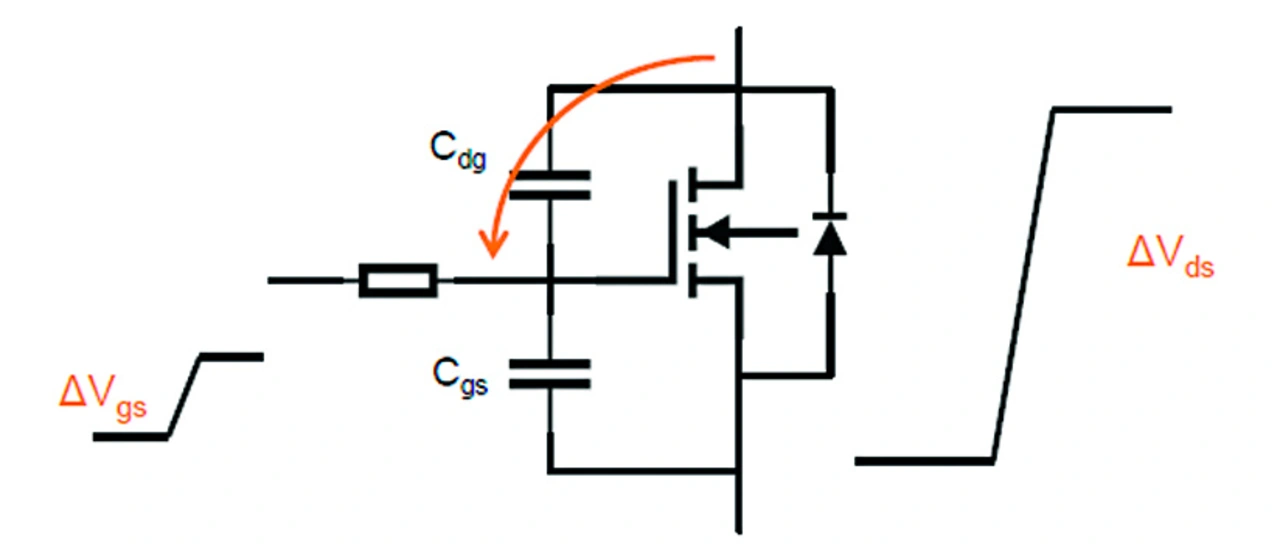

Parasitäres Wiedereinschalten über die parasitären Kapazitäten ist eine häufige Ursache hoher Schaltverluste bei SiC-MOSFET. Wenn die entstehende Gate-Source-Spannung im Vergleich zum Kapazitätsverhältnis des Bauteils höher als der Nennwert der Schwellenspannung Uth ist, dann ist diese Gefahr höher (Bild 1). Die Entwickler sollten auf einen positiven Ausgleich achten, bei dem die Schwellenspannung höher als die entstehende Gate-Source-Spannung ist, um das Bauteil vor der Gefahr eines parasitären Durchschaltens zu schützen.

Ein weiteres Problem, das bei der Spezifikation eines Gate-Treibers für einen schnell schaltenden SiC-MOSFET beachtet werden muss, sind Störspannungen. Ein wichtiger Parameter hierbei ist die Gate-Drain-Kapazität CGD. Wenn eine hohe CGD und eine niedrige Schwellenspannung Uth zusammenkommen, besteht die Gefahr, dass der MOSFET wegen des Miller-Effekts durchschaltet. Zusätzlich kann eine Spannungskopplung durch bauteileigene Kapazitäten zu ungünstigen Wellenformen beim Schalten und unerwünschten Querleitungseffekten führen.

Future Electronics empfiehlt daher bei SiC-MOSFETs, die Angaben im Datenblatt zur Gate-Drain-Kapazität und das Verhältnis der Gate-Source-Kapazität zur Gate-Drain-Kapazität im Auge zu behalten. Ist die Gate-Drain-Kapazität relativ hoch, ist es ratsam, einen Gate-Treiber mit Miller-Klemmfunktion (Miller Clamp) zu wählen. Dort, wo das Verhältnis zwischen Gate-Source- und Gate-Drain-Kapazität niedrig ist, hat es sich als günstig erwiesen, die Gate-Source-Kapazität mit einem externen Kondensator zu vergrößern.

Die Auswertung im Engineering Centre of Excellence von Future Electronics mit der Entwicklungsplattform GaNdalf hat ergeben, dass ein Treiber mit Miller-Klemmung in Verbindung mit einer zusätzlichen Gate-Source-Kapazität die Schaltleistung und den allgemeinen Betrieb des Systems verbessert, was im Weiteren zu einem deutlich höheren Wirkungsgrad, günstigeren Wellenformen und einem niedrigeren Überschwingen führt.

Diese Erfahrung zeigt, dass sich dann die Performance optimieren lässt, wenn ein spezieller Gate-Treiber für SiC-MOSFETs eingesetzt wird. Es ist dennoch möglich, einen einfacheren und günstigeren Gate-Treiber zu wählen. In diesem Fall muss der Entwickler den Betrieb des SiC-MOSFET mit externen Bauteilen regeln, da das System sonst unter schweren thermischen Problemen leiden kann, die den Wirkungsgrad verringern und stärkere Störsignale verursachen.

- SiC und GaN richtig ansteuern

- Gate-Treiber für SiC-MOSFETs

- Gate-Treiber für e-Mode-GaN-HEMTs

- Glossar