Gate-Oxid-Zuverlässigkeit

Siliziumkarbid-MOSFETs im Stresstest

Im Gate-Oxid von SiC-MOSFETs gibt es viele Defekte – lange Zeit ein ernstes Problem bei deren Zuverlässigkeit und für die Kommerzialisierung. Doch in den vergangenen Jahren kamen bessere Fertigungsmethoden und neue Testverfahren – mit Einfluss auch auf die Zuverlässigkeit des Gate-Oxids.

Viele Konzepte und Technologien, die sich bei der Verarbeitung von Silizium durchgesetzt haben, ließen sich bei der Entwicklung der Siliziumkarbid-Technologie (SiC) übernehmen – darunter auch Verfahren, um die Langzeitstabilität von Siliziumbauelementen zu verifizieren. Tiefergehende Analysen haben jedoch gezeigt, dass SiC-basierte Bauelemente noch zusätzliche Zuverlässigkeitstests erfordern. Zum Beispiel ist das Material selbst auf spezifische Defektstrukturen zu untersuchen.

Des Weiteren sind im Gegensatz zu Silizium auftretende Anisotropien und andere mechanische sowie thermische Eigenschaften zu berücksichtigen. Zudem haben SiC-Bauelemente im Gegensatz zu Si-Bausteinen eine größere Bandlücke, was sich auf Dichte und Dynamik von Grenzflächenzuständen in MOS-basierten Bauelementen auswirkt.

Im Betrieb entstehen innerhalb des Materials und an den äußeren Grenzflächen – zum Beispiel an den Randabschlussstrukturen – bis zu zehnmal stärkere elektrische Felder, was wiederum die Lebensdauer des Oxids beeinflussen kann und spezielle Abschirmstrukturen erfordert. Gleichzeitig können im Gate-Oxid von SiC-MOSFETs vermehrt Schwachstellen auftreten, die auf sogenannte extrinsische Defekte zurückzuführen sind.

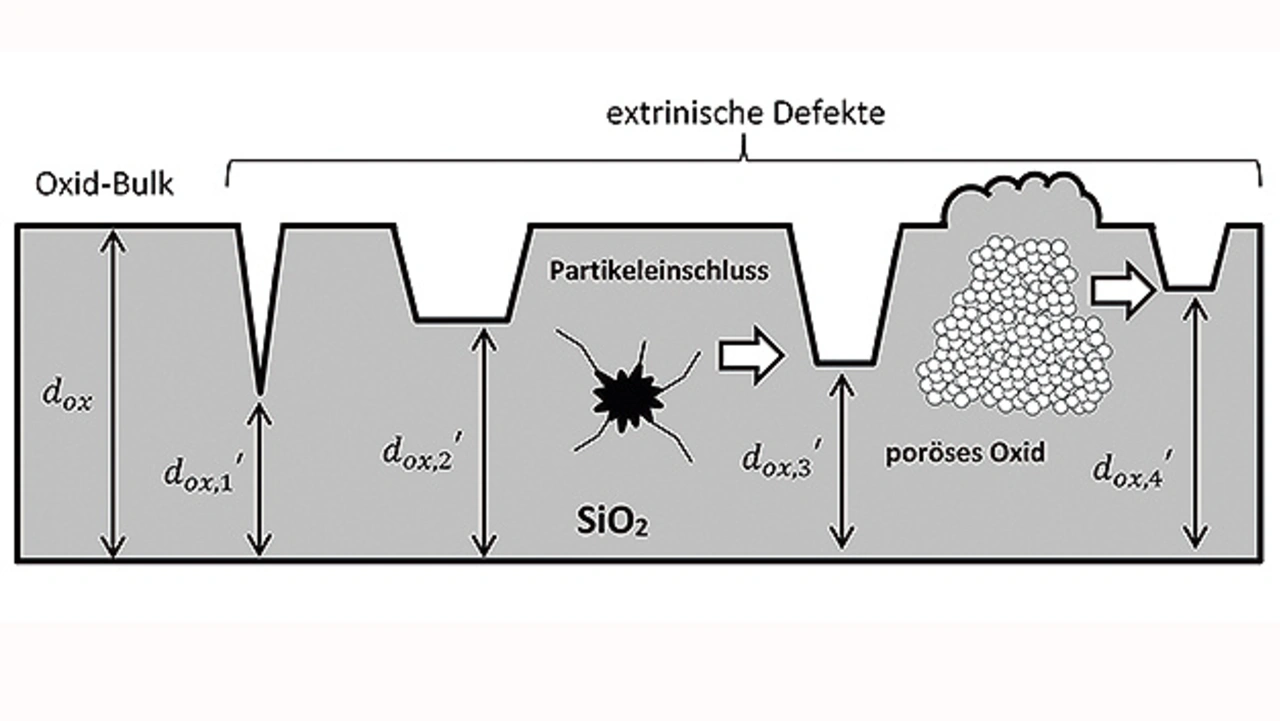

Dabei handelt es sich um winzige Verzerrungen bzw. Störungen im Gate-Oxid, die im Prinzip so wirken, als wäre das Oxid an diesen Stellen dünner. Derartige Störungen stehen oft in Zusammenhang mit Epitaxie- oder Substratdefekten [1], metallischen Verunreinigungen, Partikeln oder anderen extrinsischen Einschlüssen im Gate-Oxid, die während der Herstellung der Bauelemente eingebracht wurden (Bild 1).

Jobangebote+ passend zum Thema

Weil die extrinsische Defektdichte bei SiC selbst heute noch immer viel größer ist als bei Silizium, sind neben Maßnahmen, die die Defektdichte verringern, auch Methoden wichtig, die die Auswirkung der Defekte auf das Endprodukt reduzieren. Solche Methoden sind zum Beispiel elektrische Selektionsverfahren, sogenannte Screening-Verfahren. Beides erfordert ein hohes Maß an Know-how und ein breites Hintergrundwissen rund um die Herstellungsprozesse, Materialeigenschaften und Ausfallmechanismen. Infineon hat neben der langjährigen Expertise mit Siliziumtechnologien auch wissenschaftliche Kooperationen während der Entwicklung und Produktion von SiC-basierten Leistungsbauelementen genutzt, um diese intensiv zu analysieren und maßgeschneiderte Screening-Verfahren zu entwickeln.

So konnte das Unternehmen neue Tests und Modellierungsansätze entwickeln, die auch Betriebsarten einbeziehen, die bei Silizium-Leistungshalbleitern weniger üblich sind. Zusätzlich modifiziert es bereits etablierte Tests, um SiC-spezifische Anforderungen zu berücksichtigen. Im Laufe der Zeit entstanden somit aussagekräftige Charakterisierungs- und Validierungsschemata, die auf Stresstestanalysen beruhen, die auf spezifischen Mission-Profilen basieren. Mit diesen lassen sich kritische Betriebsbedingungen für SiC-Bauteile bewerten und neue potenzielle Ausfallmechanismen verstehen.

Elektrisches Gate-Oxid-Screening

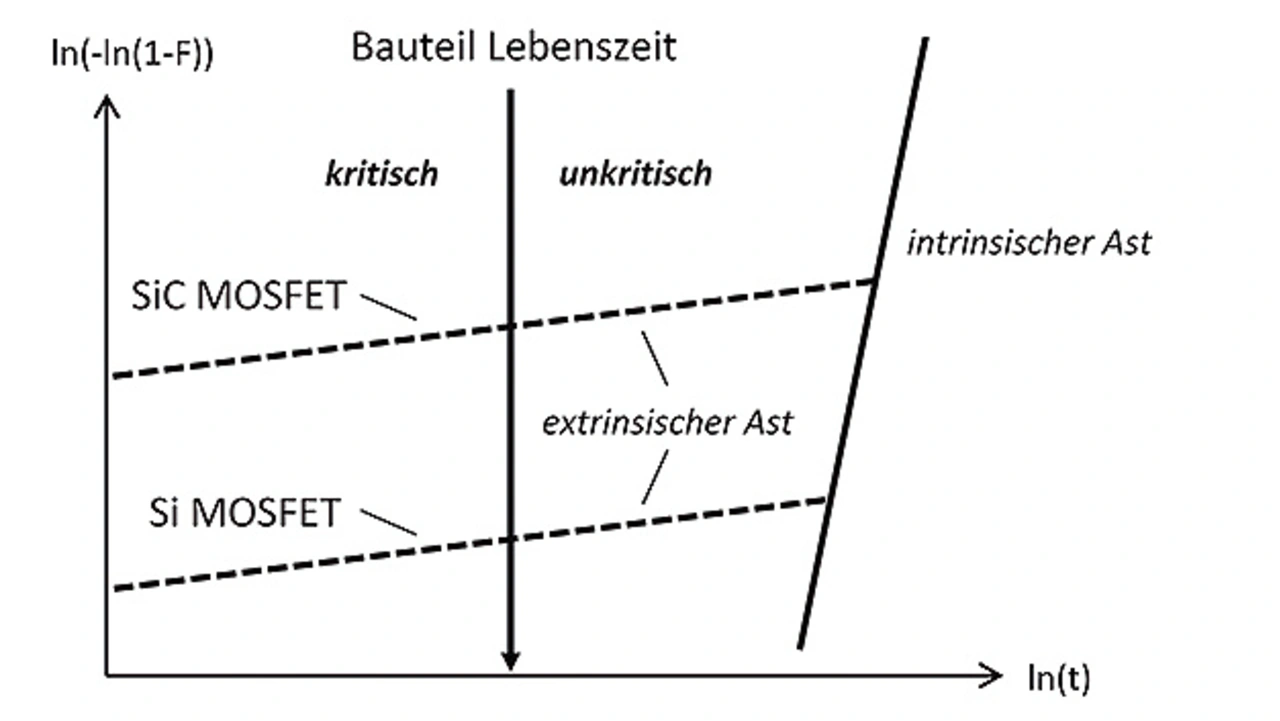

Indem die Defektdichte während des Herstellungsprozesses minimiert wird, verringert sich die Anzahl an Bauteilen, die am Ende des Prozesses kritische Gate-Oxid-Defekte beinhalten. Trotzdem weisen heute auf Siliziumkarbid gefertigte Gate-Oxide noch deutlich höhere extrinsische Defektdichten auf als vergleichbare Silizium-Bausteine (Bild 2).

Dadurch steigt die Wahrscheinlichkeit für Frühausfälle im Feld. Damit SiC-MOSFETs ähnlich zuverlässig arbeiten wie ihre Gegenstücke aus Silizium, sind daher zusätzliche elektrische Selektionsverfahren nötig. Nur so lassen sich potenziell schwache Bauelemente mit hinreichender Effizienz identifizieren und eliminieren.

Ein klassisches Beispiel für ein solches elektrisches Auswahlverfahren ist ein Burn-in-Test. Bei diesem Test werden die Bauelemente typischerweise bei niedrigen Gate-Spannungen und erhöhten Temperaturen für längere Zeit belastet. Bauteile, die ausfallen, werden entfernt, die anderen dürfen ausgeliefert werden. Dieser Ansatz hat jedoch mehrere Nachteile: Ein Burn-in ist zeitaufwendig, kostspielig und kann aufgrund des langanhaltenden Gate-Stresses bei hoher Vorspannung (Bias) und hoher Temperatur dazu führen, dass kritische elektrische Bauteilparameter wie z. B. die Schwellenspannung und der On-Widerstand zu driften beginnen.

Diese Effekte sind allgemein als Spannungs-Temperatur-Instabilitäten (Bias Temperature Instabilities) bekannt [2]. Besser geeignet ist darum ein weitaus kürzerer, dafür deutlich schärferer elektrischer Endtest, der im Folgenden als »Screeningtest« bezeichnet wird: Dabei werden die einzelnen Bauelemente hohen Spannungspulsen am Gate mit definierter Amplitude und Zeit ausgesetzt [3] [4]. Spannung und Zeit werden dabei so ausgelegt, dass Bauelemente mit kritischen extrinsischen Defekten ausfallen. Übrig bleiben nur Chips ohne oder mit nur unkritischen extrinsischen Defekten. Die Zuverlässigkeit des Gate-Oxids bei der überlebende Population ist nach dem Screeningtest deutlich höher [5].

Eine Voraussetzung für ein schnelles und effizientes Gate-Spannungs-Screening ist eine Bulk-Oxidschicht, die deutlich dicker ist als jene, die nötig wäre, um lediglich intrinsische Lebensdauerziele zu erfüllen. Durch die dickere Oxidschicht lassen sich Screening-Spannungen verwenden, die erheblich höher sind als die typische Betriebsspannung der Bauelemente, ohne dass dadurch fehlerfreie Bauelemente geschädigt werden. Dabei gilt: Je höher das Verhältnis von Screeningspannung zu Betriebsspannung ist, desto effizienter wirkt das elektrische Screening und desto niedriger ist danach die Fehlerwahrscheinlichkeit im Feld [6].

Ein Nachteil der dickeren Bulk-Oxidschicht ist ein leicht erhöhter elektrischer Widerstand im MOS-Kanal. Dieser ist in erster Näherung direkt proportional zur Dicke des Gate-Oxids und kann in bestimmten Fällen einen großen Teil des gesamten On-Widerstands ausmachen. Dies gilt insbesondere bei Bauelementen niedrigerer Spannungsklassen, die einen vergleichsweise geringen Widerstand in der Driftzone aufweisen. Die hohe Screeningeffizienz und damit auch die ausgezeichnete Gate-Oxid-Zuverlässigkeit von SiC-MOSFETs haben also einen Preis: Der On-Widerstand steigt leicht.

Dieser Kompromiss lässt sich zwar nicht völlig umgehen, doch die Tatsache, dass sich die Bulk-Oxiddicke unterschiedlich stark auf den On-Widerstand und die Zuverlässigkeit des Gate-Oxids auswirkt, kann man nutzen. So steigt die Zuverlässigkeit des Gate-Oxids durch Verwendung höherer Screeningspannungen exponentiell mit der Oxiddicke, während sich der On-Widerstand oft nur minimal erhöht. Bei höheren Temperaturen ist der Anteil des Driftzonen-Widerstands noch ausgeprägter, wodurch die Leistungseinbuße eines dickeren Bulk-Oxids in relativen Zahlen ausgedrückt nochmals deutlich kleiner wird. Nutzt man eine dickere Bulk-Oxidschicht, verzichtet man also bewusst auf ein nur geringes Maß an Leistungsfähigkeit; im Gegenzug erhöht sich die Zuverlässigkeit der Bauteile jedoch drastisch.

- Siliziumkarbid-MOSFETs im Stresstest

- Extrinsische Gate-Oxid-Zuverlässigkeit bewerten