Servo-Motorregelungen

Schnellere Stromregelkreise zeichnen sich aus

Fortsetzung des Artikels von Teil 1

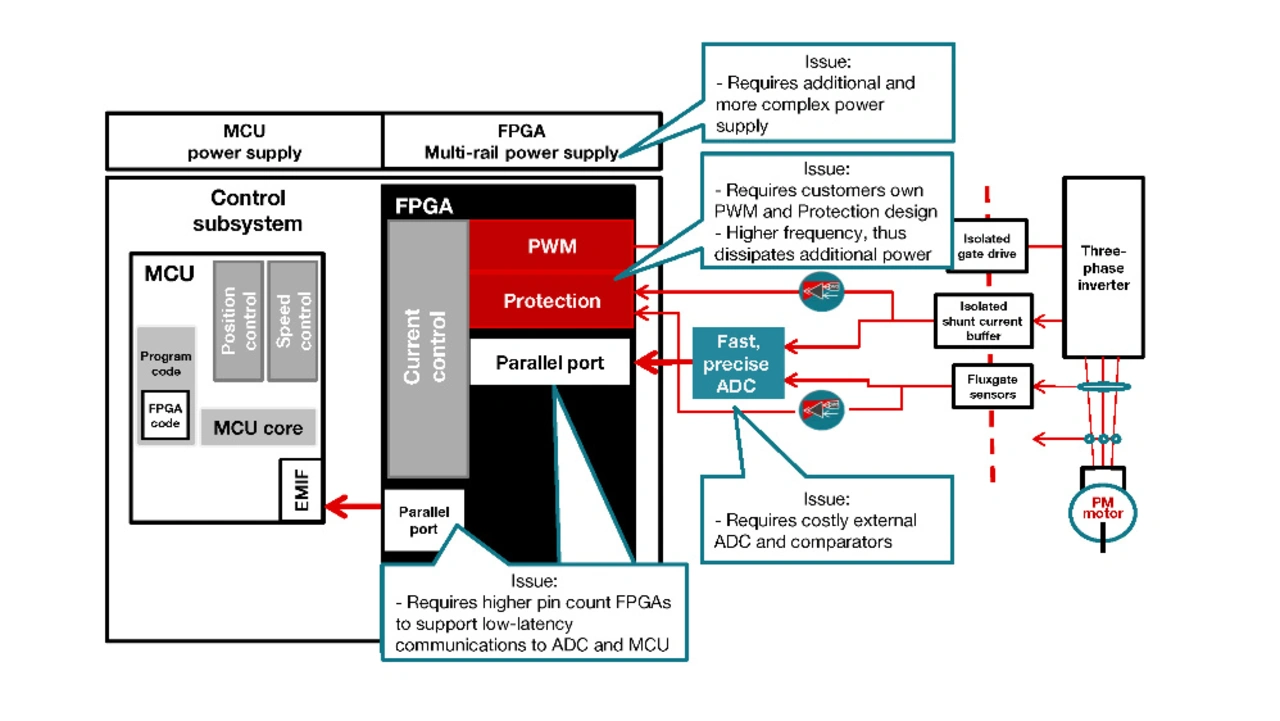

FPGA-Architekturen

Wenn man einen Servo-Antrieb mit einem FPGA ausstattet, entfällt damit keineswegs die Notwendigkeit für einen Mikrocontroller, der für die Drehzahl- und Positionsregelkreise zuständig ist und gelegentlich auch für die Benutzeroberfläche und die Konnektivität. Das Einfügen eines FPGA in den Stromregelkreis hat Folgewirkungen für das gesamte übrige Design (Bild 1).

Um den gesamten Stromregelkreis abzudecken, verlangt das FPGA nach individueller Designarbeit, um die PWM-Generierung, Schutzschaltungen für den Wechselrichter und Kontrolllogik zur Abtastung des Analogsignals einzuschließen. Diese Designarbeit macht die Systementwicklung komplizierter, treibt die Gatterzahl und die Kosten des FPGA in die Höhe und bringt nicht zuletzt auch höhere Design- und Support-Risiken mit sich.

Da die meisten FPGAs über keine integrierten ADCs mit genügend Leistungsfähigkeit und Auflösung für Servomotor-Regelungen verfügen, müssen diskrete ADCs und Analogkomparator-Schaltungen in das System integriert werden. Das FPGA benötigt außerdem auch parallele I/O-Schnittstellen, um die Latenz der Datentransfers vom ADC zu minimieren und eine schnelle Kommunikation mit der MCU zu ermöglichen.

Hierdurch nehmen der Pin Count und die Kosten des FPGA sowie der von ihm benötigte Platz auf der Leiterplatte weiter zu. Als letzter Punkt kommt hinzu, dass ein FPGA-Design in der Regel ein komplexeres Stromversorgungs-Subsystem erfordert – möglicherweise mit zusätzlichen Versorgungsspannungen und höheren Strömen, als sie für den Mikrocontroller und die übrigen Bauelemente üblicherweise benötigt werden.

Natürlich beherbergt ein FPGA, wenn es erst einmal im System vorhanden ist, einen Funktionsumfang, der sonst entweder mit diskreten Bauelementen oder gar nicht implementiert worden wäre. In einer Servomotor-Regelung könnten beispielsweise Delta-Sigma-ADC-Filter, Encoder-Schnittstellen, die Erzeugung von Impulszug-Ausgängen und andere Funktionen integriert werden. Hat dieser Integrations-Trend erst einmal eingesetzt, ist das Resultat ein sehr großes und teures FPGA mit sehr vielen Pins.

Schnelle Stromregelkreis-Software

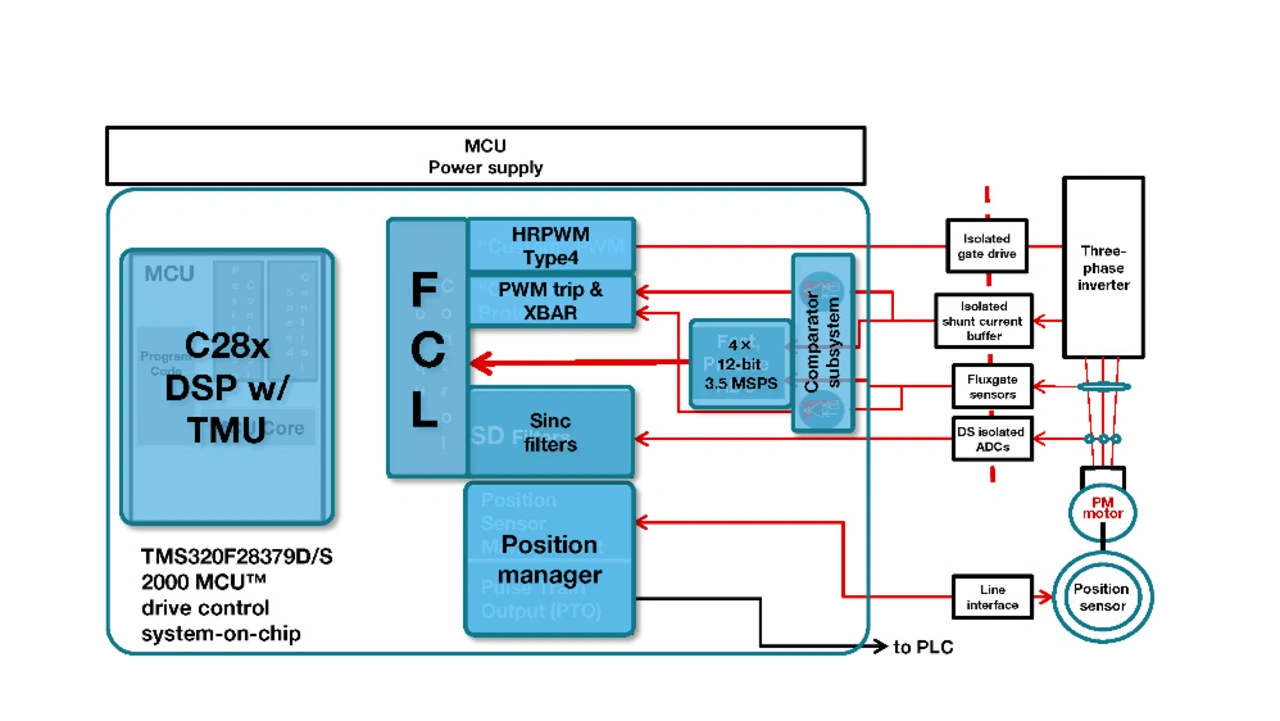

Eine effektive Alternative, die viele der bei der Ausstattung einer Servoregelung mit einem teuren FPGA entstehenden Herausforderungen umgeht, wäre die Implementierung dieser Funktionen in der MCU. Wenn man von den Echtzeit-MCUs der C2000-Familie von TI absieht, gibt es jedoch nur wenige Mikrocontroller mit den entsprechenden Fähigkeiten am Markt.

TI nutzte seine zwanzigjährige Erfahrung im Design industrieller Echtzeit-Regelungssysteme für die Verwendung der C2000-MCUs zur Entwicklung der neuen FCL-Software (Fast Current Loop). Die DesignDRIVE-Plattform mit der FCL-Software resultiert in einer enormen Vereinfachung des Designprozesses, während weniger wünschenswerte Eigenschaften gleichzeitig vermieden werden.

Einfach ausgedrückt beseitigt die FCL-Software viele der seit langem geltenden Anschauungen beim Design von Stromregelkreisen. Zum Beispiel haben Designer von Servomotor-Regelungen der Bandbreite des Stromregelkreises jahrelang Beschränkungen auferlegt, weil sie davon ausgingen, dass der Controller das PWM-Signal in jedem Zyklus des Regelkreises nur einmal aktualisieren kann.

Jetzt, mit einem integrierten, leistungsfähigen SAR-ADC (Successive Approximation Register), ADC-Nachverarbeitungs-Hardware, einem Beschleuniger für trigonometrische Berechnungen und weiteren Cycle-Scavenging-Ressourcen, können die C2000-MCUs in weniger als einer Mikrosekunde die Motorströme abtasten und in digitale Daten umwandeln, diese Daten verarbeiten und den PWM-Generator aktualisieren.

FOC-Verarbeitung und PWM-Aktualisierung nehmen weniger als 500 ns in Anspruch. Wegen der FCL-Software und der Fähigkeiten der C2000-MCU im ePWM Immediate Mode werden PWM-Updates auch innerhalb eines Zyklus so schnell wie möglich ausgeführt, anstatt den Ablauf eines kompletten Regelkreiszyklus abzuwarten.

Designer gingen ferner davon aus, dass eine höhere Stromregelkreis-Bandbreite eine höhere Trägerfrequenz voraussetzt. Zum Beispiel hätte eine Bandbreitensteigerung um den Faktor 3 von 1 kHz auf 3 kHz demnach ein Anheben der Trägerfrequenz von 10 kHz auf 30 kHz erfordert.

Die von den C2000-MCUs gebotene Fähigkeit, PWM-Updates auch innerhalb der Zyklen in weniger als einer Mikrosekunde vorzunehmen, verbessert die Bandbreite des Stromregelkreises, wodurch die Schaltfrequenz für eine bestimmte Bandbreitenvorgabe reduziert oder optimiert werden kann.

Wie Tests gezeigt haben, lässt sich die Bandbreite des Stromregelkreises per FCL von 1 kHz ausgehend um den Faktor drei auf rund 3,3 kHz anheben, während die Trägerfrequenz von 10 kHz beibehalten werden kann. Mit dem Einsatz der FCL-Technik werden somit die Nachteile des höheren Strombedarfs, der vermehrten Wärmeentwicklung sowie komplexerer und teurerer Wärmemanagement-Strategien vermieden.

Bei den TMS320F28379-MCUs handelt es sich um hochintegrierte Bausteine für industrielle Antriebssysteme. Chipintegrierte Features wie etwa Sigma-Delta-Filter, Analog-Komparatoren und PWM-Schutzschaltungen sparen auf System-Ebene Kosten gegenüber der externen Implementierung dieser Funktionen. Die Position-Manager-Lösungen für Absolut-Encoder-Schnittstellen sowie die Erzeugung von Impulszug-Ausgängen sorgen dafür, dass auch hierfür weniger externe Logikgatter hinzugefügt werden müssen.

Mit der Einführung der FCL-Software stehen die Systemfunktionen, die traditionell mit FPGAs umgesetzt wurden, nunmehr in der DesignDRIVE-Lösungsbibliothek zur Verfügung (Bild 2). Die MCUs der TMS320F2837x-Familie werden deshalb zurecht als Antriebssteuerungs-SoCs bezeichnet.

Eine weitere Herausforderung beim Design leistungsfähiger Stromregelkreise war stets die Stabilität des Reglers bei hohen Drehzahlen. Digitale oder übertragungsbedingte Verzögerungen lassen die Phasenreserve des Stromregelkreises bei hohen Drehzahlen immer mehr abnehmen, bis schließlich keine Regelung mehr möglich ist. Traditionelle Stromregelkreise bilden diese digitalen Verzögerungen nicht besonders gut nach.

- Schnellere Stromregelkreise zeichnen sich aus

- FPGA-Architekturen

- Stabilität auch bei höheren Drehzahlen