Das Motto: »Klein, aber oho«

Hochintegrierte, kompakte MCUs für platzsparende Designs

Immer kompakter, leistungsfähiger, effizienter: Moderne Embedded-Systeme benötigen kleine, integrierte Bausteine. MCUs wie der MSPM0C1104 zeigen, wie platzsparende Gehäuse und eine hohe Integrationsdichte Fläche sparen, Kosten senken und die Entwicklung vereinfachen.

Mein erstes Handy war ein Klapptelefon in einem ziemlich coolen Pink. Auch wenn man damit wirklich nur telefonieren konnte, handelte es sich um ein faszinierendes Stück Technik. Der Reiz ist bis heute noch vorhanden, allerdings erwarte ich inzwischen von jedem neuen Handy deutlich mehr, wie ein höher auflösendes Display, eine längere Akkulaufzeit, schnellere Prozessoren und vor allem auch kleinere Abmessungen.

Mit diesen Erwartungen stehe ich natürlich nicht allein da. Die meisten Verbraucher wünschen sich stetige Verbesserungen in Bezug auf Größe und Funktionsumfang, und das gilt nicht nur für Handys und Smartwatches, sondern beispielsweise auch für einen Haarföhn. Ohne Fortschritte beim Preis, der Größe oder der Ausstattung dürften die meisten Verbraucher wenig geneigt sein, ein vorhandenes Produkt durch ein neues Produkt der nächsten Generation zu ersetzen.

Der Trend zu kompakteren und leistungsfähigeren Elektronikgeräten betrifft auch Entwickler von Embedded Systemen. Auch sie müssen die Funktionalität und Leistungsfähigkeit ihrer Systeme steigern und gleichzeitig die Abmessungen und Kosten des Systems reduzieren.

Zur Unterstützung dieser Designer entwickeln Halbleiterhersteller wie Texas Instruments (TI) Mikrocontroller (MCUs) und Embedded-Prozessoren mit vielen Funktionen, und dennoch in kompakter Bauform. Kennzeichnend für diese Bausteine sind optimierte Gehäuse, die auf der Leiterplatte weniger Fläche benötigen, sodass mehr Platz für zusätzliche Bauteile und größere Akkus bleibt, um längere Betriebszeiten zu erzielen. Auch innerhalb dieser Gehäuse geht die Entwicklung weiter, beispielsweise durch Integration zahlreicher analoger Funktionen, um die Fähigkeiten zu erweitern und gleichzeitig den Bedarf an externen Bauelementen zu verringern.

Der vorliegende Artikel befasst sich damit, wie Gehäusetechnologien und die Integration analoger Funktionen dazu beitragen, die Größe von Embedded Systemen zu reduzieren, ohne dabei Abstriche an der Funktionalität machen zu müssen – und welche Auswirkungen dies auf die Fertigungsprozesse hat.

Gehäusetechnologien

Innovationen auf der Seite der Packaging-Technologien gehören zu den wenigen Fortschritten im Halbleitersektor, die auch mit bloßem Auge sichtbar sind. Moderne Bauformen verzichten auf unnötige Kunststoffummantelungen und Anschluss-Pins, indem sie von traditionellen bedrahteten Bauformen auf fortschrittlichere Gehäuse umsteigen. Die Größe dieser Gehäusevarianten hängt direkt von der Größe des Dies ab und kann die für eine bestimmte Funktion benötigte Leiterplattenfläche deutlich verringern.

TI bietet in seinem Embedded-Processing-Portfolio mehrere Miniaturgehäuse zur Wahl, einschließlich:

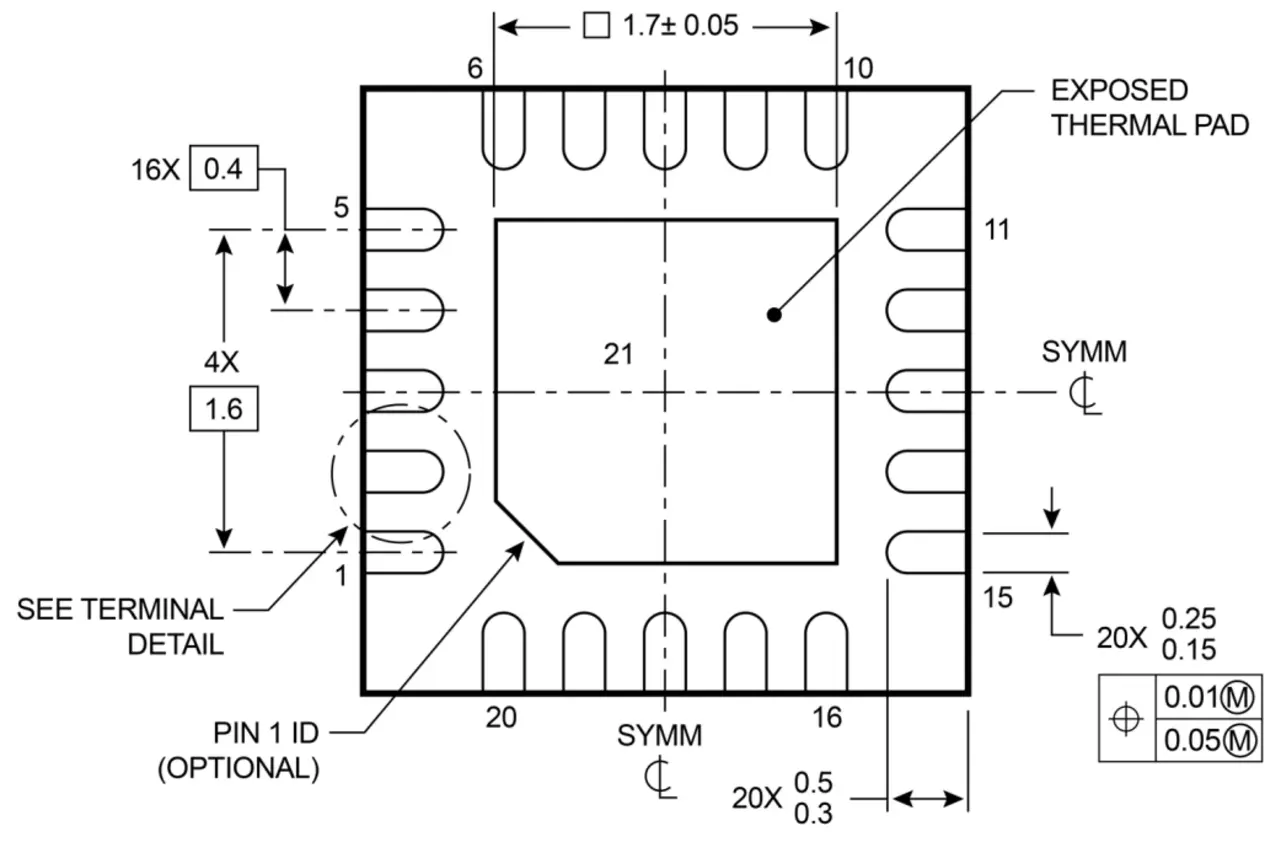

Quad Flat No-lead (QFN) – anstelle von traditionellen herausgeführten Anschlüssen ist ein QFN-Gehäuse mit flachen Kontakten an den Rändern seines Kunststoffgehäuses ausgestattet. Seine thermischen Eigenschaften werden durch eine eigene Wärmableitfläche an der Unterseite verbessert. Bild 1 zeigt als Beispiel das nur 9 mm² messende, 20 Kontakte aufweisende Gehäuse des Mikrocontrollers MSPM0C1104.

Jobangebote+ passend zum Thema

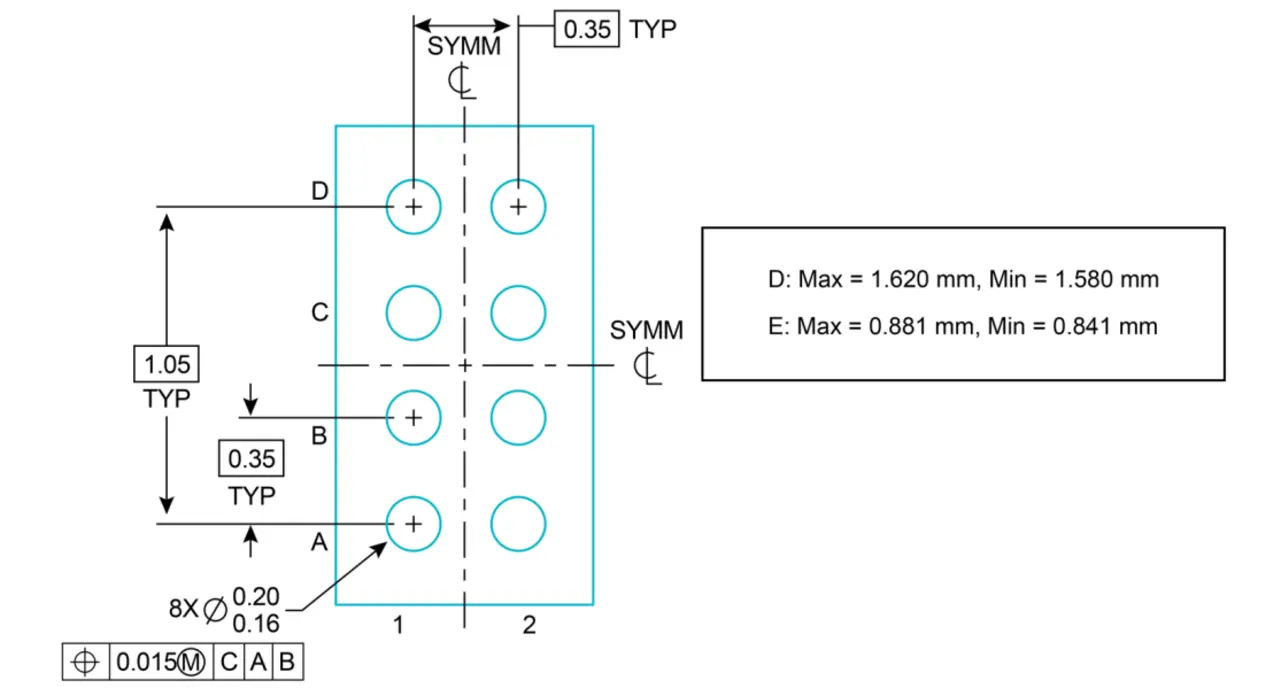

Wafer Chip-Scale Package (WCSP) – dieser Gehäusetyp zeichnet sich gegenüber anderen Bauformen durch die kleinsten Abmessungen aus. Die Lotkügelchen sind direkt mit dem Halbleiterchip verbunden, sodass das Gehäuse nur geringfügig größer ist als der eigentliche Die (Bild 2). Acht solcher Lotkügelchen auf einer Fläche von nur 1,38 mm² ermöglichen eine besonders dichte Funktionsintegration pro Flächeneinheit. Der MSPM0C1104 ist ebenfalls in einer WCSP-Version lieferbar, die 38 Prozent kleiner ist als konkurrierende Bauelemente und ihn damit zum kleinsten Mikrocontroller der Welt macht.

Integration

Eine weitere Möglichkeit zur Platzersparnis besteht darin, die in den Baustein integrierten Funktionsblöcke zu optimieren. Einzelbausteine mit eigenem Kunststoffgehäuse und eigenen Anschlüssen und dem entsprechenden Flächenbedarf beanspruchen deutlich mehr Leiterplattenfläche als ein einzelner Chip mit denselben integrierten Funktionen.

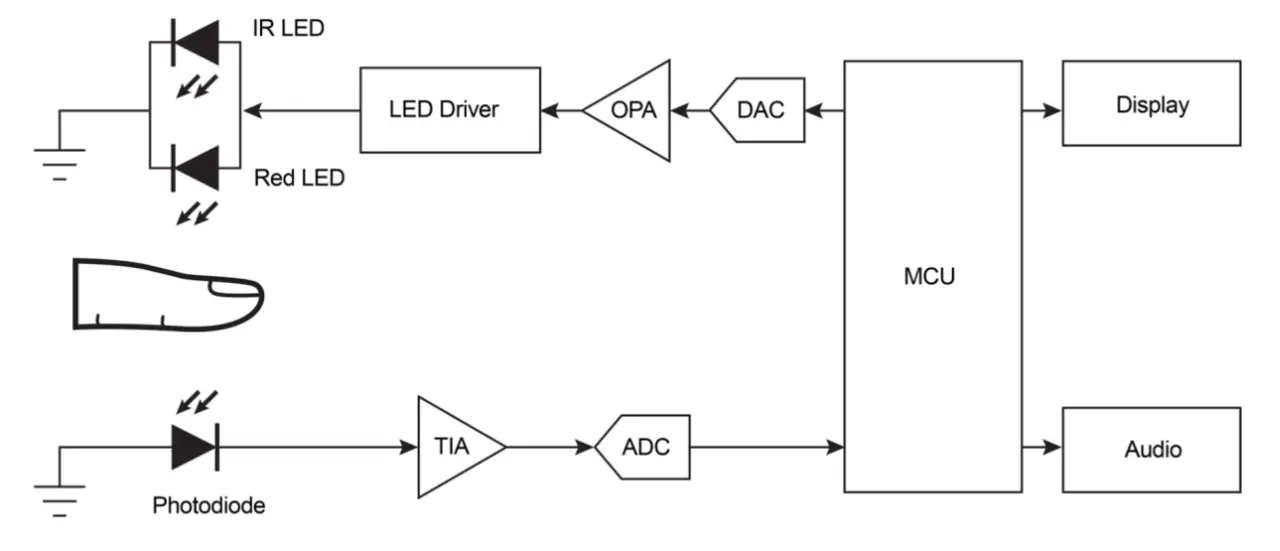

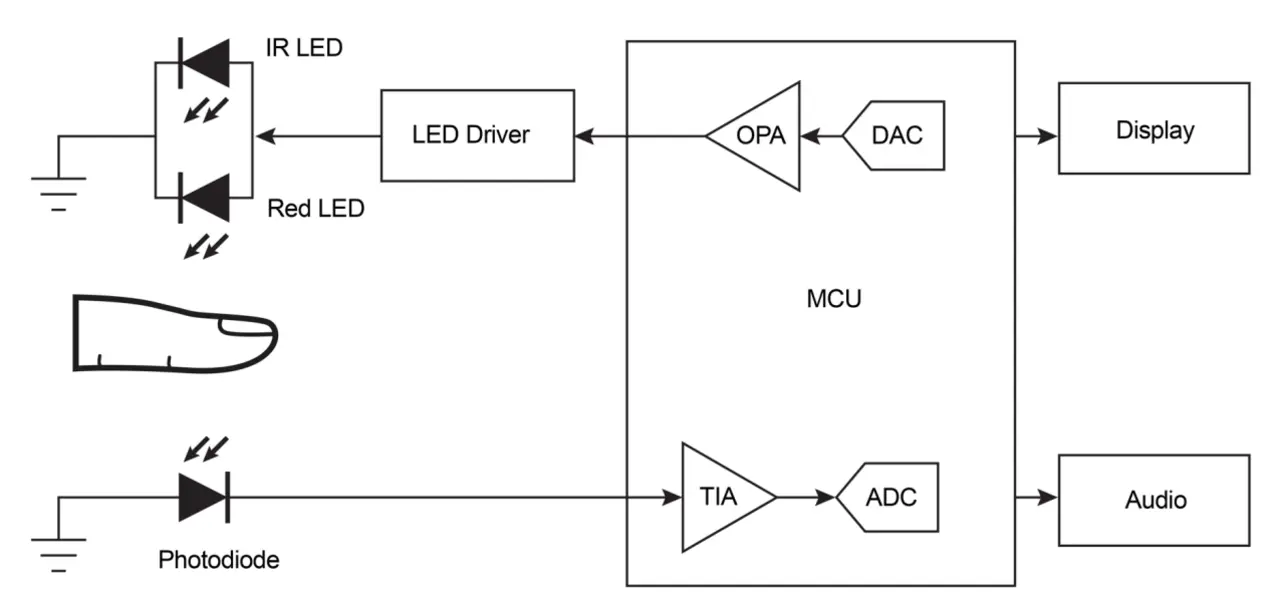

MCUs und Prozessoren mit integrierten analogen und digitalen Peripheriefunktionen können die Miniaturisierung deutlich vorantreiben. Das lässt sich am Beispiel eines Pulsoximeters deutlich machen. Verglichen mit einem diskreten Design-Ansatz, wie in Bild 3 dargestellt, kann eine MCU mit integriertem A/D-Wandler (ADC), Komparator und Spannungsreferenz die Zahl der benötigten Bauelemente deutlich reduzieren, und damit auch die Leiterplattenfläche verringern, wie Bild 4 verdeutlicht.

Wichtig ist dabei ein ausgewogenes Maß: Einerseits verringert eine hohe Integration zwar den Bauteileaufwand eines Designs, andererseits kann das Integrieren unnötiger Features der eigentlichen Intention zuwiderlaufen und dazu führen, dass eine Single-Chip-Lösung sogar mehr Platz benötigt.

Deshalb ist eine optimierte Feature-Ausstattung von entscheidender Bedeutung, denn der Umfang der integrierten Peripheriefunktionen wirkt sich direkt auf die Chipgröße und die Kosten des Bauelements aus. Ungenutzte Funktionen vergeuden sowohl Platz als auch Geld und reduzieren die Effizienz eines platzbeschränkten Designs. Erst wenn man die wirklichen Anforderungen des Markts verstanden hat, kann man Embedded-Prozessoren hervorbringen, die in Bezug auf Größe und Preis wettbewerbsfähig sind. Der MSPM0C1104 zeigt wie es geht: Der Baustein sitzt in einem WCSP-Gehäuse mit acht Balls. Damit ist er nicht nur klein, sondern er enthält auch eine Vielzahl integrierter Features und Funktionen. Auf einer Fläche von nur 1,38 mm² sind 16 KB Flash-Speicher, ein dreikanaliger 12bit-ADC und drei Timer integriert – ideal für Designs, die kompakt und leistungsfähig zugleich sein müssen.

Fertigung/Bestückung im Miniaturmaßstab

Mit schrumpfenden Chip-Größen entwickeln sich auch die Design- und Produktionsmethoden weiterentwickelt. Der Umstieg auf kleinere elektronische Bauelemente trägt zwar zur Minimierung der Leiterplattenfläche bei, aber zusätzlich müssen das Layout, das Handling und der Produktionsablauf berücksichtigt werden.

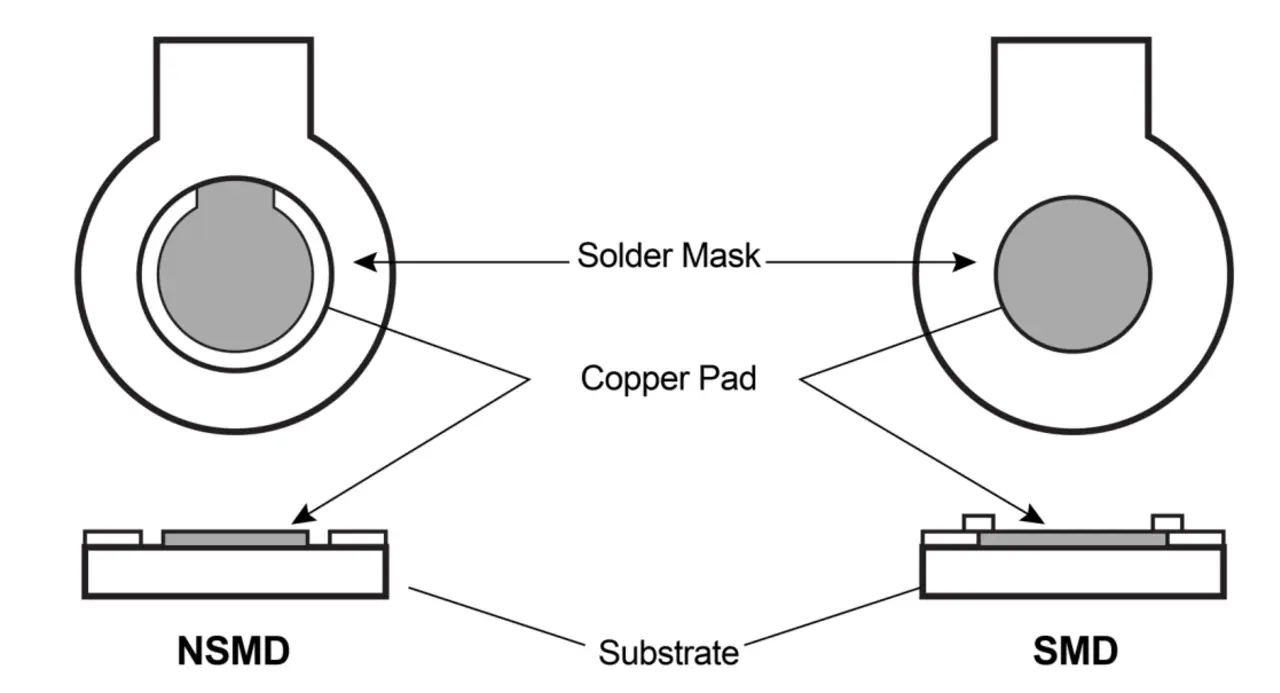

Beim Design mit Wafer-Chip-Scale-Gehäusen sind zwei Arten von Anschlussflächen (Land Patterns) gängig: SMD (Solder Mask Defined; dt.: Lötmasken-definiert) und NSMD (Non-Solder Mask Defined; dt.: Nicht-Lötmasken-definiert) - siehe Bild 6. SMD-Varianten verfügen über eine größere Kupferfläche, die sich mit dem Substrat überlappt, während NSMD-Pads (Non-Solder Mask Defined) kleinere Kupferflächen mit engeren Toleranzen aufweisen. NSMD-Pads bieten eine gleichmäßigere Lötverteilung, ermöglichen eine bessere Leiterbahnführung und reduzieren mechanische Spannungen bei Chip-Scale-Gehäusen.

Handling und Bestückung der Bauelemente können sich bei sehr kleinen Gehäusen ebenfalls als schwierig erweisen. Um Beschädigungen am freiliegenden Chip (Die) zu vermeiden, setzen Halbleiter- und Gerätehersteller auf Pick-and-Place-Maschinen sowie Vakuumgreifer. Um die Platzierungsgenauigkeit zu erhöhen, kann das Bildverarbeitungssystem der jeweiligen Pick-and-Place-Maschine entweder den Gehäuseumriss oder die einzelnen Kontaktflächen lokalisieren. Die Geometrie der Kontaktflächen ermöglicht außerdem eine automatische Ausrichtung auf den Löt-Pads. Die Entwicklung der Fertigungsmaschinen hat also durchaus mit der Größenreduzierung der elektronischen Bauelemente Schritt gehalten.

Zusammenfassung

Technologische Innovationen verläuft in Zyklen. Verbraucher verlangen immer kompaktere Produkte, mit immer mehr Funktionen. Das heißt für Entwickler: Sie müssen die teils konträren Anforderungen miteinander in Einklang bringen. Die Halbleiterindustrie hilft ihnen dabei, denn auch sie entwickelt sich ständig weiter und optimiert Gehäuse- und Feature-Optionen. Wenn die aktuelle Produktgeneration in die Läden kommt, läuft bei den Entwicklerteams bereits das Brainstorming für das nächste Top-Produkt, und der gesamte Zyklus beginnt von vorn.

Um die Miniaturisierung voranzutreiben, arbeitet TI an Entwicklungen wie eine selektive Feature-Integration, eine Optimierung der Gehäuse sowie Fortschritte auf dem Fertigungssektor, um mehr Optionen und Möglichkeiten für Entwickler zu schaffen, die an Produkten für die ständig kleiner werdende Welt arbeiten.

Autor:

Alexandra Grudzinski ist Product Marketing Engineer bei Texas Instruments