Die beste Schaltungstopologie?

Die Vorteile von Totem-Pole-PFC-Schaltungen richtig nutzen

Mit der Totem-Pole-Topologie lassen sich höhere Wirkungsgrade erzielen als mit anderen Schaltungstopologien. Doch die Ansteuerung ist komplexer als bei anderen PFC-Strukturen. Das bringt zahlreiche Herausforderungen mit sich.

Wirtschaftliche Aspekte und Umweltschutz-Erwägungen machen die Effizienz von Leistungswandler-Systemen zu einem immer wichtigeren Thema. Gemäß 80-Plus-Standard werden für Titan Wirkungsgrade von bis zu 96 % verlangt. Wenn derart hohe Wirkungsgrade erforderlich sind, stellt das für Stromversorgungs-Hersteller, die mit traditionellen Topologien arbeiten, eine echte Herausforderung dar.

Netzteile mit Ausgangsleistungen ab 75 W bestehen meist aus einer PFC-Schaltung (Power Factor Correction, Leistungsfaktor-Korrektur) und einem Gleichspannungswandler. Die PFC-Schaltung sorgt dafür, dass der Eingangsstrom den gleichen Verlauf hat wie die Eingangsspannung, sodass jeder elektrische Verbraucher wie ein ohmscher Widerstand erscheint.

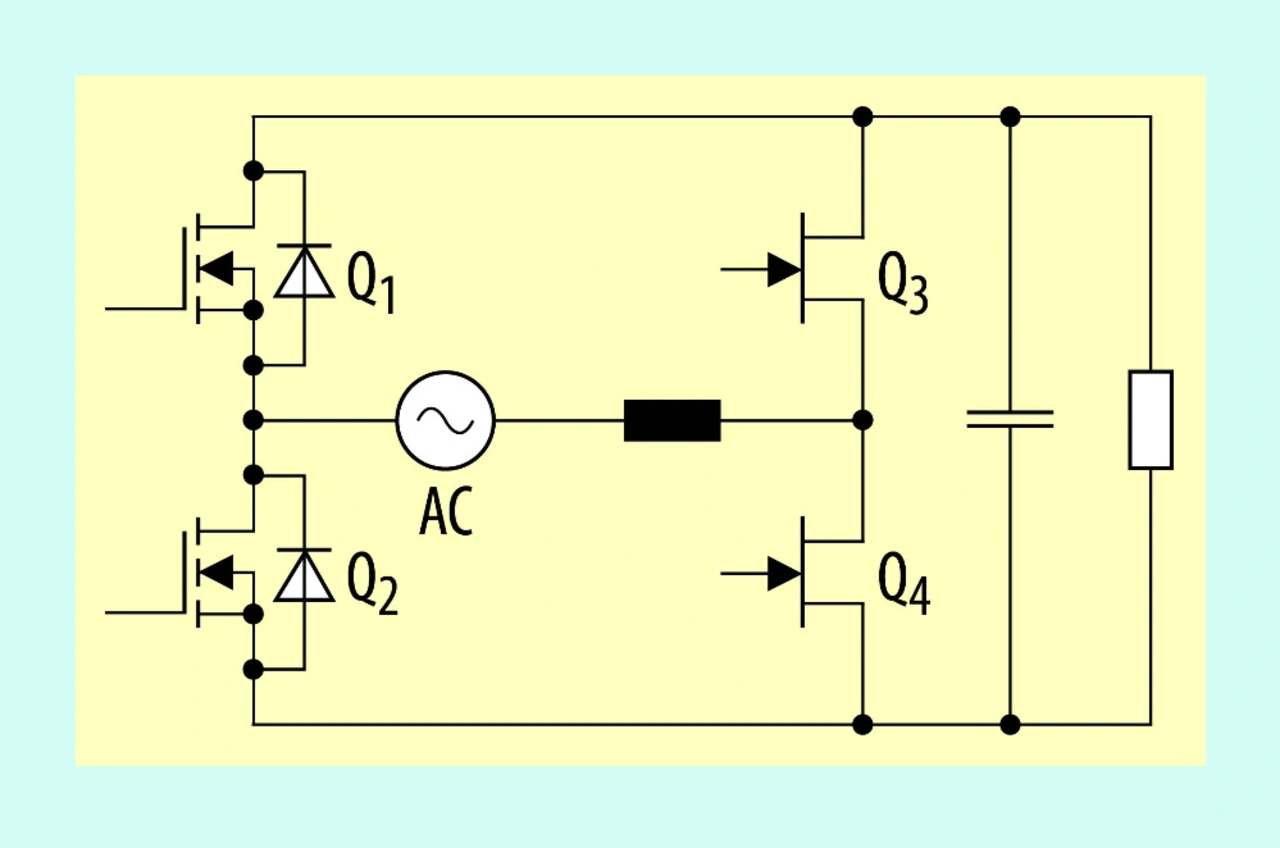

Unter den verschiedenen PFC-Topologien weckt die Totem-Pole-Architektur immer größeres Interesse, da sie den höchsten Wirkungsgrad erzielen kann. Bild 1 zeigt das Grundprinzip einer Totem-Pole-PFC-Struktur. Q3, Q4 und die Induktivität bilden in dieser Schaltung einen Aufwärtswandler.

Je nach Polarität von UAC fungieren Q3 und Q4 abwechselnd als PFC-Haupt- oder Synchronschalter. Während einer positiven Halbwelle von UAC ist Q4 der Hauptschalter und Q3 übernimmt die Funktion des Sync-FET. Die Ansteuersignale für Q3 und Q4 sind dabei komplementär: während Q4 mit dem Tastverhältnis D des Regelkreises angesteuert wird, erfolgt die Ansteuerung von Q3 mit 1 – D.

Während einer negativen Halbwelle von UAC sind die Funktionen von Q4 und Q3 vertauscht: Q3 wird zum Hauptschalter und Q4 zum Sync-FET. Dabei sind die Treibersignale für Q3 und Q4 nach wie vor komplementär, nur wird Q3 jetzt mit D, Q4 dagegen mit 1 – D angesteuert. Wegen des Sperrverzögerungs-Problems kann in einer im nichtlückenden Betrieb (Continuous Conduction Mode, CCM) arbeitenden Totem-Pole-PFC-Schaltung kein gewöhnlicher MOSFET eingesetzt werden.

Stattdessen müssen für Q3 und Q4 Galliumnitrid-FETs gewählt werden, bei denen das Sperrverzögerungs-Phänomen nicht auftritt. Zur weiteren Verbesserung des Wirkungsgrads sind zu den standardmäßigen MOSFETs Q1 und Q2 Dioden parallelgeschaltet.

Derzeit sind keine analogen Regler für Totem-Pole-PFC-Schaltungen am Markt erhältlich. Digitale Regler sind mit ihrer Flexibilität und ihren integrierten digitalen Leistungs-Peripheriebausteinen gut für diese Topologie geeignet. Allerdings kann die traditionelle digitale Ansteuermethode bei einer Totem-Pole-PFC-Schaltung nicht direkt angewandt werden, sodass spezielle Ansteuer-Algorithmen entwickelt werden müssen.

Denn die Ansteuerung einer Totem-Pole-PFC-Schaltung gestaltet sich deutlich komplexer als die einer traditionellen PFC-Struktur. Wegen des fehlenden Brückengleichrichters bringen der bidirektionale Strom in der Induktivität und der Funktionswechsel zwischen Haupt- und Sync-Schalter bei einer Totem-Pole-PFC-Schaltung zahlreiche Herausforderungen mit sich.

Stromspitze beim AC-Nulldurchgang

Ein Problem bei einer im nichtlückenden Betrieb arbeitenden Totem-Pole-PFC-Schaltung ist, dass der Eingangsstrom beim Nulldurchgang der Wechselspannung hohe Spitzen aufweist. Dies ist ein prinzipbedingtes und sehr kompliziertes Phänomen der Totem-Pole-PFC-Topologie.

Zu den Schaltungs-Charakteristika, die diese Spitzen hervorrufen können, gehören die Einschaltabfolge der Schalter, ein langsames Sperrverzögerungs-Verhalten der Body-Dioden von Q1 und Q2, hohe COSS-Werte von Q1 und Q2, ein plötzliches Vertauschen des PWM-Signals zwischen Q3 und Q4 usw.

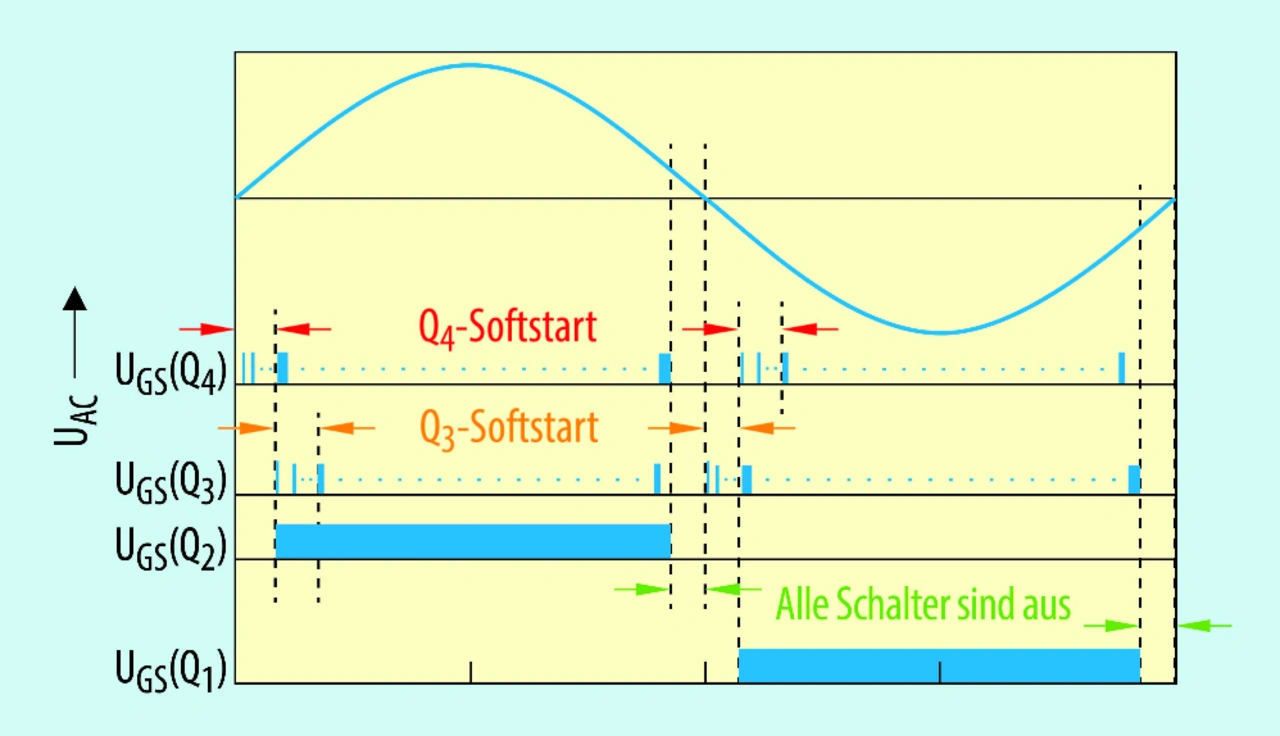

Deutlich reduzieren lassen sich die Stromspitzen, indem man die Schalter in einer ganz bestimmten Reihenfolge einschaltet und am Haupt- und Sync-FET einen Softstart-Mechanismus anwendet (Bild 2) [1]. Das Resultat dieser Maßnahmen ist eine signifikante Verbesserung des THD-Werts, d.h. des Oberschwingungsgehalts.

Detektion des AC-Nulldurchgangs

Wie bereits erwähnt, hängt die Funktion von Q3 und Q4 von der Polarität von UAC ab. Q3 und Q4 tauschen ihre Funktion als Haupt- oder Synchronschalter unmittelbar nach dem AC-Nulldurchgang. Dabei ändert sich das Tastverhältnis des einen Schalters abrupt von nahezu 100 % auf Null, während es beim jeweils anderen Schalter genau umgekehrt ist.

Ein Fehler bei der Detektion des Nulldurchgangs von UAC, wie er typischerweise durch Störungen oder eine Spannungsspitze verursacht wird, wäre höchst problematisch. Wenn beispielsweise während der positiven Halbwelle von UAC eine Störgröße den Regler so reagieren lässt, als hätte die negative Halbwelle von UAC begonnen, wird der Schalter Q3 mit einem Tastverhältnis von fast 100 % beaufschlagt.

Da Q2 in diesem Fall noch eingeschaltet wäre, würde der Ausgangsbus zur Masse kurzgeschlossen. Das Resultat wäre eine Stromspitze von enormer Höhe, die Schäden an der Hardware verursachen könnte. Eine Möglichkeit, den AC-Nulldurchgang zuverlässig zu erkennen, funktioniert folgendermaßen:

- Wird eine Änderung der Polarität von UAC erkannt, schaltet der Regler aus Sicherheitsgründen alle Schalter ab.

- Erkennt der Controller mehrere Male hintereinander (z. B. dreimal) eine Änderung der Polarität von UAC, kann davon ausgegangen werden, dass tatsächlich eine Polaritätsänderung erfolgt ist. Daraufhin leitet der Controller eine spezielle Softstart-Sequenz ein, wie sie in [1] beschrieben ist.

Mit diesen Vorsichtsmaßnahmen lässt sich praktisch ausschließen, dass es durch Störgrößen oder Spannungsspitzen zu einer fehlerhaften Erkennung des Nulldurchgangs von UAC kommt.

Vor dem Anlaufen einer PFC-Schaltung sind der Spannungs- und der Stromregelkreis abgeschaltet, und ihre Ausgänge auf Null. Beim Anlaufen der PFC-Schaltung starten beide Regelkreise einen Hochfahr-Vorgang. Die Integratoren beider Regelkreise beginnen sich aufzufüllen, bis der erforderliche Sollwert (Tastverhältnis) erreicht ist. Deshalb ist am Beginn des Softstart-Vorgangs das Tastverhältnis D klein, während 1 – D entsprechend groß ist.

Wenn der Sync-Schalter in diesem Moment mit 1 – D einschaltet, wird die Ausgangsspannung entladen, was eine negative Stromspitze bewirkt. Zur Vermeidung dieses Problems sollte der Sync-Schalter abgeschaltet bleiben, bis der PFC-Softstart abgeschlossen ist und die Schaltung einen statischen Zustand erreicht hat.

- Die Vorteile von Totem-Pole-PFC-Schaltungen richtig nutzen

- Stromreferenz und Polarität des Regelkreises