Zonenbasierte Power-Architektur

Die Ansteuerung kapazitiver Verbraucher

Halbleiterbasierte Smart-Fuse-Lösungen laufen traditionellen Schmelzsicherungen in Automotive-Anwendungen den Rang ab. Dies ist der deutlich besseren Zeit-Strom-Kennlinie sowie der Tatsache zu verdanken, dass sie softwaremäßig rückstellbar sind. Doch es gibt auch Herausforderungen zu lösen.

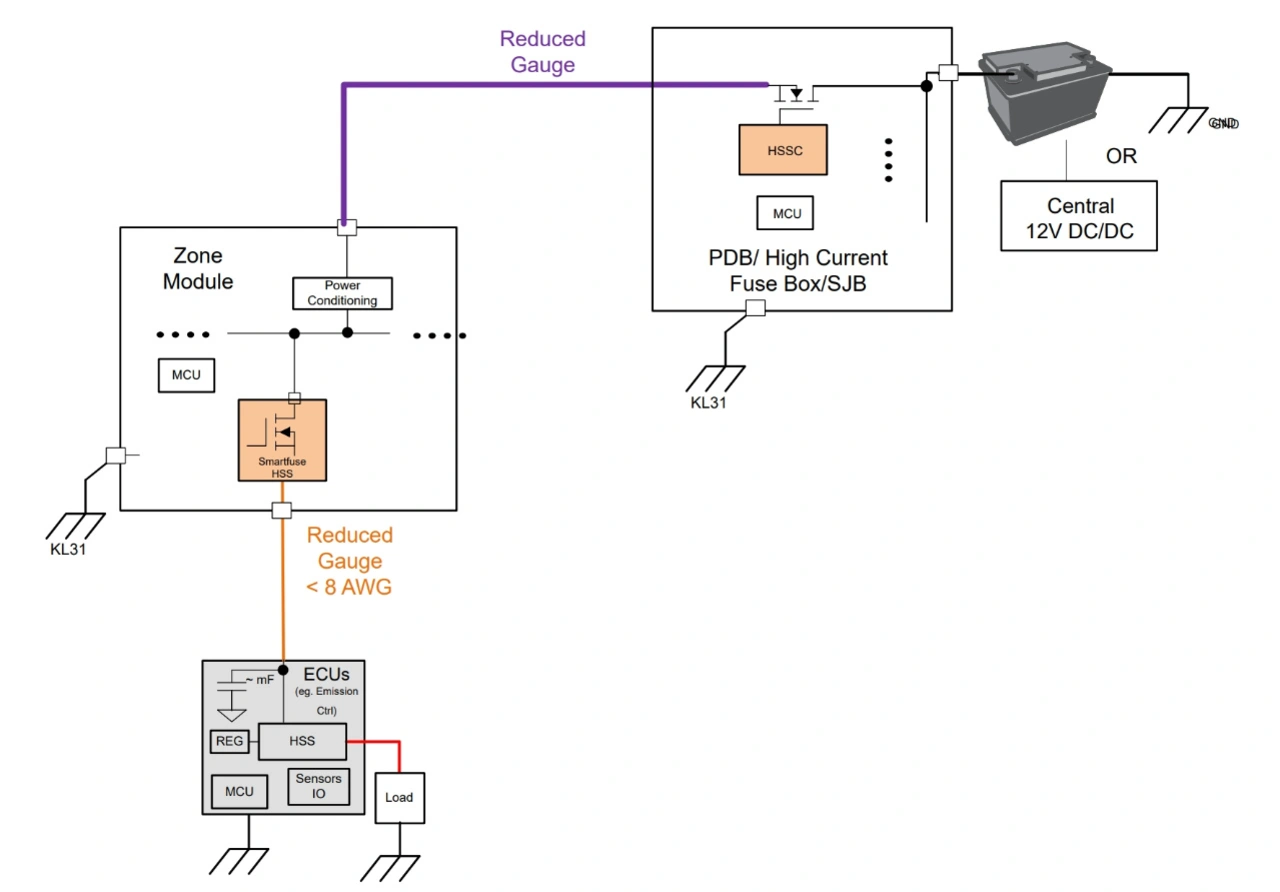

Die Umstellung von domänen- auf zonenbasierte Architekturen in der Kfz-Elektronik bringt tiefgreifende Änderungen für die Stromversorgung im Automobilbereich mit sich. Die traditionell für den Stromkreisschutz eingesetzten Schmelzsicherungen werden dabei durch halbleiterbasierte Lösungen ersetzt.

Diese bieten Vorteile wie etwa eine geringere Variabilität der Zeit-Strom-Kennlinie, was potenziell eine Verringerung des Leiterquerschnitts und damit des Gewichts und der Kosten der Kabelbäume ermöglicht. Da Halbleiterschalter zudem aus der Ferne rückstellbar sind, müssen sie nicht an leicht zugänglichen Stellen platziert werden und bieten damit Gelegenheit, die Kabel zwischen Stromquelle und Verbraucher zu verkürzen (Bild 1).

Bei der Verwendung von Halbleiter-Bauelementen als intelligente Leitungsschutzschalter ergeben sich verschiedene Herausforderungen. Dazu gehört das Absenken der Ruhestromaufnahme im eingeschalteten Zustand und das korrekte Einschalten der Ausgänge in Verbindung mit großen Lastkapazitäten. Denn die von den Halbleiterschaltern angesteuerten elektronischen Steuergeräte (Electronic Control Units, ECUs) können Eingangskapazitäten zwischen 47 µF und 5 mF aufweisen, und die erforderlichen Start-up-Zeiten der ECUs liegen je nach Art und Anzahl der an den jeweiligen Ausgang einer Power Distribution Box (PDB) angeschlossenen ECUs zwischen unter 1 ms und bis zu 50 ms.

Dieser Artikel beschreibt verschiedene Methoden, die ECU-Eingangskapazitäten mit den MOSFET-Schaltern innerhalb der vorgegebenen Start-up-Zeit des jeweiligen Steuergeräts zu laden und damit eine der primären Design-Herausforderungen im Zusammenhang mit zonenbasierten Architekturen zu meistern.

Kontrolle der Spannungs-Anstiegsrate

Bei der Methode der Kontrolle der Spannungsanstiegsrate wird mithilfe eines Kondensators C zwischen Gate und GND die Anstiegsgeschwindigkeit der Ausgangsspannung künstlich herabgesetzt, um den Inrush-Strom zu begrenzen (Bild 3). Mit den beiden folgenden Gleichungen lassen sich der Inrush-Strom und die Verlustleistung in der Start-up-Phase berechnen:

Da der MOSFET hier im Sättigungsbereich arbeitet, sollte der Inrush-Strom so niedrig sein, dass die in der Start-up-Phase entstehende Verlustleistung innerhalb des sicheren Betriebsbereichs (Safe Operating Area, SOA) des MOSFET bleibt. MOSFETs verkraften mehr Energie (½ COUT∙VIN²), wenn die anfallende Verlustleistung reduziert und über einen längeren Zeitraum verteilt wird. Das Inrush-Intervall muss folglich zeitlich gestreckt werden, um größere Lastkapazitäten zu unterstützen.

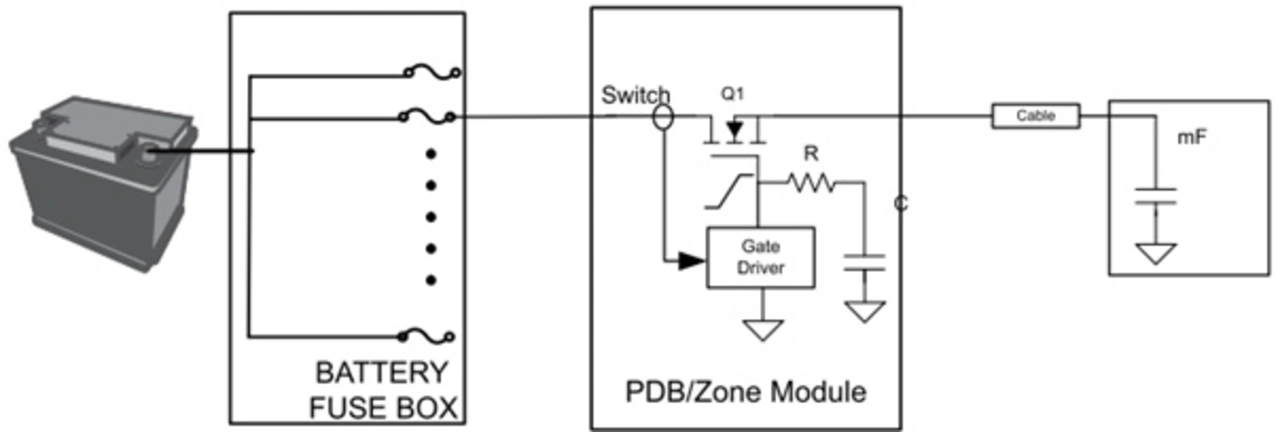

Diese Methode (Bild 2) bietet sich immer dann an, wenn eine geringe Ladegeschwindigkeit gefordert ist (z. B. 5 mF innerhalb von 50 ms), allerdings muss beim Design stets eine Abwägung zwischen COUT, dem SOA des FET, der Ladezeit und der Betriebstemperatur getroffen werden. Zum Beispiel dauert das Aufladen von 5 mF an 12 V bei einer Begrenzung des Inrush-Stroms auf 1,5 A immerhin 40 ms, wenn der High-Side-Schaltregler TPS1211-Q1 von TI als Gatetreiber eingesetzt wird. In [1] ist eine Prozedur zum Überprüfen des SOA des FET während der Start-up-Phase bei Anwendung dieser Methode beschrieben, während es sich bei [2] um ein Online-Tool zum Abschätzen der SOA-Reserven für einen bestimmten MOSFET handelt.

Paralleler Precharge-Pfad

Das Verfahren mit paralelem Precharge-Pfad wird üblicherweise in Hochstrom-Designs mit parallelgeschalteten FETs genutzt, die einen zusätzlichen Gatetreiber zum Ansteuern eines Precharge-FETs benötigen. Mithilfe von Gleichung 3 lässt sich der Precharge-Widerstand (Rpre-ch) berechnen, der den Inrush-Strom auf einen bestimmten Wert begrenzt:

Da der Precharge-Widerstand die gesamte Leistung während der Start-up-Phase verkraften muss, sollte er für die durchschnittliche und die maximale Verlustleistung dimensioniert sein, siehe Gleichung 4 bzw. Gleichung 5.

Mit dieser Methode ist ein schnelles Laden des Ausgangs möglich, allerdings fällt der Precharge-Widerstand in diesem Fall recht sperrig aus. Zum Beispiel würde das Aufladen von 5 mF auf 12 V in 10 ms einen für 36 W dimensionierten Precharge-Widerstand von 0,4 Ω erfordern, der allerdings für eine Spitzenleistung von 360 W ausgelegt sein muss. Ein klobiger Drahtwickelwiderstand ist hier somit unabdingbar, sodass diese Lösung für viele Anwendungen nicht in Frage kommt – besonders dann, wenn mehrere Kanäle auf einer Leiterplatte untergebracht sind.

Automatisches, PWM-basiertes Laden der Eingangskapazität

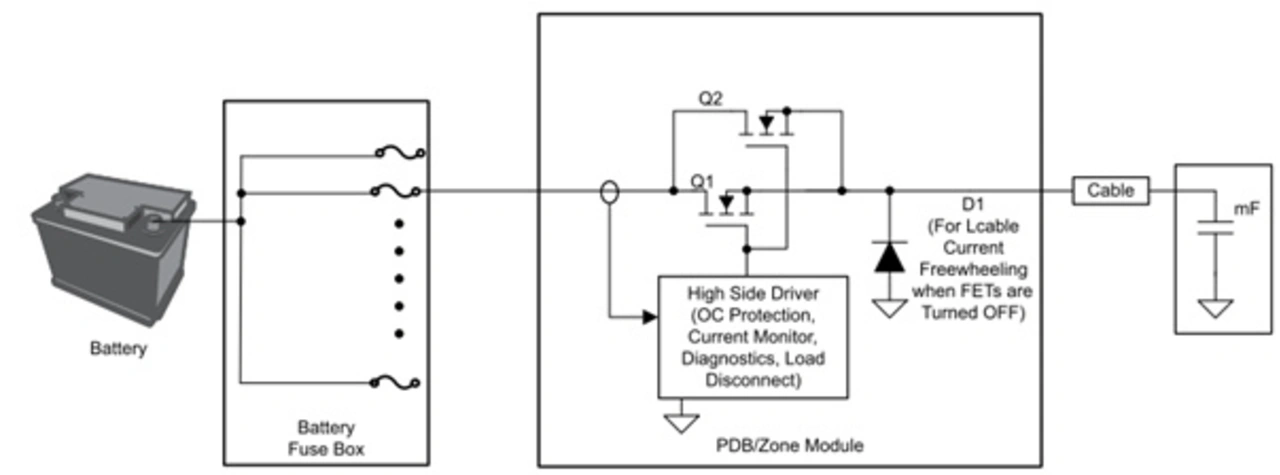

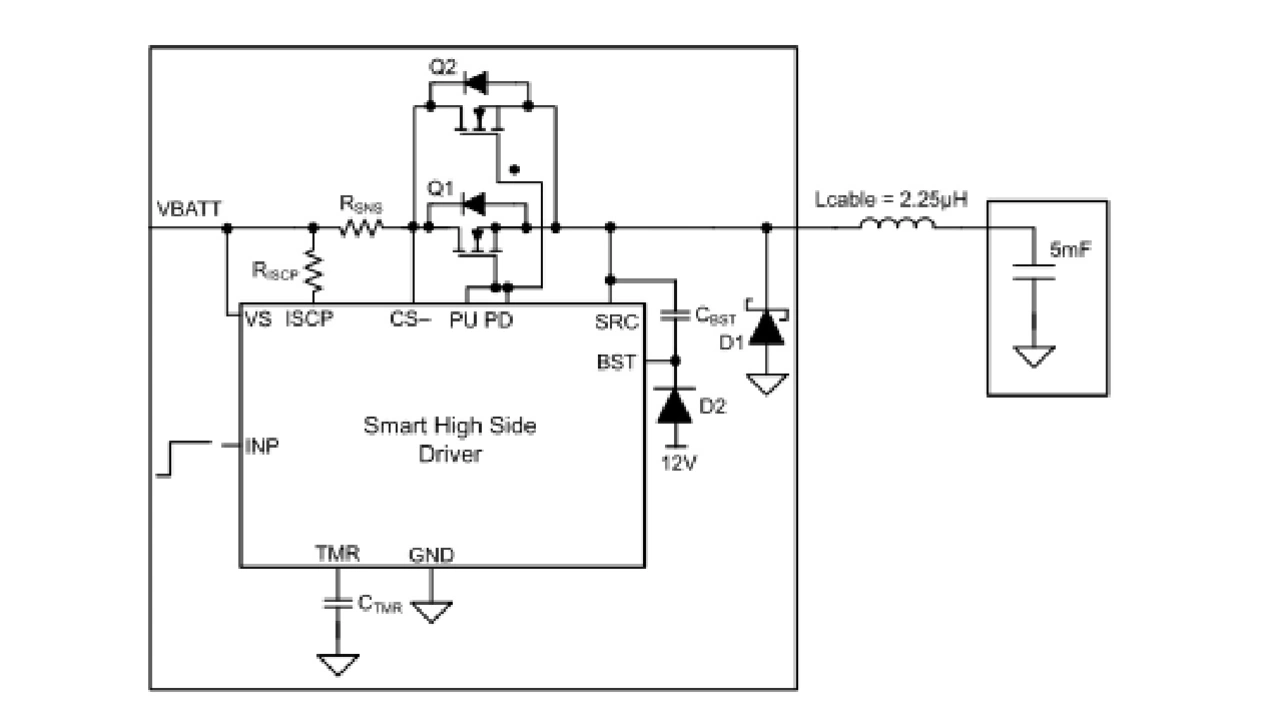

Wie in Bild 3 zu sehen ist, sind die High-Side-Treiberausgänge der Leiterplatte über Kabel, die zwischen einem und mehrere Meter lang sind, mit den jeweiligen ECUs verbunden. Ein für 50 A ausgelegter Kabelbaum hat beispielsweise einen Widerstand von 2 mΩ/m und eine Induktivität von 1,5 µH/m.

Die zum Systemdesign gehörende Diode D1 dient als Freilaufdiode für die von der Kabelinduktivität verursachten Ströme. Die High-Side-Treiber verfügen über Ausgänge mit hoher Treiberstärke, die parallelgeschaltete FETs mit kurzen Ein- und Abschaltzeiten (<1 µs) ansteuern können und zusätzlich für den erforderlichen Überstrom- und Kurzschlussschutz sorgen. Die parasitären Effekte des Kabels, die Diode D1 und die High-Side-MOSFETs bilden gemeinsam eine typische Abwärtsregler-Konfiguration.

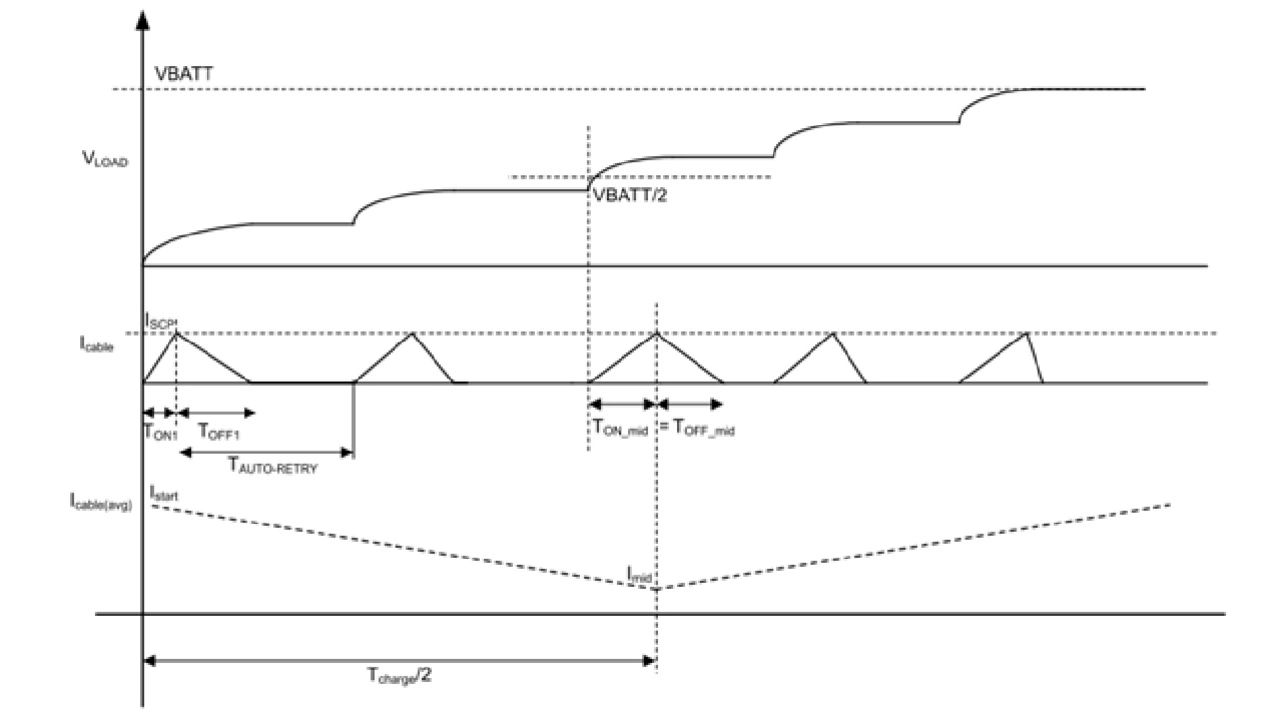

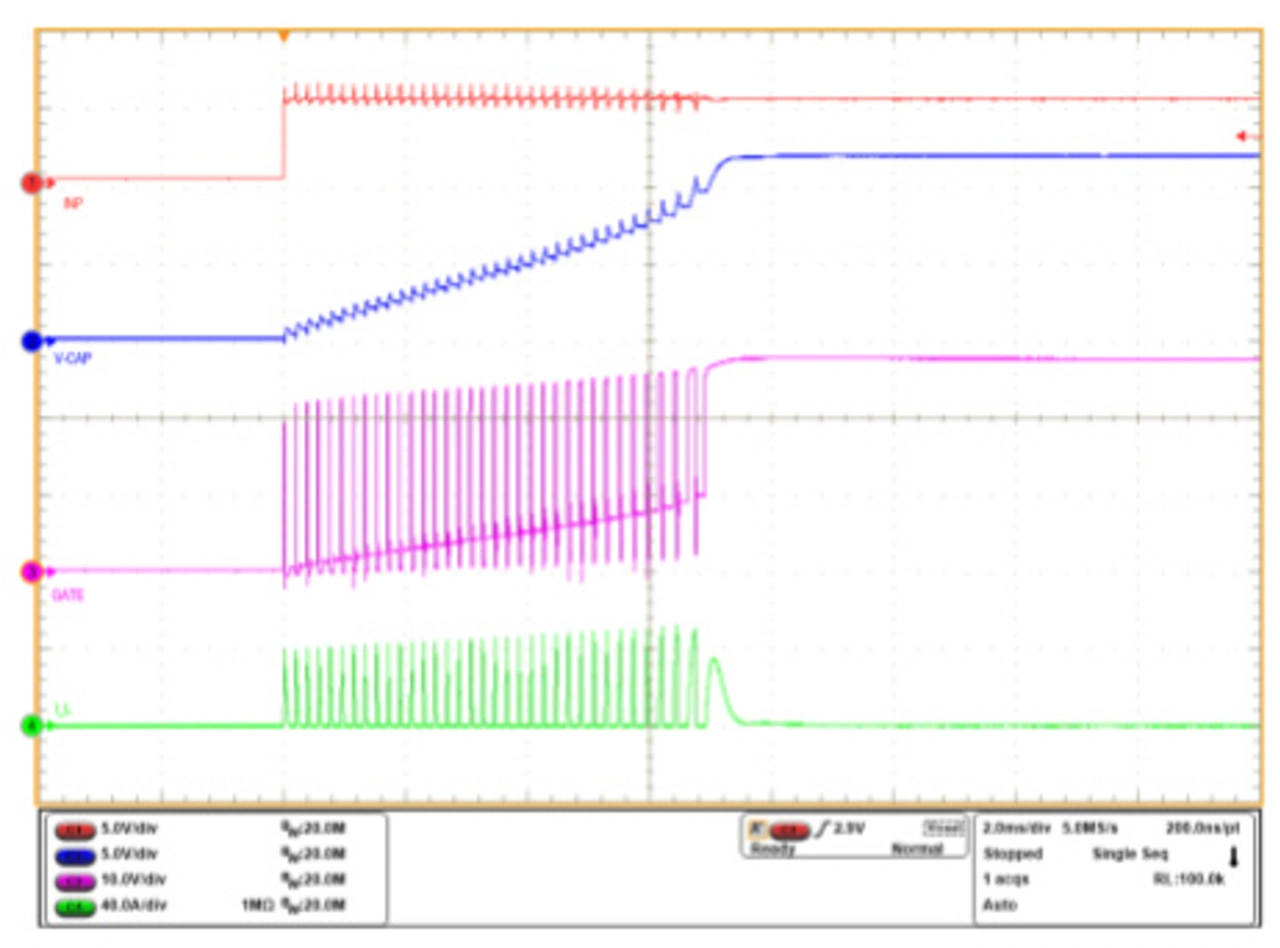

Der Ablauf des Ladevorgangs ist aus Bild 4 zu entnehmen: Während der Anlaufphase fließt ein Inrush-Strom in die ungeladenen Ausgangskapazität und löst ein Kurzschluss-Ereignis aus, sobald er die Ansprechschwelle des Kurzschlussschutzes (ISCP) erreicht. Der High-Side-Treiber schaltet daraufhin ab und unternimmt nach einer bestimmten Wartezeit (TAUTO-RETRY) einen Wiedereinschaltversuch. Dieser Zyklus setzt sich so lange fort, bis die Ausgangskapazität vollständig geladen ist und der Treiber in den normalen Betrieb übergeht.

Die beiden Variablen ISCP und TAUTO-RETRY, die bei diesem Verfahren eine wichtige Rolle spielen, müssen abhängig von der Eingangsspannung (VIN), der Lastkapazität und der gewünschten Ladezeit für den High-Side-Treiber festgelegt werden. Ein höher angesetzter ISCP-Grenzwert oder eine kürzere TAUTO-RETRY-Phase erlauben ein schnelleres Laden des Ausgangs, sodass die Lösung für beliebige Lastkapazitäten eingesetzt werden kann.

Reizvoll an dieser Methode ist, dass sie die bestehenden Ressourcen eines High-Side-Treibersystems (nämlich die Kabelinduktivität und die Diode D1) nutzt und durch Takten der High-Side-MOSFETs eine effiziente Lademethode implementiert. Anders als traditionelle Verfahren ist diese Lösung außerdem nicht vom SOA der FETs abhängig und benötigt weder einen sperrigen Precharge-Widerstand noch einen Precharge-FET oder einen Treiber. Stattdessen bedient sie sich des eingebauten Kurzschlussschutzes des High-Side-Treibers und arbeitet autonom, ohne dass irgendwelche externen Steuersignale oder komplexen Algorithmen erforderlich sind.

Designüberlegungen und Testergebnisse

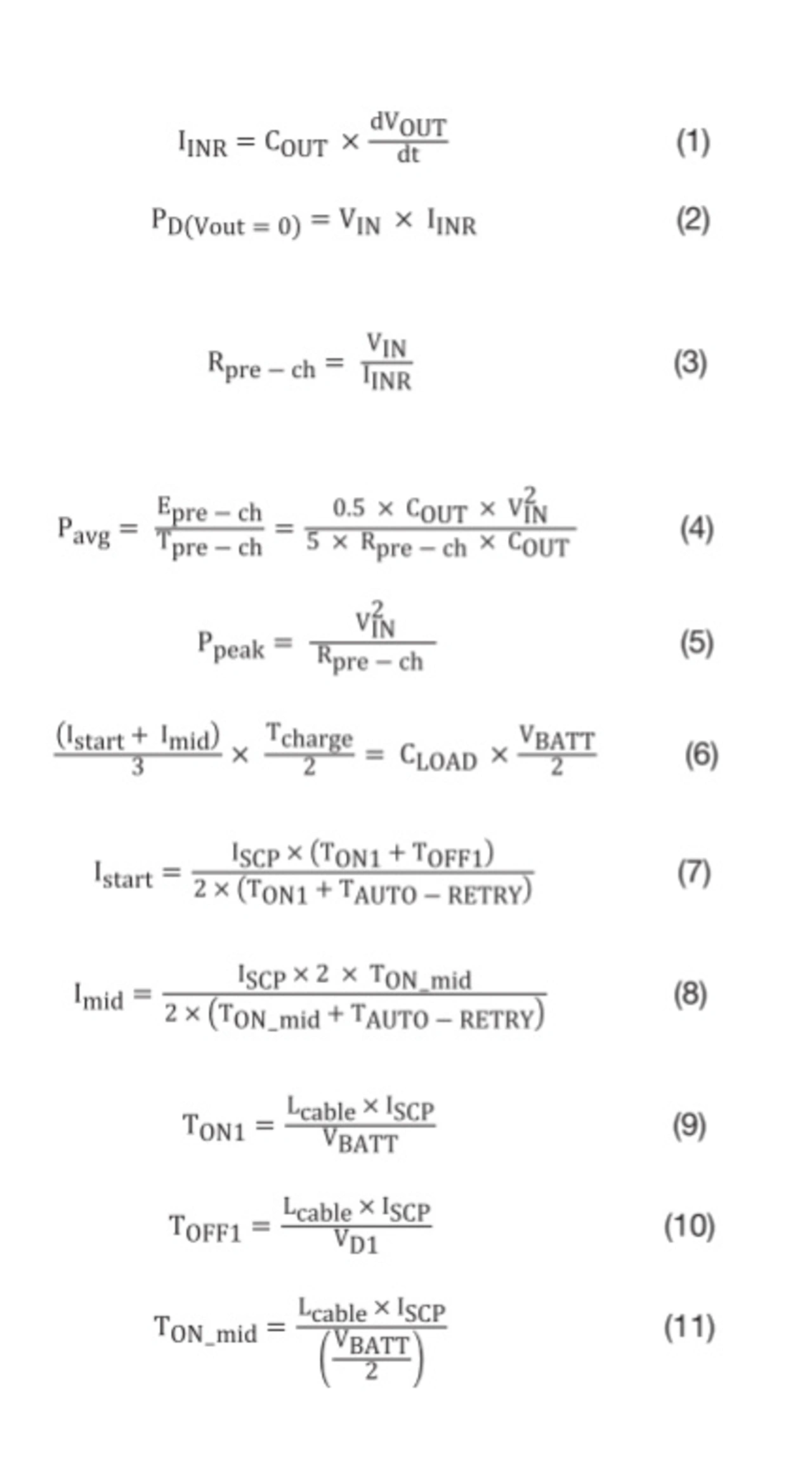

Für ein Designbeispiel mit einem Laststrom von 50 A gilt:

- Batteriespannung (VBATT): 12 V

- Lastkapazität (CLOAD): 5 mF

- Induktivität von 1,5 m Kabel: 2,25 µH

- Ladezeit (Tcharge): 10 ms

- Spannungsabfall an der Freilaufdiode (VD1): 0,7 V

Auf der Basis dieser Daten müssen die Werte von ISCP und TAUTO-RETRY festgelegt werden. ISCP wird in der Regel 20 % über dem maximalen Laststrom angesetzt, also bei 50 A ∙ 1,2 = 60 A. Zum Berechnen von TAUTO-RETRY wird nun anhand von Bild 5 die Strom-Spannungs-Kennlinie des Kondensators bei Tcharge/2 genutzt, um Gleichung 6 zu erhalten. Darin werden die Bedingungen aus Gleichung 7 und Gleichung 8 genutzt.

Die Zeitintervalle TON1, TOFF1 und TON_mid lassen sich mithilfe der Gleichungen 9 bis 11 berechnen.

Setzt man nun die bekannten Werte für VBATT, Lcable, ISCP, VD1 and CLOAD ein und löst nach TAUTO-RETRY auf, so errechnet sich eine Zeitspanne von <200 µs zum Erzielen einer Ladezeit von 10 ms. Bild 5 stellt die zum Laden einer Lastkapazität von 5 mF dienende Schaltung mit dem High-Side-Treiber TPS1211-Q1 dar. Der mit 180 µs angesetzte Wert von TAUTO-RETRY ergibt eine Ladezeit von 7 ms, wie aus Bild 6 zu entnehmen ist.

Literatur

[1] Rogachev, Artem. 2014. »Robust Hot Swap Design.« Texas Instruments Application Report, Literature No. SLVA673A, April 2014.

[2] FET SOA Margin Calculator for dv/dt-Based Startup

Die Autoren

Dilip Jain

ist Systems Manager, Power Switches bei Texas Instruments.

Rakesh Panguloori

ist Applications Manager, Power Switches bei Texas Instruments.