Entwicklungszeit verringern

10 Schritte zum erfolgreichen SoC-Design

Chips werden immer komplexer – das erfordert immer größere Teams von Ingenieuren. Um zu gewährleisten, dass die Entwicklungszeit eines Chips nicht stetig ansteigt, investiert Sondrel viel in Forschung und Entwicklung und gibt 10 Tipps, wie eine erfolgreiche Entwicklung gelingt.

Sondrel möchte neue Modellierungswerkzeuge und Abläufe entwickeln, die die Produktion von ASICs vereinfachen. Hierzu hat der Hersteller zehn Schritte identifiziert, die für den Entwurf einer SoC-Architektur essenziell sind. Insgesamt lautet die Strategie für den erfolgreichen Entwurf einer SoC-Architektur:

- Aufteilung des Problems in Stufen nach dem »Teile-und-Herrsche«-Verfahren.

- Mit zunehmendem Detaillierungsgrad: weniger Optionen zur Untersuchung in Betracht ziehen.

- Den Vorgang der Modellierung zur Beantwortung spezifischer Fragen verwenden.

- Im Verlauf des Prozesses auf bestimmte Ressourcen fokussieren. (Keine Simulationszeit verschwenden, Datenmenge sowie Simulationsgröße und -anzahl reduzieren)

- Probleme nach einer logischen Reihenfolge abarbeiten, um die Analyse von Ursache und Wirkung zu vereinfachen und die erforderlichen Iterationen zu reduzieren.

- Iterieren, um Probleme zu identifizieren und zu beheben, bevor mit dem Entwurf weitergemacht wird.

- Einen Kompromiss zwischen Genauigkeit und Geschwindigkeit finden.

Jobangebote+ passend zum Thema

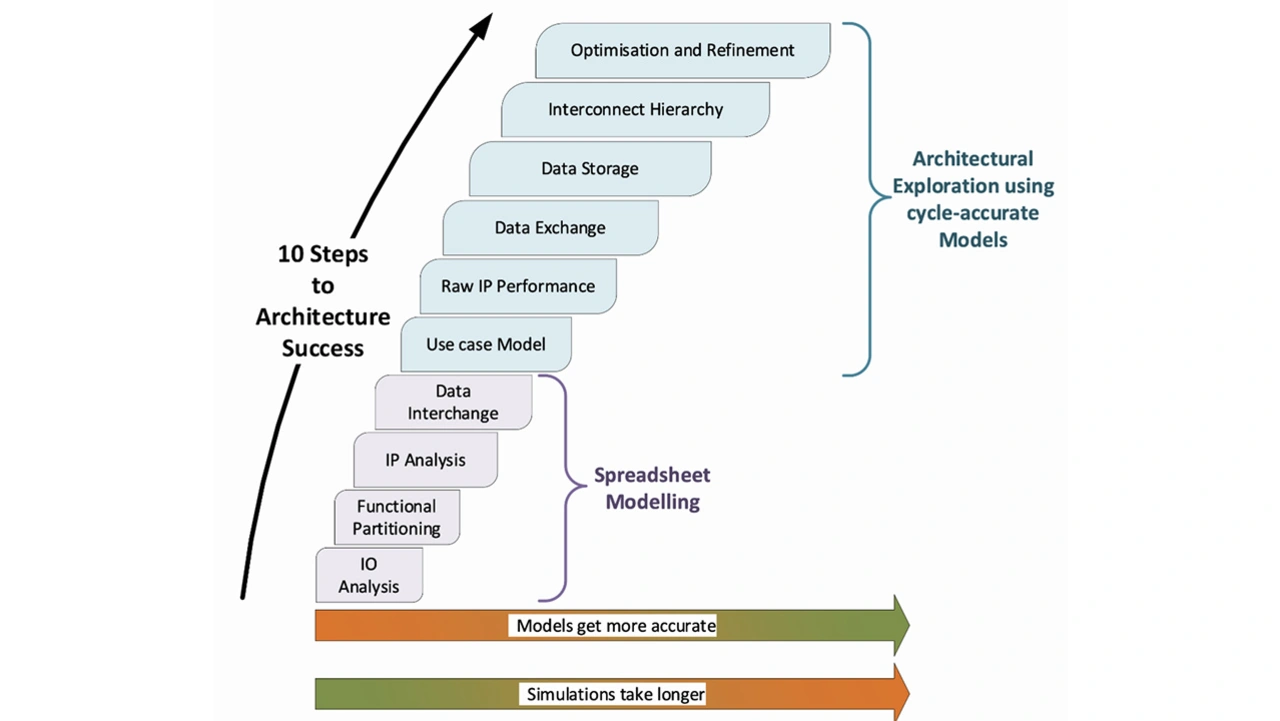

Wenn diese Strategie angewandt befolgt wird, sind in Summe 10 Schritte auszuführen, um erfolgreich ein SoC zu designen. Die 10 Schritte (Bild) lauten wie folgt:

- Daten und I/O-Beschränkungen wie Latenz, Timing und Formatierung bestimmen. Buffer-Anforderungen im Datenblatt festhalten.

- Teilaufgaben der Verarbeitung bestimmen und Teile des SoC in gemeinsame Funktionsteile gruppieren.

- Identifizieren, welche IP-Blöcke man von Drittanbietern benötigt, um die Schritte eines Algorithmus auszuführen. Wie viel Speicher- und Rechenleistung wird benötigt, die in die Modellierungsumgebung eingespeist werden kann. So erhält man eine genaue Darstellung dessen wie alle IP-Blöcke arbeiten.

- Abdecken der Methode des Datenaustauschs zwischen Teilen eines Algorithmus. Zum Beispiel On-Chip-SRAM oder externer DDR-Speicher sowie FIFO, die kleine Speicherbereiche auf dem Chip sind. Die Entscheidung zwischen SRAM und DDR hängt von der Größe der Daten ab und davon, wie oft auf sie zugegriffen werden muss, wobei große Datenmengen in den externen Speicher und kleine Datenmengen in SRAM oder FIFO gehen.

- Hierbei wird eine Software-Darstellung der verschiedenen Phasen mit der konzeptionellen Ansicht des Algorithmus und den tatsächlichen Simulationsobjekten erstellt. Sie entsprechen den verschiedenen Software-Phasen des Algorithmus. Diese erfordern Einstellungen wie Latenz und Verarbeitungszyklen und werden durch als Kanäle bezeichnete Objekte ergänzt, die die Abfolge angeben.

- Nachdem alle Simulationsobjekte für den vollständigen Algorithmus erstellt wurden, können Simulationen durchgeführt werden, um zu sehen, ob die richtige Reihenfolge des Algorithmus erfasst wurde.

- Verwenden von Modellen der Hardware-Plattform mit VPUs (Virtual Processor Units), auf denen die Software aus Schritt 5 ausgeführt wird – jeweils mit eigenem lokalen Speicher. Hier kann das Schnittstellentiming berücksichtigt und Kommunikationsdomänen mit ihren zugewiesenen Kanälen definiert und ausgewertet werden. Außerdem kann die Konfiguration der VPUs auf ihre Richtigkeit überprüft werden.

- Man nimmt den Speicher, der jeder VPU zur Verfügung steht, und stellt ihn so dar, als sei er über einen gemeinsamen Speicher-Controller mit dem externen Speicher verbunden. Dies ergibt eine genauere Darstellung der Konnektivität aller VPUs und Speicher im endgültigen System.

- Hinzufügen der Interconnect Fabric. Anstelle der direkten Verbindungen zwischen den VPUs und dem Speicher-Controller werden diese durch die Interconnect Fabric ersetzt und die Auswirkungen auf das Timing und die Leistung bewertet. Die Interconnect Fabric wird dann so angepasst, dass sie die geforderte Leistung erbringt, wobei die vorangegangenen Schritte erneut durchgeführt werden, um die gewünschten Ergebnisse zu erzielen.

- Durch einfaches Anpassen der Einstellungen können verschiedene Simulationen durchgeführt werden. So können Engpässe ermittelt werden und man kann herausfinden, welche Einschränkungen im System bestehen und welche Parameter angepasst werden sollten. So kann man den Durchsatz verbessern und die Latenzzeit des SoC verringern. Die Ausführung der Simulationen dauert nur wenige Minuten bis eine Stunde, so dass sich Varianten einfach und schnell testen lassen.

Hierbei ist noch zu ergänzen, dass die ersten vier Schritte auf Papier oder in einer Kalkulationstabelle durchgeführt werden können. So kann der Entwickler die Eingangs- und Ausgangsdatenströme in das SoC und deren Eigenschaften besser verstehen. Die letzten sechs Schritte sind jedoch simulationsbasiert auszuführen. Wobei Software-Modelle erstellt und Simulationen durchgeführt werden, um Ergebnisse zu generieren, die Informationen über das System liefern.