Leistungs-MOSFETs

SiC aus der CMOS-Fab

Fortsetzung des Artikels von Teil 1

SiC-MOSFET-Prozesse testen

Um die Produktionskosten für SiC-MOSFETs zu reduzieren, müssen eine hocheffiziente Bearbeitung und ausreichende Designmargen in einem ausgewogenen Verhältnis stehen, um Bereiche wie die Epitaxialdotierungstoleranz bei Siliziumkarbid anzupassen.

Jobangebote+ passend zum Thema

Um diese Balance zu testen, ist die Verteilung der Durchbruchspannung einer großen Anzahl an Bauteilen von mehreren Wafern aus verschiedenen Fertigungslosen zu prüfen. Die Analyse sollte zeigen, dass der Prozess ausreichenden Spielraum für einen weiten Bereich an Epitaxialdotierungsvariationen bietet.

Da 100-mm-SiC-Wafer häufiger genutzt werden als solche mit 150 mm Durchmesser ist auch der Dioden-Leckstrom der hergestellten Bauteile zu testen, um Defektdichte und Bauteileertrag zu bewerten. Das Ziel sollte dabei ein Ertrag sein, der über 90 % liegt!

Die Bauteilstabilität und Widerstandsfähigkeit von SiC-MOSFETs führten in der Vergangenheit zu Bedenken, deshalb sollten verschiedene Tests durchgeführt werden, um die Integrität des Gate-Oxids, die parametrische Stabilität und Robustheit zu prüfen.

TDDB-Messungen (Time-dependent Dielectric Breakdown) der MOS-Kondensatoren wurden von Drittanbietern bei hohen Temperaturen durchgeführt, um die Lebensdauer der Bauteile unter erhöhter Temperatur (bis zu +300 °C) und einem Oxidfeld von über 9 MV/cm vorherzusagen [2]. Diese Tests prognostizierten eine Lebensdauer von mehr als hundert Jahren. Zudem haben QBD-Messungen (Charge-to-breakdown) konsistente Ausbeutewerte von über 10 C/cm² ohne gekrümmtes Ende ergeben. Dies deutet darauf hin, dass keine extrinsischen Defekte vorhanden sind, die zu vorzeitigem Ausfall führen würden.

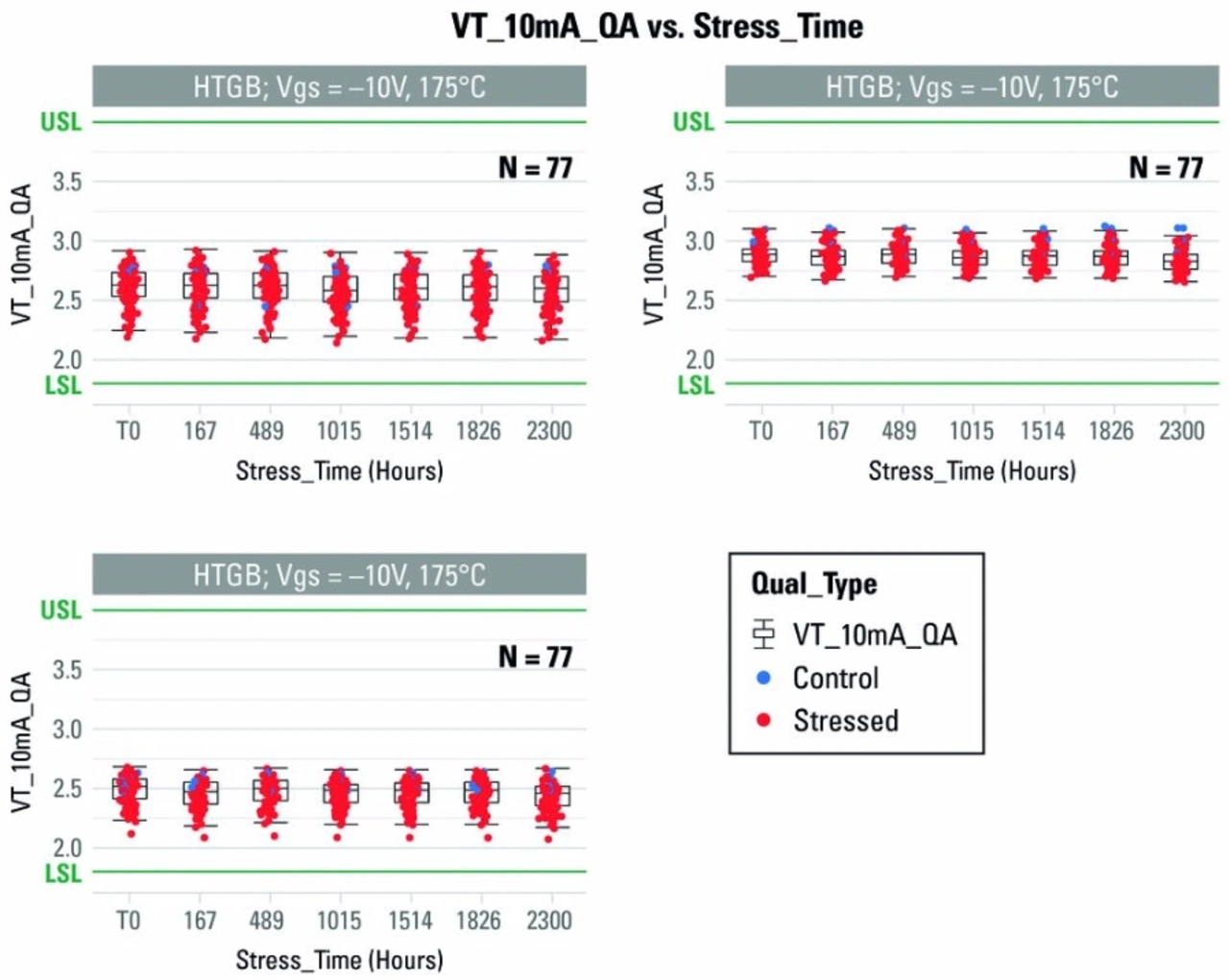

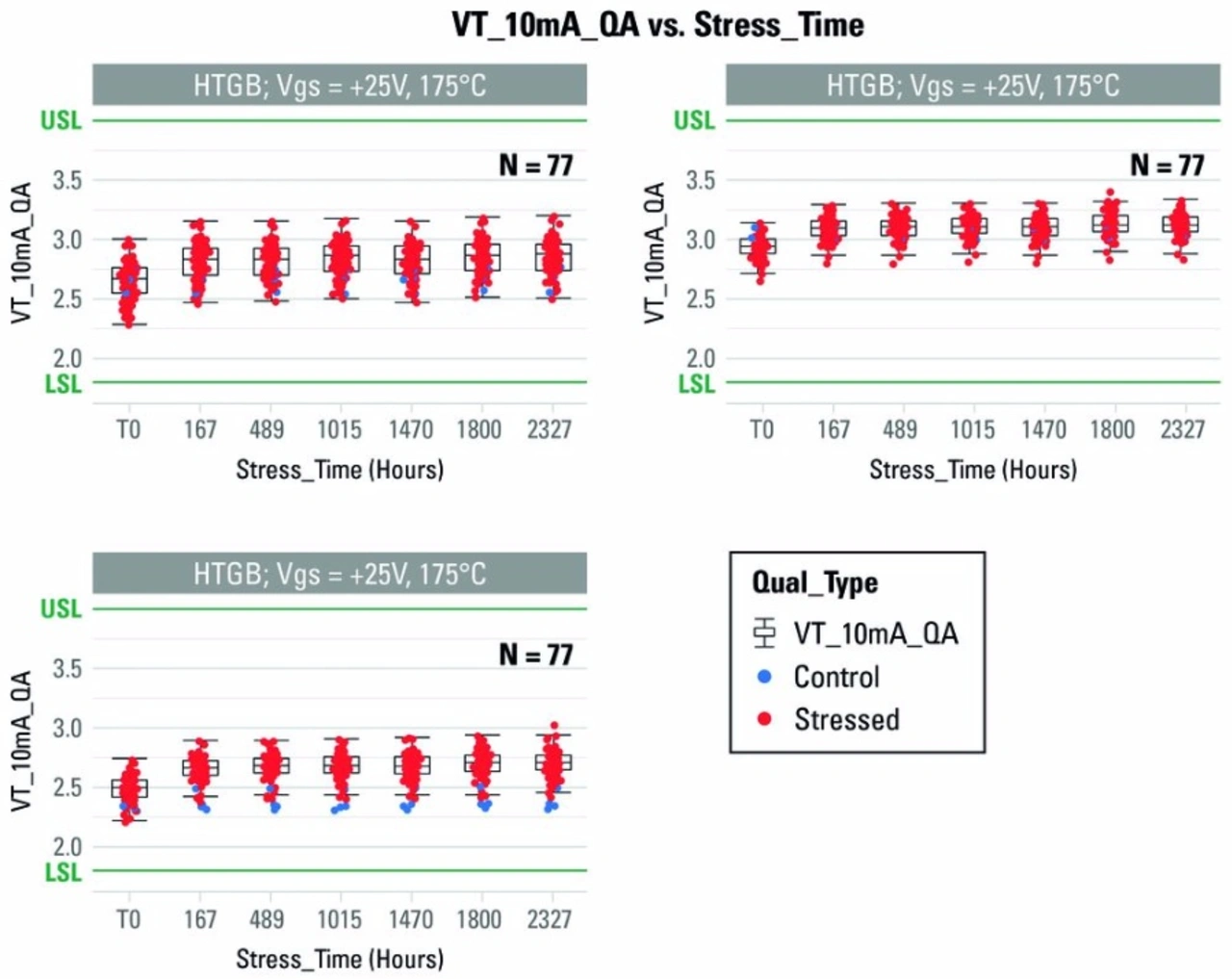

In den Bildern 1 und 2 sind HTGB-Tests (High Temperature Gate Bias) bei einer Gate-Source Spannung UGS von –10 V und +25 V zu sehen. Dies belegt die Stabilität der Schwellenspannung. Die Abweichungen bleiben bei weniger als 300 mV nach 2300 Stunden bei +175 °C.

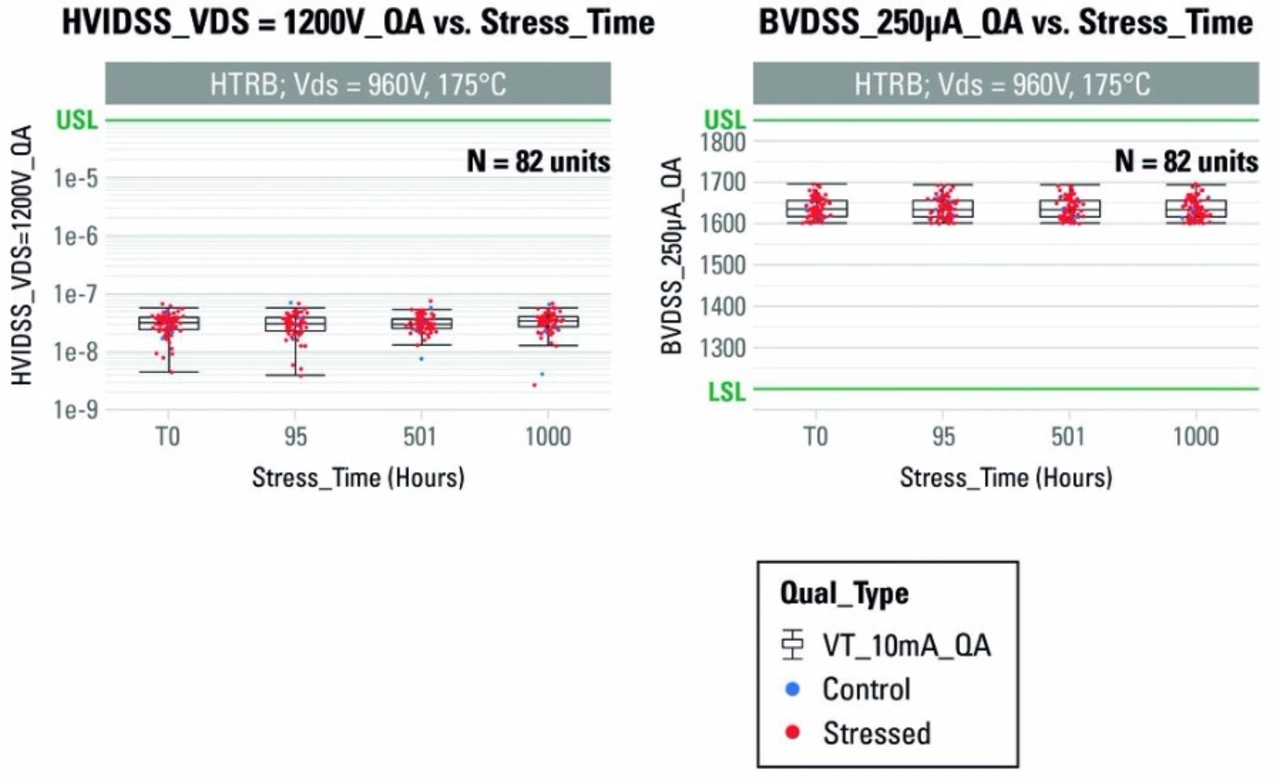

Zudem haben die SiC-MOSFETs eine vernachlässigbare Tendenz für Leckströme gezeigt, nachdem sie 1400 Stunden lang HTRB-Tests (High Temperature Reverse Bias) bei +175 °C und einer Drain-Source-Spannung UDS von 960 V sowie einer UGS von 0 V unterzogen wurden (Bild 3).

Ausblick

SiC-MOSFETs sind enorm vielversprechend für die Entwicklung kompakter Leistungswandler mit bislang unerreichter Effizienz in Solarumrichtern, Netzteilen für Rechenzentren, Ladegeräten und Antrieben für Elektrofahrzeuge und vieles mehr. Dafür müssen jedoch die Preise deutlich sinken und die Zuverlässigkeit der Bauteile konsistent nachgewiesen werden.

Techniken wie die Produktion in volumenstarken Silizium-CMOS-Fabs für 150-mm-Wafer könnten die Kosten für SiC-MOSFETs innerhalb der nächsten Jahre um 80 % reduzieren. In Kombination mit dem zunehmenden Wettbewerb verschiedener Hersteller sollten SiC-MOSFETs in Kürze preislich mit Silizium-IGBTs konkurrenzfähig und für die Volumenproduktion in der Leistungselektronik geignet sein.

Literatur

S. Banerjee et al., »Manufacturable and Rugged 1.2 KV SiC MOSFETs Fabricated in High-Volume 150mm CMOS Fab«, International Symposium on Power Semiconductor Devices & ICS, 2016, Prague, Czech Republic.

Z. Chbili et al., »Time Dependent Dielectric Breakdown in high quality SiC MOS Capacitors«, Proc. ICSCRM 2015

- SiC aus der CMOS-Fab

- SiC-MOSFET-Prozesse testen