Dritte SiC-MOSFET-Generation von Toshiba

Schalt- und Durchlassverluste deutlich gesenkt

Um 20 Prozent gegenüber der Vorgängergeneration hat Toshiba die Schalt- und Durchlassverluste der vierten Generation an SiC-MOSFETs reduzieren können. Möglich macht dies eine neue Bauelementestruktur. Noch im August 2022 soll die Serienfertigung anlaufen.

Leistungshalbleiter sind wesentliche Komponenten, um den Energiebedarf in allen Arten von elektronischen Systemen zu senken und somit einer kohlenstoffneutralen Gesellschaft zu erreichen. Siliziumkarbid (SiC) wird weithin als das Material der nächsten Generation für Leistungshalbleiter angesehen, da es höhere Spannungen zulässt und geringere Verluste als Silizium aufweist.

Derzeit kommen SiC-Leistungsbauelemente vor allem in Wechselrichtern für Züge zum Einsatz, doch eine breitere Anwendung ist absehbar, etwa bei der Elektrifizierung von Fahrzeugen und der Miniaturisierung von Industrieanlagen. Allerdings bremsen die Frage nach der Zuverlässigkeit die Akzeptanz und das Marktwachstum von SiC-Bauelementen.

Toshiba hat diese Herausforderung durch eine Struktur gelöst, bei der eine Schottky-Barrier-Diode (SBD) parallel zur parasitären PN-Diode im SiC-MOSFET der zweiten Generation angeordnet ist. Allerdings führte dies zu neuen Herausforderungen: Die Leistungskennzahlen des MOSFETs verschlechterten sich. Konkret steigen der flächenspezifische Durchlasswiderstand Ron·A und der Performance-Index Ron·QGD. Außerdem steigen die Chipkosten, weil die Chipfläche zunehmen muss, um den Durchlasswiderstand konstant zu halten.

Jobangebote+ passend zum Thema

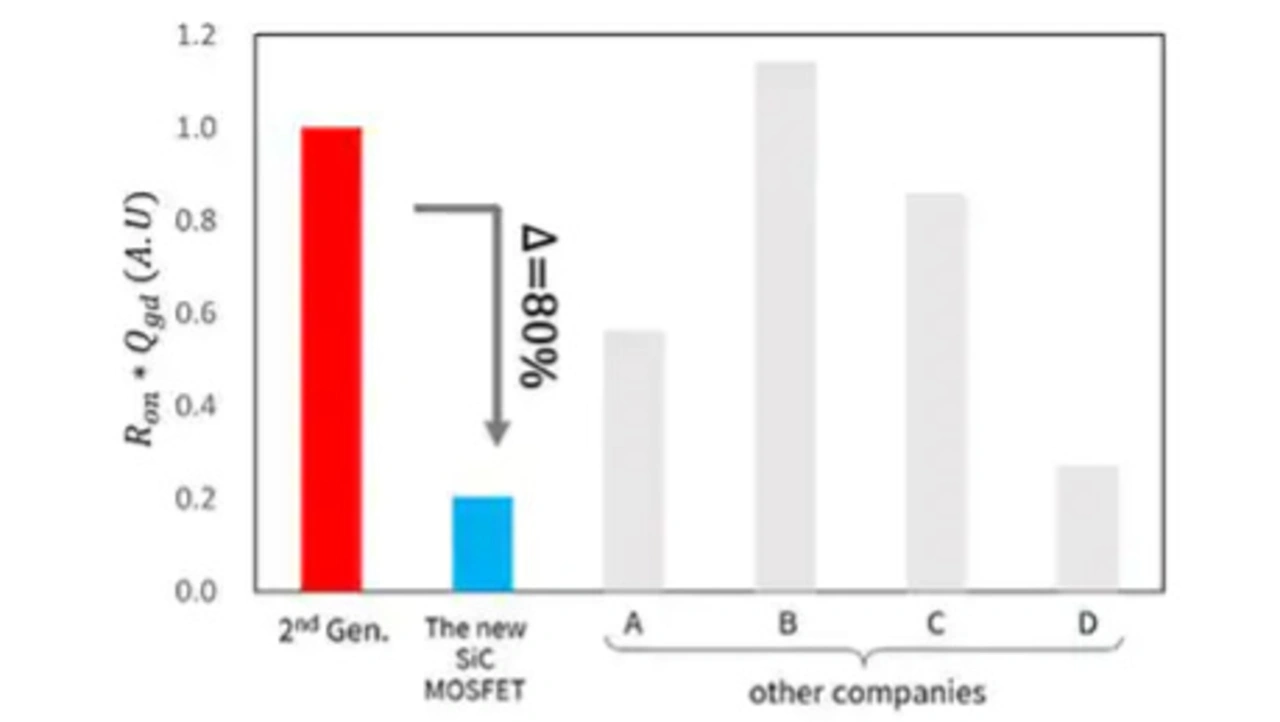

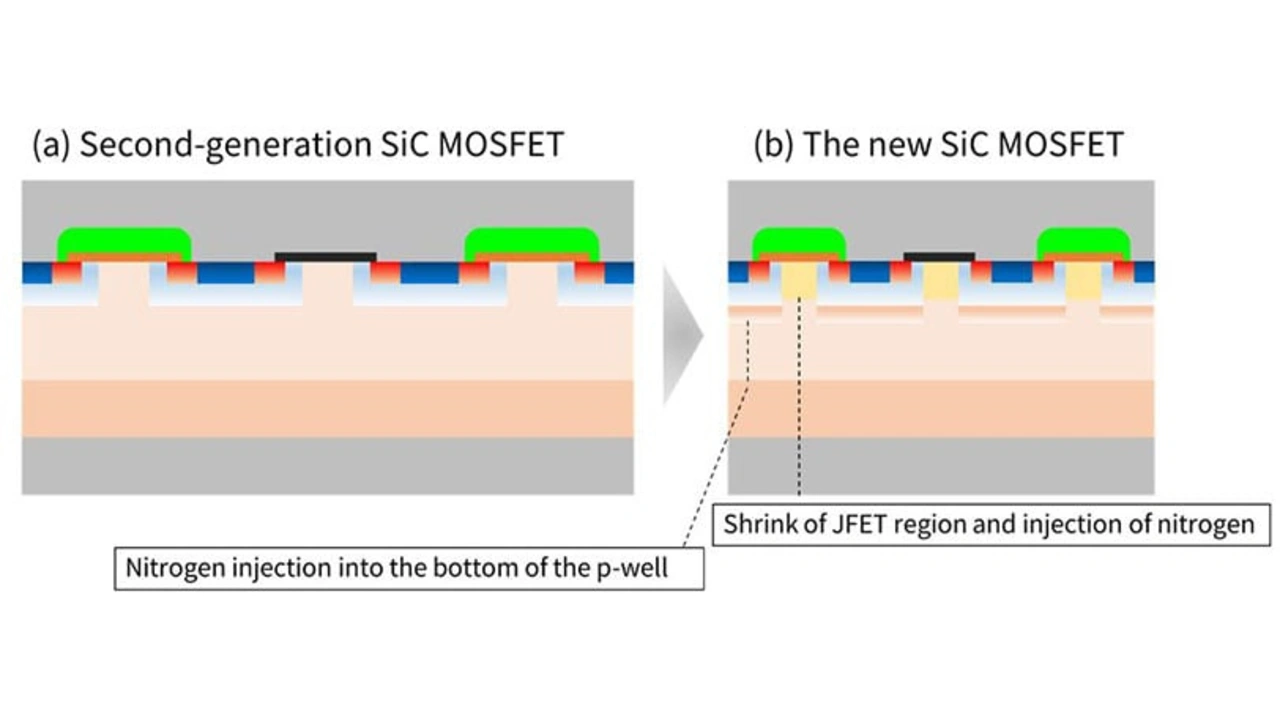

Toshiba hat nun eine Bauelementestruktur entwickelt, die den Wert von Ron·A reduziert und gleichzeitig eine Schottky-Barrier-Diode enthält (Bild 1). Durch Injizieren von Stickstoff in den unteren Teil des breiten p-Typ-Diffusionsbereichs (p-well) des SiC-MOSFETs lässt sich der Diffusionswiderstand am Boden der p-Wanne, auch Spread-Widerstand Rspread genannt, reduzieren und der Strom in der SBD erhöhen. Auch den JFET-Bereich hat Toshiba verkleinert und Stickstoff eingebracht, um die Koppelkapazität und den JFET-Widerstand zu verringern. Dadurch wurde die Koppelkapazität reduziert, ohne den flächenspezifischen Durchlasswiderstand zu erhöhen.

Bei den Prototypen für 1,2 kV lag der Ron·A um 43 Prozent (Bild 2), Ron·QGD um 80 Prozent (Bild 3) und die Schaltverluste (Ein- und Ausschalten) um etwa 20 Prozent niedriger als bei Produkten der zweiten Generation. Eine optimierte Platzierung der SBD stellt sicher, dass Ron·A nicht schwankt.