Galliumnitrid: Schnell und mit Potenzial

Licht aus dem Schatten des Siliziums

Fortsetzung des Artikels von Teil 4

Monolitisch integrierte Leistungsschaltkreise

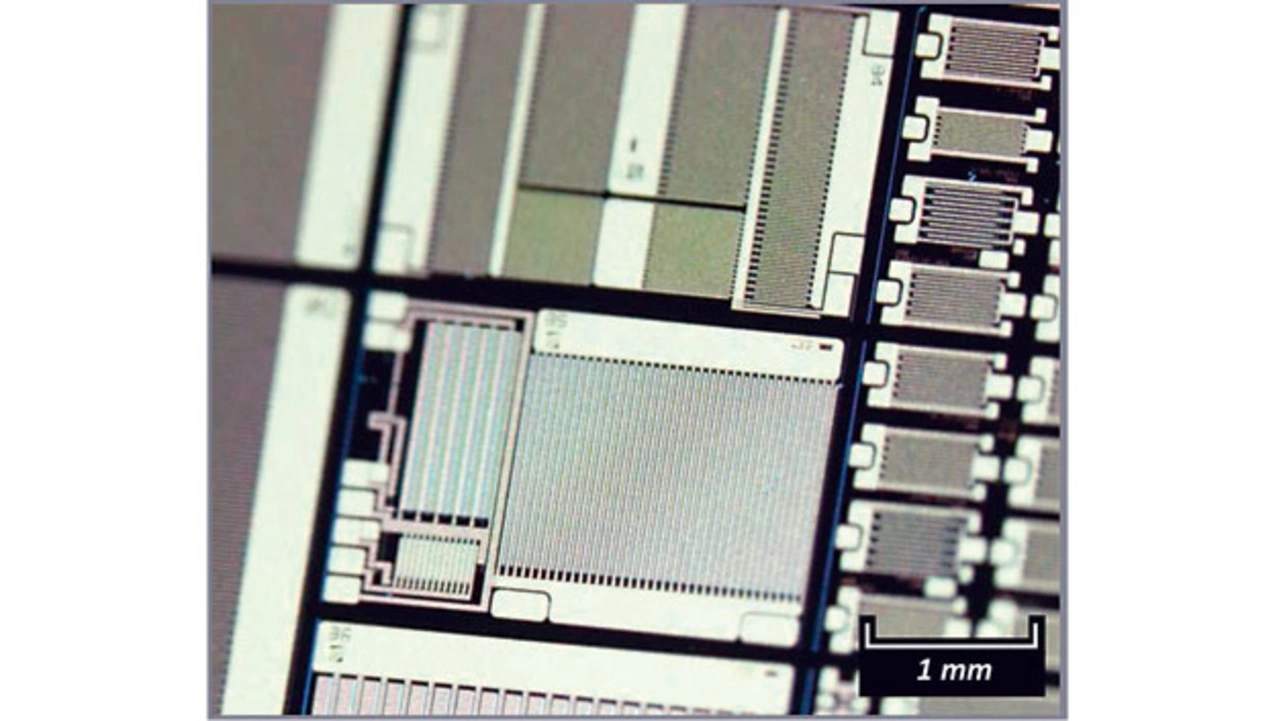

Ein aktueller Schwerpunkt der GaN-Forschung ist die monolithische Integration von mehreren Schaltungselementen auf einem GaN-Leistungs-Chip. Im Gegensatz zu den meisten konventionellen Leistungstechnologien wie Leistungs-MOSFETs oder IGBTs erlaubt die laterale GaN-auf-Si-Hetero-Junction-Technologie die Integration mehrerer Komponenten nebeneinander auf einen Chip (Bild 4). Dies können mehrere Transistoren, Dioden, Induktivitäten, Kapazitäten oder auch Sensoren sein. Im Vergleich zu Einzelbauelementen wird durch die monolithische Integration die Funktionalität und die Leistungsfähigkeit erhöht und der Aufwand für die Aufbau- und Verbindungstechnik reduziert.

Jobangebote+ passend zum Thema

Die monolithische Kointegration eines Gate-Treibers und eines Leistungs-HEMT reduziert sowohl die Gate-Schleifeninduktivität als auch die Drain-Gate-Kopplung. Damit können sehr hohe Ein- und Ausschaltflanken mit Werten von bis zu 250 V/ns erreicht werden.

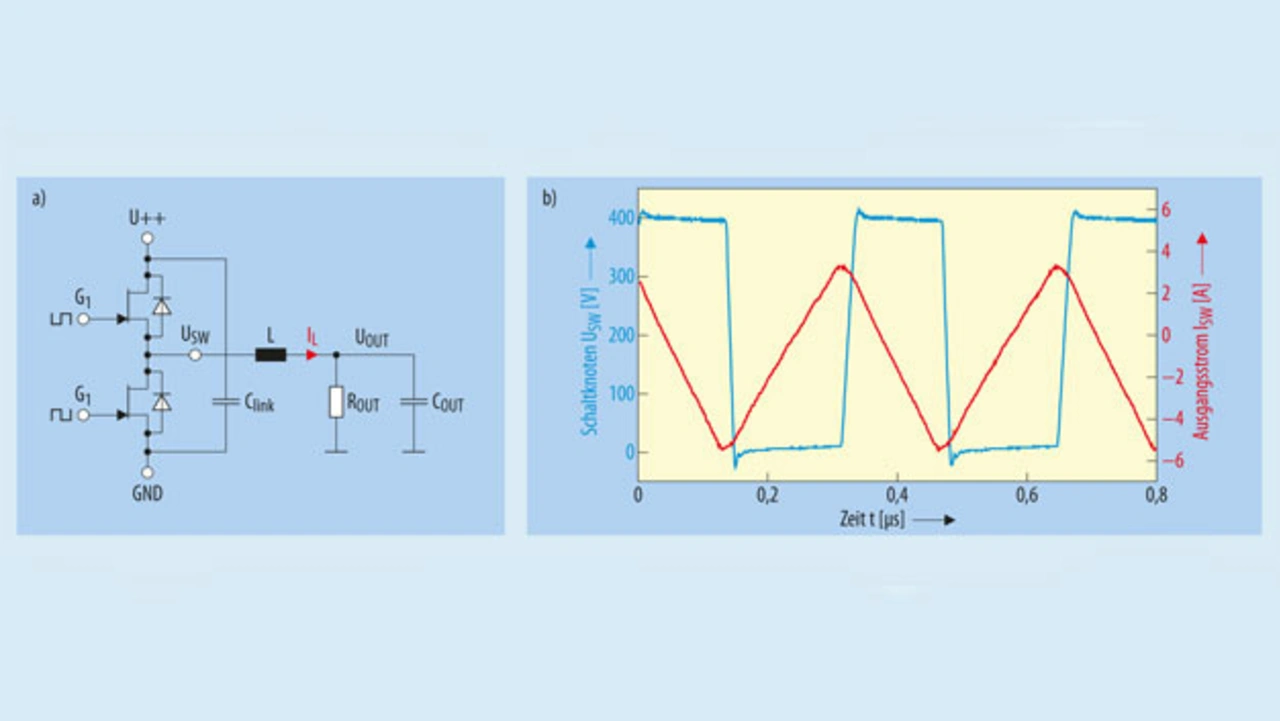

Ein weiteres Beispiel ist die Integration einer monolithischen Halbbrücke. Die integrierte Schaltung erreicht ein besseres Schaltverhalten durch reduzierte Parasitäten, eine erhöhte Zuverlässigkeit und geringere Herstellungskosten für die Aufbau- und Verbindungstechnik. Das Fraunhofer-Institut für angewandte Festkörperphysik IAF hat eine monolithisch integrierte Halbbrücke der 600-V-Klasse entwickelt. Der Betrieb wurde in einem weich schaltenden Abwärtswandler bei einer Schaltfrequenz von 3 MHz, einer Eingangsspannung von 400 V und einer Ausgangsleistung von bis zu 250 W demonstriert [3], [4], siehe Bild 5.

Kompakte Aufbautechnik „Embedding“

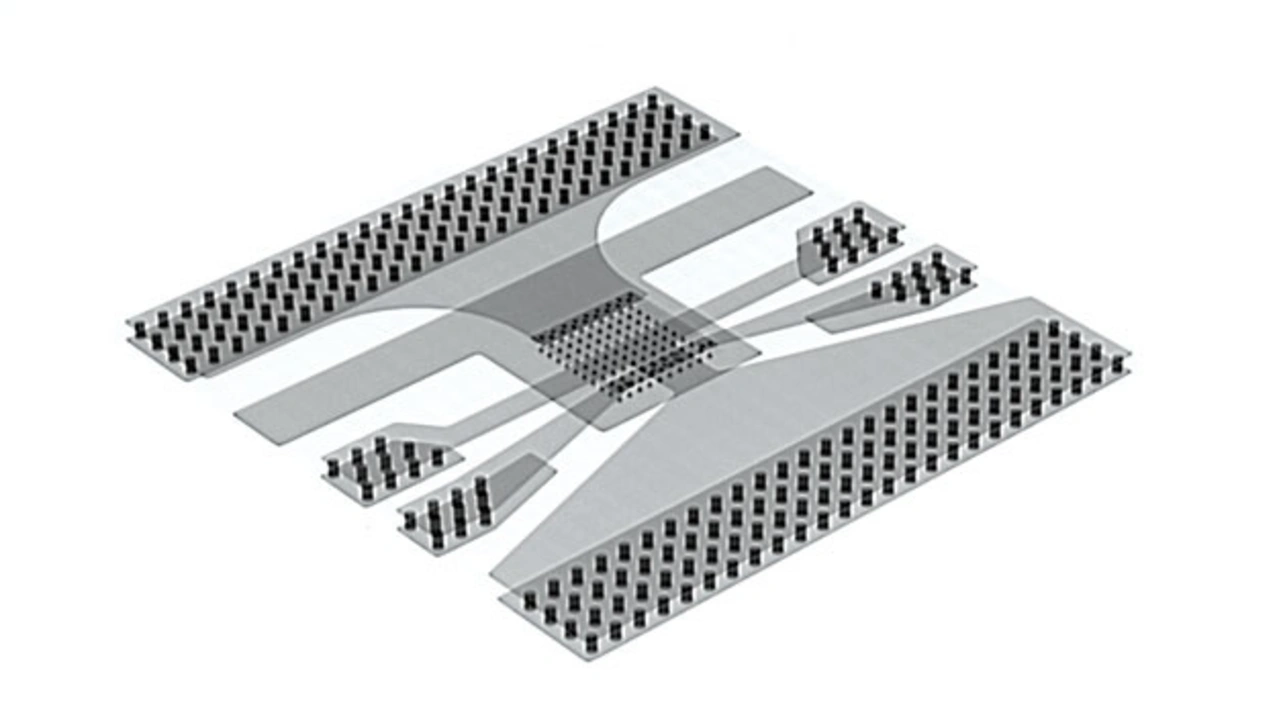

Die Aufbautechnik der schnellen Transistoren ist ebenfalls von großer Bedeutung. Der klassische Aufbau in TO220/247-Bauform ist nicht sehr sinnvoll wegen der hohen zusätzlichen parasitären Einflüsse. Das daraus erwachsende Grundproblem ist die noch fehlende Basisaufbautechnik, die von allen Herstellern akzeptiert wird, um z.B. Second Sourcing zu ermöglichen. Zur Zeit sind die Lösungen der Hersteller noch spezifisch, was den Einsatz von GaN bislang hemmt. Eine Möglichkeit, die auch industriell zu den monolithisch integrierten Leistungsschaltkreisen verfolgt wird, ist die sogenannte „Embedding Component Packaging“- (ECP) Gehäusetechnologie. Die Vorteile dieser kompakten Aufbautechnik mit hoher Funktionalität demonstriert das Fraunhofer IAF an seinem monolithisch integrierten GaN-Multilevel-Inverter, der in einer solchen AT&S-ECP-Technologie eingebettet ist (Bild 6).

- Licht aus dem Schatten des Siliziums

- Warum Galliumnitrid?

- Die Herausforderungen

- Das etwas andere Rückwärtsverhalten

- Monolitisch integrierte Leistungsschaltkreise

- Literatur