Leistungsstarkes Trench-Konzept

Die Grenzen von SiC überwinden

Fortsetzung des Artikels von Teil 1

Spannungsverlauf steuern

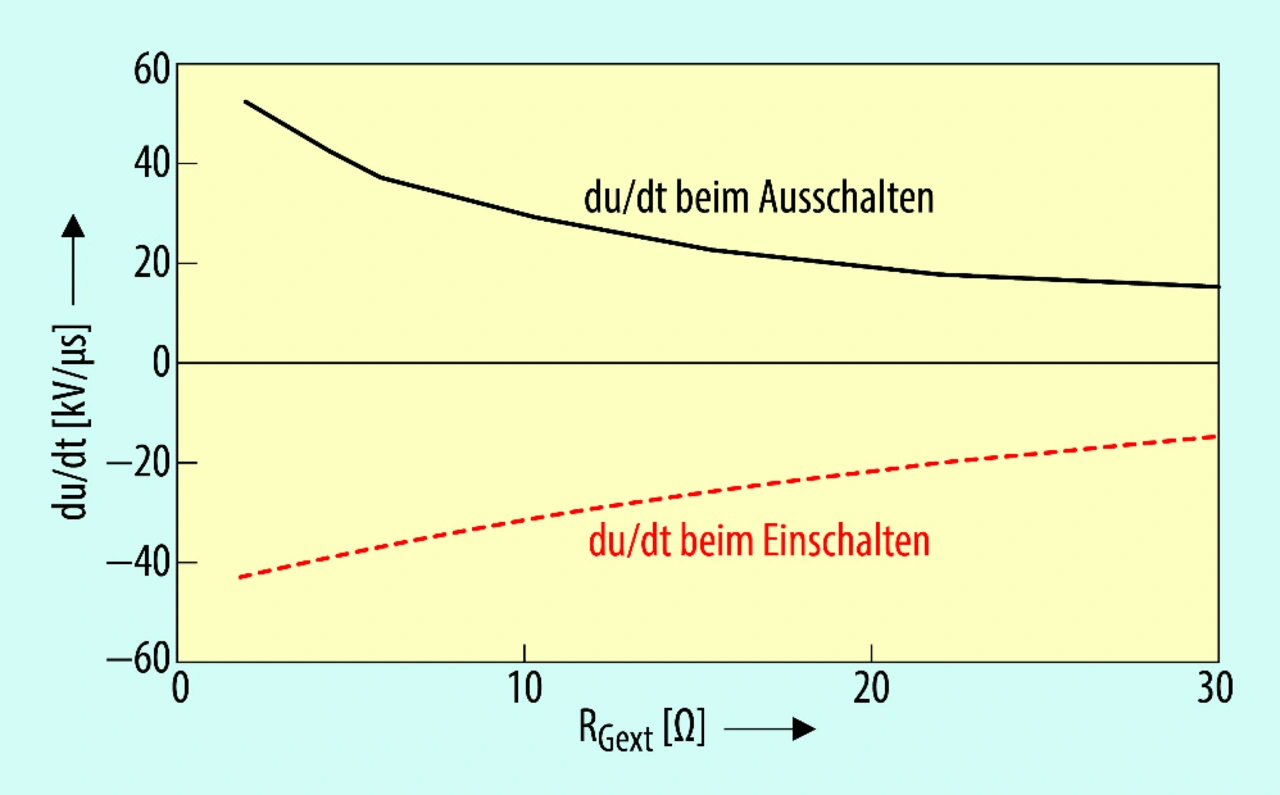

Ein wichtiges Funktionsmerkmal der neuen MOSFETs ist, dass der Spannungsverlauf beim Ein- und Ausschalten über den externen Gate-Widerstand gesteuert werden kann. Damit können alle Systemanforderungen bezüglich einer geforderten Spannungssteilheit du/dt erfüllt werden.

Jobangebote+ passend zum Thema

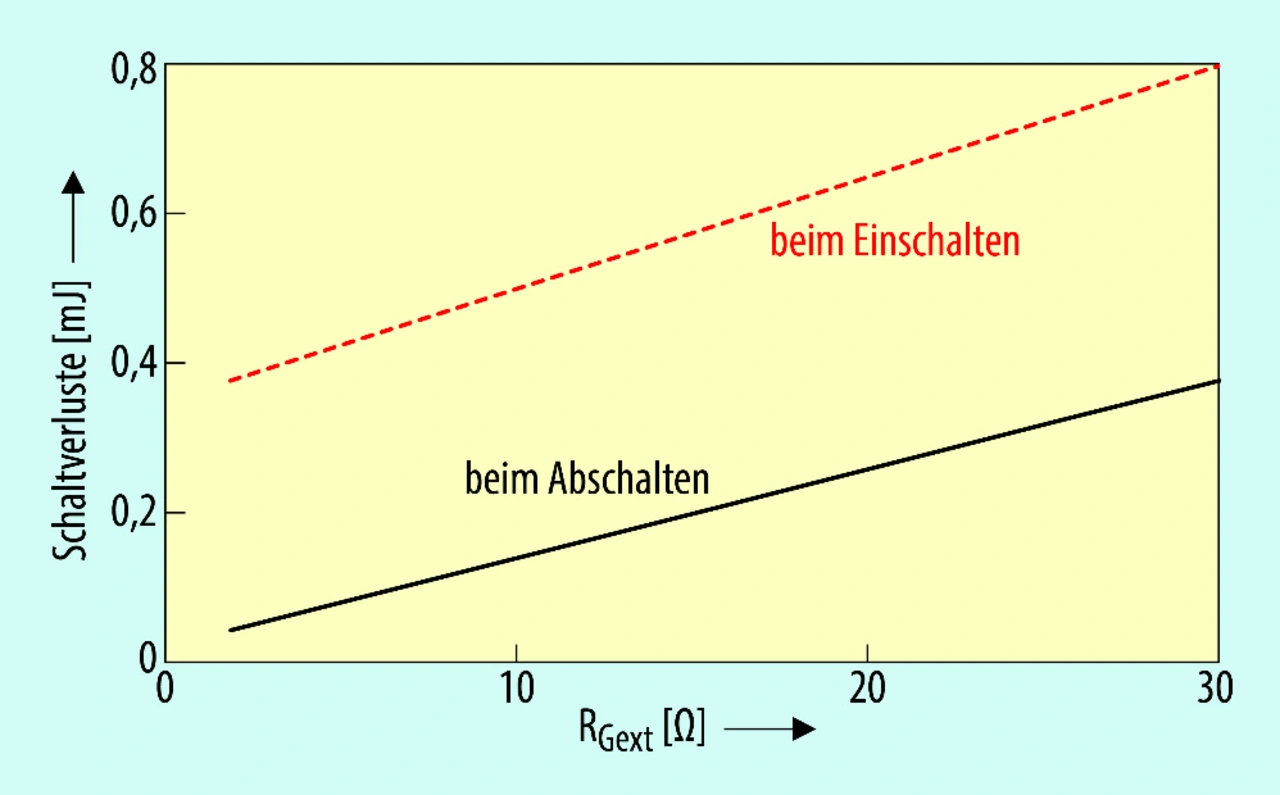

Bild 4 verdeutlicht die einfache Kontrollierbarkeit der Spannungssteilheit beim Ein- und Ausschalten mittels des externen Gate-Widerstands RGext. Die Schaltverluste sind nahezu unabhängig von der Temperatur und hängen damit nur vom Gate-Widerstand RGext ab.

Dieser Zusammenhang ist in Bild 5 dargestellt. Hier unterscheidet sich der MOSFET deutlich von IGBTs, da Minoritätsträger kaum Einfluss auf das Schaltverhalten des Bauelements nehmen.

Das dynamische Verhalten wird maßgeblich von den Kapazitäten des MOS-Systems kontrolliert, die durch den Aufbau der entsprechenden Raumladungszonen im Bauteil bestimmt sind. Die Kapazitätswerte sind unabhängig von der Temperatur des Bauelements.

In Halbbrücken-Konfiguration ist die Body-Diode aktiv und zeigt einen Einfluss auf die Verlustbilanz bei größeren Lastströmen und höheren Temperaturen. Dieser Effekt wird durch Minoritätsträger verursacht, die bei vorwärts gepoltem pn-Übergang injiziert werden und eine Speicherladung generieren.

Allerdings sind die absoluten Werte bei einem Strom von 20 A im Vergleich zu den bei bipolaren Silizium-Bauelementen auftretenden Werten sehr klein, sodass sie in der Regel nur einen geringen Einfluss auf die Gesamtverluste haben.

Extrinsische Defekte beachten

Eine der größten Bedenken beim Einsatz von SiC-MOSFETs ist die Zuverlässigkeit des Gate-Oxids im Hinblick auf sogenannte extrinsische Defekte. Ursache extrinsischer Defekte, die sich auf das Gate-Oxid von SiC-MOS-Bausteinen auswirken, sind hauptsächlich das Substrat-Material und der Epitaxie-Prozess, aber auch Defektbeiträge der restlichen Prozesskette [6].

Die Herausforderung besteht nun darin – trotz einer signifikant höheren Defektdichte im Vergleich zur etablierten Siliziumtechnologie – für die Gate-Oxid-Zuverlässigkeit der SiC-MOSFETs eine möglichst geringe Fehlerrate über die gesamte Lebensdauer unter gegebenen Betriebsbedingungen zu sichern, beispielsweise < 1 FIT in Industrieanwendungen (das entspricht einer Fehlerrate von <100 ppm in 20 Jahren).

Für die Bewertung der Zuverlässigkeit von SiC-MOSFETs wird oftmals auf Untersuchungen bei hohen Sperrspannungen (HTRB-Testbedingungen) verwiesen. Diese Vorgehensweise beschreibt jedoch nicht den primären Belastungsvorgang im realen Betrieb bzw. resultiert in zu geringen Fehlerraten aus der Extrapolation, da noch Überlagerungen mit weiteren Effekten im Halbleiter auftreten.

Daher wurden zahlreiche Bauelemente im eingeschalteten Zustand in Langzeit-Gate-Belastungstests unter realen, applikationsnahen Bedingungen untersucht.

300-Tage-Test

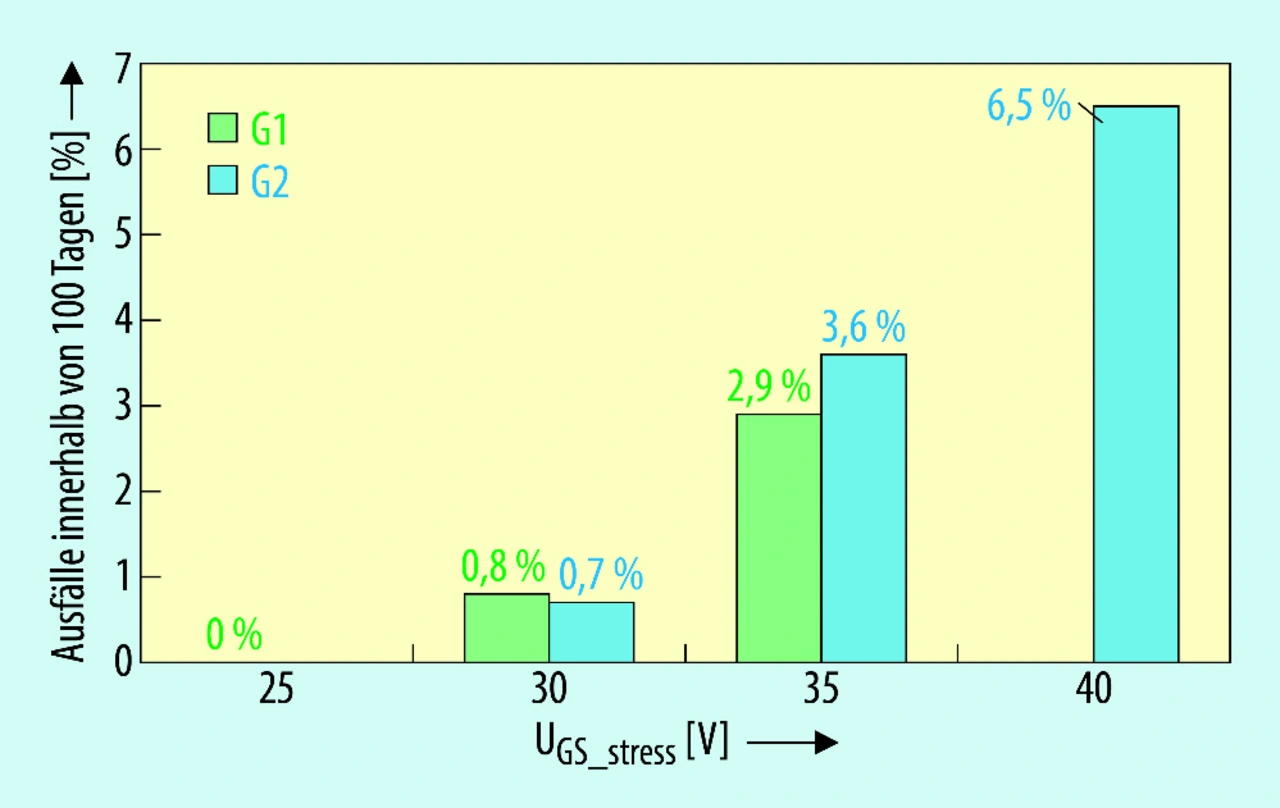

Im Rahmen der Untersuchungen wurden zwei Gruppen mit je 1000 diskreten Bauelementen getestet. Der dreistufige Test wurde bei einer Umgebungstemperatur von 150 °C mit konstanter Gate-Bias-Belastung durchgeführt.

Jede Stufe dauerte jeweils 100 Tage, danach wurde für das nächste Zeitintervall die Gate-Source-Spannung um jeweils 5 V erhöht. Jeder Ausfall wurde mit einem Zeitstempel versehen. Bild 6 zeigt die Summe der Ausfälle pro 100-Tage-Testsequenz. Im Fall der Gruppe G1 (siehe Bild 6) begann der Test mit einer Gate-Source-Spannung von +25 V und zeigte nach 100 Tagen keine Ausfälle.

Der Test an Gruppe G1 endete bei +35 V (also 20 V über der empfohlenen Gate-Source-Spannung von +15 V) mit einer Ausfallrate von insgesamt 2,9 % nach 300

Tagen. Die zweite Gruppe G2 wurde zunächst bei 30 V getestet, mit Steigerung auf 35 V und zuletzt auf 40 V. Dabei wurde eine Ausfallrate von insgesamt 6,5 % beobachtet.

Die Evaluierung ergibt, dass die Ausfallstatistik gut mit dem linearen E-Modell beschreibbar ist [7]. Extrapoliert man das Ergebnis auf eine Lebensdauer von 20 Jahren, sagt das Modell eine Ausfallrate von 0,2 ppm voraus. Das Experiment resultiert damit in einer Fehlerrate für das Gate-Oxid, die mit der eines IGBTs vergleichbar ist und unter praxisnahen Bedingungen die typischen Anforderungen im industriellen Bereich mit 1 FIT pro Chip erfüllt.

Zusätzlich wurden Hochtemperatur-Gate-Belastungstests (HTGS) durchgeführt. Sowohl Belastungstests mit positiver (Positive Bias Temperature Instability, PBTI) als auch mit negativer Gate-Spannung (Negative Bias Temperature Instability, NBTI) zeigten eine Silizium-MOSFETs entsprechende temperaturabhängige Verschiebung der Einsatzspannung ΔUGSth ~ (Zeit)n.

Bei einer Belastung über 1000 h bei 150 °C betrug die gesamte Drift der Einsatzspannung etwa +0,3 V für UGS = +20 V und -0,1 V für UGS = -10 V. Im Unterschied zu Silizium ist die durch BTI induzierte Verschiebung der Einsatzspannung bei SiC-MOSFETs überlagert von einer vollständig wiederherstellbaren Ein-/Aus-Hysterese [8].

Diese Hysterese der Einsatzspannung ist eine intrinsische Eigenschaft der SiC/SiO2-Grenzfläche und wird durch die Dynamik von schnellen Einfang- und Emissionseffekten an Grenzflächenzuständen hervorgerufen.

Die aus Anwendungssicht wichtigere permanente bzw. nur langsam relaxierende Veränderung der Einsatzspannung ist bei typischen DC-Stressbedingungen (1000 h, +20 V, 150 °C) auf einige 100 mV beschränkt.

Die darüber hinaus noch verbleibende Verschiebung der Einsatzspannung am Ende des BTI-Stresstests geht sehr wahrscheinlich auf den Ladungseinfang durch grenzflächennahe Defekte im Gate-Oxid zurück. Ladungsträger, welche an dieser Stelle eingefangen werden, reduzieren zwar nicht die Oxid-Integrität, benötigen aber mehr Zeit um wieder freigesetzt zu werden.

- Die Grenzen von SiC überwinden

- Spannungsverlauf steuern

- CoolSiC-MOSFETs - die wesentlichen Funktionalitäten