Interview mit Dr. Gerald Deboy, Infineon

CoolMOS – Hintergründe und Ausblicke einer Erfolgsstory

Fortsetzung des Artikels von Teil 1

Wie sich CoolMOS weiterentwickelt hat

Damit war Infineon – damals noch Siemens Halbleiter – der Erste.

Richtig. Wir arbeiteten damals unter Hochdruck an dieser Technologie, weil wir das Gefühl hatten, die Idee liege in der Luft – und Siemens wollte mit diesem Konzept definitiv das erste Unternehmen am Markt sein. Rückblickend haben wir aber festgestellt, dass wir auf weiter Flur allein waren. Es gab keinerlei kommerzielle Aktivitäten in dieser Richtung seitens der Wettbewerber.

Die frühesten Arbeiten in dieser Richtung datieren aus dem Jahr 1997 von Dr. Fujihira, unsere ersten Veröffentlichungen stammen aus dem Jahr 1998. Fujihira hat sich allerdings ausschließlich theoretisch mit diesem Konzept auseinandergesetzt. Nichtsdestotrotz ist das eine wichtige Schrift, denn sie beschreibt, wie Superjunction-Bauelemente überhaupt auszulegen sind, wie das laterale und das vertikale Feld zu verteilen ist und wie die Designmethodik aussehen sollte. Aber Fujihiras Ansatz hätte in der Produktion nicht funktioniert, denn bei ihm waren die p- und n-Säulen überall gleich stark dotiert. Neben ihm gab es noch Aktivitäten von Florin Udrea von der Universität Cambridge zu lateralen Superjunction-Bauelementen.

Auch Dr. Reinhard Ploss, der heutige Infineon-CEO, war damals dabei. Welchen Beitrag leistete er zu CoolMOS?

Dr. Ploss wurde 1997 Entwicklungsleiter für Leistungshalbleiterbauelemente und war von Anfang an ein Unterstützer der CoolMOS-Technologie.

Mittlerweile ist der CoolMOS fast zwanzig Jahre alt. Wie hat er sich über diese Zeit weiterentwickelt?

Uns ist es gelungen, den Einschaltwiderstand gegenüber dem Standard-Hochvolt-Transistor »BUZ 90« um den Faktor 22 zu verringern. Das ist schon gewaltig! (lacht) Außerdem haben wir das Superjunction-Prinzip immer weiter »ausgefahren«, das heißt, wir bieten den gleichen RDS(on) auf immer kleinerer Fläche. Das erreichen wir dadurch, dass wir die Strukturen immer weiter verkleinern.

Jobangebote+ passend zum Thema

Das bringt im Wesentlichen zwei Vorteile mit sich: zum einen sinken die Schaltverluste, weil der Hochspannungsanteil der Ausgangskapazität, der die Verluste beim harten Schalten bestimmt, entsprechend sinkt. Dadurch kann das Bauteil immer schneller schalten. Zum anderen wird das Bauteil dadurch immer günstiger. Und die Kosten sind ja ein wesentliches Argument für den Einsatz eines Bauteils. Wir haben festgestellt, dass es in der 600-V-Klasse keinen kostengünstigeren Weg gibt, einen gegebenen Einschaltwiderstand bei einem Leistungshalbleiter zu erreichen, als mit Superjunction. Planare Transistoren sind im Vergleich teurer, und auch die Wide-Bandgap-Bauelemente sind – Stand heute – noch nicht auf dem Preisniveau von Superjunction angelangt.

In welche Richtung lässt sich der CoolMOS noch weiterentwickeln?

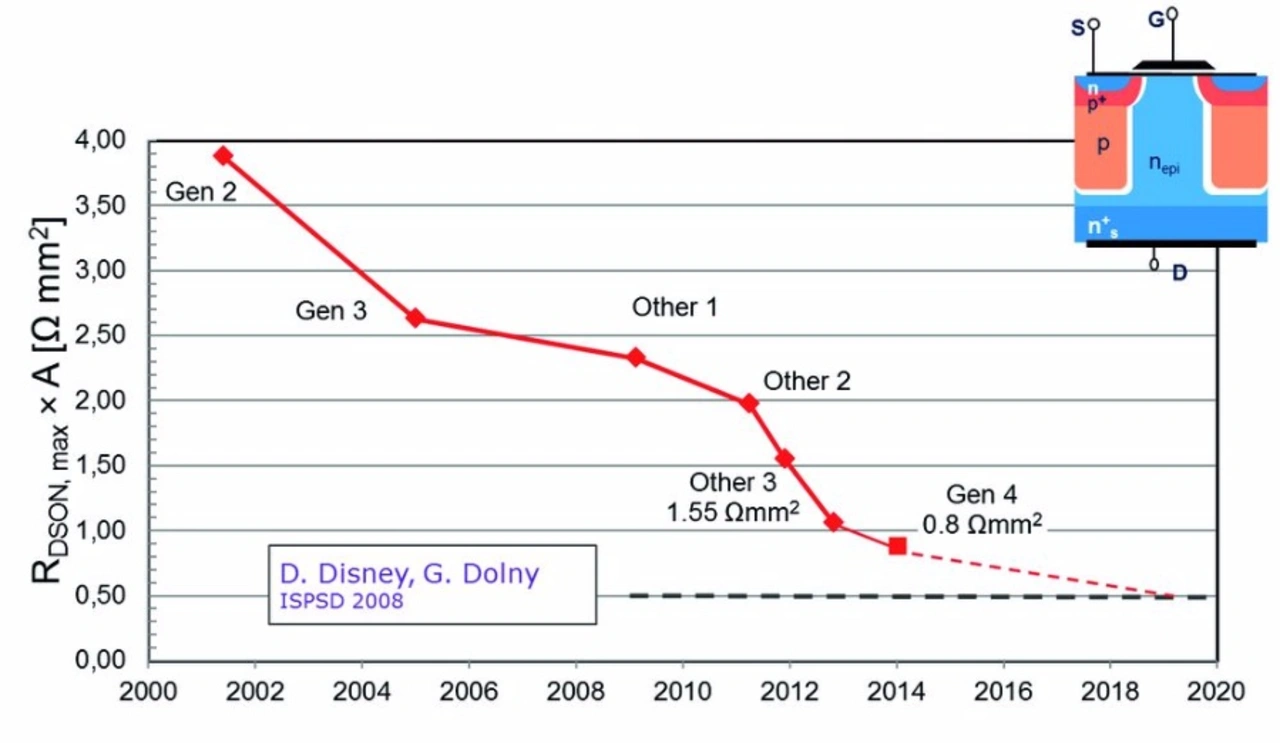

Wir stehen heute bei einem spezifischen RDS(on) von 0,8 Ω·mm². Es gibt ein Paper von der ISPSD 2008, wonach das Limit bei 0,5 Ω·mm² liegt. Wir glauben, dass dies zukünftig sicher erreichbar sein wird. Damit kommen wir dann mit Siliziumtechnik in einen Bereich, wo heutige Transistoren aus Wide-Bandgap-Materialien wie Siliziumkarbid und Galliumnitrid liegen.

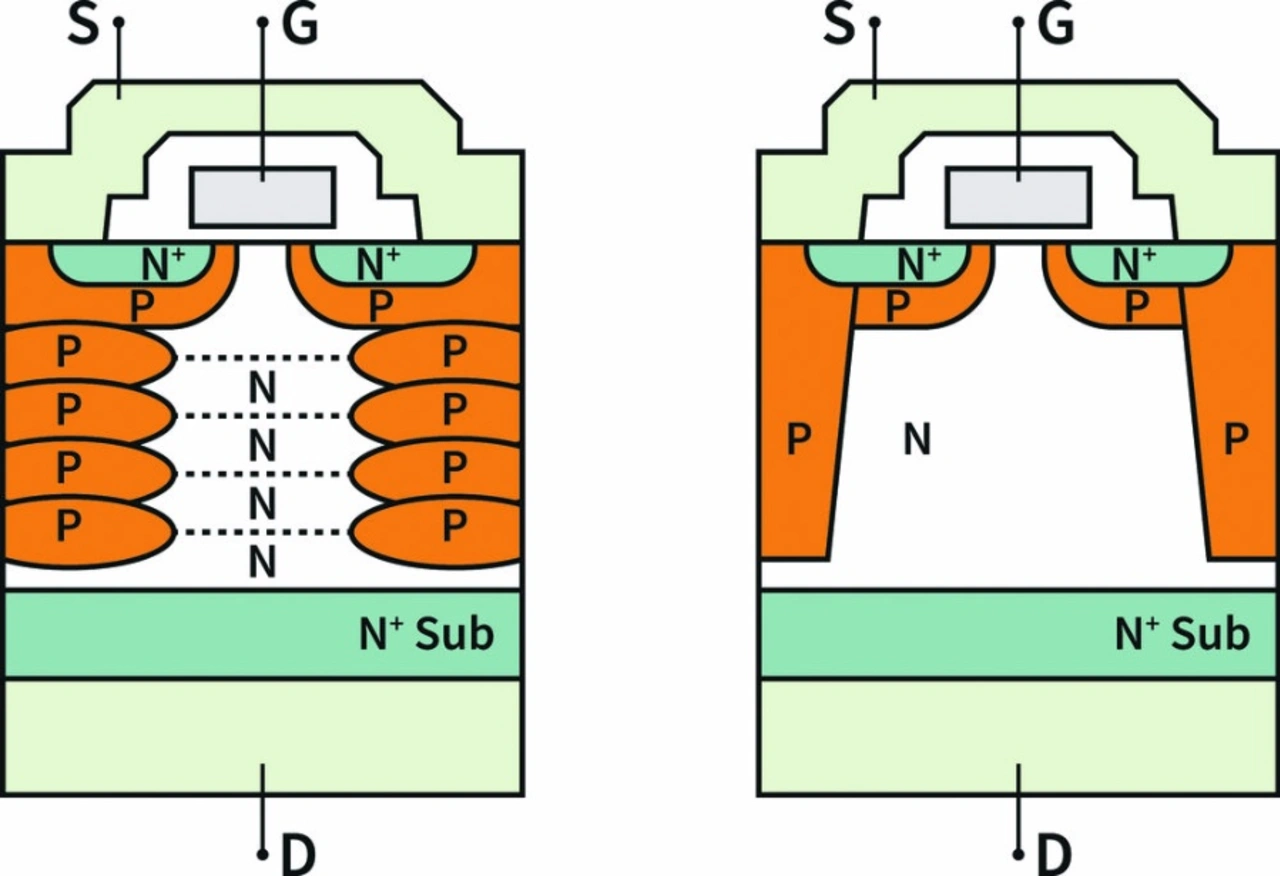

Wie Sie bereits sagten, war 1998 Infineon bzw. Siemens allein auf weiter Flur mit Superjunction. Das hat sich mittlerweile geändert. Einige Mitbewerber, besonders die Japaner, nutzen die sogenannte »Deep Trench«-Struktur und preisen diese als vorteilhafter gegenüber der konventionellen Multi-Epi-Struktur, wie sie beim CoolMOS zum Einsatz kommt. Was sagen Sie Kunden, die dieses Argument zur Sprache bringen?

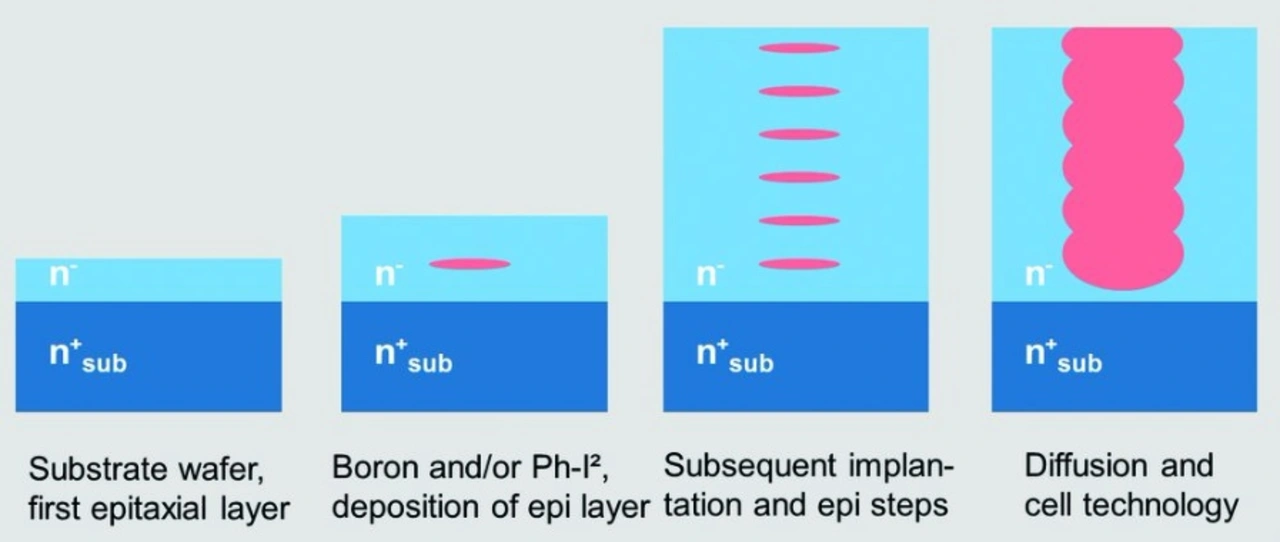

Zunächst ein paar Anmerkungen zu Technologie selber. Wenn man den Unterbau betrachtet, das heißt die spannungsaufnehmende Schicht des Transistors, die wir mit mehreren Epitaxieschichten bilden, lässt sich in jeder Ebene die Ladungsträgerkonzentration exakt einstellen. Das heißt, der Prozess beinhaltet einen sehr großen Freiraum, die p- und die n-Säulen sehr genau zu fertigen. Die Ladungsträger können auf einfache Weise dreidimensional im Halbleiter verteilt werden. Damit haben wir ein sehr präzises Werkzeug an der Hand, Bauelemente optimal auszulegen. Wird dagegen die Deep-Trench-Technologie genutzt, reduzieren sich diese Freiheitsgrade entsprechend. Die Deep-Trench-Technologie stößt deshalb schnell an Grenzen zum Beispiel hinsichtlich Avalanche-Fähigkeit und nutzbarem Fertigungsfenster. Natürlich beobachten wir bei Infineon sehr genau, welche Entwicklungen es im Markt gibt. Diese Technologie haben wir mehrfach angeschaut – und jedes Mal für uns verworfen.

Ergänzend noch ein paar Worte zur Kundensicht: Wie das Bauteil hergestellt wird, ist dem Kunden herzlich egal. Er interessiert sich für Performance – also Schalt-

eigenschaften oder erzielbarer Wirkungsgrad –, und dafür, wie leicht es sich eindesignen lässt. Ein weiteres wichtiges Kriterium ist natürlich der Preis. Mit Blick auf diese Merkmale sind wir sehr zuversichtlich, dass das Multi-Epi-Verfahren der richtige Weg ist.

- CoolMOS – Hintergründe und Ausblicke einer Erfolgsstory

- Wie sich CoolMOS weiterentwickelt hat

- Wie schneidet CoolMOS gegen SiC und GaN ab?

- Zukunft der Halbleiterei »made in Germany«